#include <sys/cdefs.h>#include <sys/param.h>#include <sys/kernel.h>#include <sys/systm.h>#include <sys/lock.h>#include <sys/mutex.h>#include <sys/sx.h>#include <sys/module.h>#include <sys/endian.h>#include <sys/types.h>#include <sys/malloc.h>#include <sys/kobj.h>#include <sys/bus.h>#include <sys/rman.h>#include <sys/socket.h>#include <sys/sockio.h>#include <sys/sysctl.h>#include <sys/smp.h>#include <sys/bitstring.h>#include <sys/limits.h>#include <sys/queue.h>#include <sys/taskqueue.h>#include <contrib/zlib/zlib.h>#include <net/debugnet.h>#include <net/if.h>#include <net/if_types.h>#include <net/if_arp.h>#include <net/ethernet.h>#include <net/if_dl.h>#include <net/if_var.h>#include <net/if_media.h>#include <net/if_vlan_var.h>#include <net/bpf.h>#include <netinet/in.h>#include <netinet/ip.h>#include <netinet/ip6.h>#include <netinet/tcp.h>#include <netinet/udp.h>#include <dev/pci/pcireg.h>#include <dev/pci/pcivar.h>#include <machine/atomic.h>#include <machine/resource.h>#include <machine/endian.h>#include <machine/bus.h>#include <machine/in_cksum.h>#include "device_if.h"#include "bus_if.h"#include "pci_if.h"#include "ecore_mfw_req.h"#include "ecore_fw_defs.h"#include "ecore_hsi.h"#include "ecore_reg.h"#include "bxe_dcb.h"#include "bxe_stats.h"#include "bxe_elink.h"#include "ecore_sp.h"

Go to the source code of this file.

Data Structures | |

| struct | bxe_device_type |

| struct | bxe_bar |

| struct | bxe_intr |

| struct | bxe_dma |

| struct | attn_route |

| struct | iro |

| union | bxe_host_hc_status_block |

| union | bxe_db_prod |

| struct | bxe_sw_tx_bd |

| struct | bxe_sw_rx_bd |

| struct | bxe_sw_tpa_info |

| struct | bxe_fastpath |

| union | cdu_context |

| struct | hw_context |

| struct | bxe_fw_stats_req |

| struct | bxe_fw_stats_data |

| struct | bxe_slowpath |

| struct | bxe_port |

| struct | bxe_mf_info |

| struct | bxe_devinfo |

| struct | bxe_sp_objs |

| struct | bxe_link_report_data |

| struct | bxe_softc |

| struct | bxe_nvram_data |

| union | bxe_stats_show_data |

| struct | bxe_func_init_params |

Macros | |

| #define | LITTLE_ENDIAN |

| #define | __LITTLE_ENDIAN |

| #define | VF_MAC_CREDIT_CNT 0 |

| #define | VF_VLAN_CREDIT_CNT (0) |

| #define | ARRSIZE(arr) (sizeof(arr) / sizeof((arr)[0])) |

| #define | DIV_ROUND_UP(n, d) (((n) + (d) - 1) / (d)) |

| #define | roundup(x, y) ((((x) + ((y) - 1)) / (y)) * (y)) |

| #define | ilog2(x) bxe_ilog2(x) |

| #define | BRCM_VENDORID 0x14e4 |

| #define | QLOGIC_VENDORID 0x1077 |

| #define | PCI_ANY_ID (uint16_t)(~0U) |

| #define | BCM_PAGE_SHIFT 12 |

| #define | BCM_PAGE_SIZE (1 << BCM_PAGE_SHIFT) |

| #define | BCM_PAGE_MASK (~(BCM_PAGE_SIZE - 1)) |

| #define | BCM_PAGE_ALIGN(addr) ((addr + BCM_PAGE_SIZE - 1) & BCM_PAGE_MASK) |

| #define | U64_LO(addr) ((uint32_t)(addr)) |

| #define | U64_HI(addr) (0) |

| #define | HILO_U64(hi, lo) ((((uint64_t)(hi)) << 32) + (lo)) |

| #define | SET_FLAG(value, mask, flag) |

| #define | GET_FLAG(value, mask) (((value) & (mask)) >> (mask##_SHIFT)) |

| #define | GET_FIELD(value, fname) (((value) & (fname##_MASK)) >> (fname##_SHIFT)) |

| #define | BXE_MAX_SEGMENTS 12 /* 13-1 for parsing buffer */ |

| #define | BXE_TSO_MAX_SEGMENTS 32 |

| #define | BXE_TSO_MAX_SIZE (65535 + sizeof(struct ether_vlan_header)) |

| #define | BXE_TSO_MAX_SEG_SIZE 4096 |

| #define | BRB_SIZE(sc) (CHIP_IS_E3(sc) ? 1024 : 512) |

| #define | MAX_AGG_QS(sc) |

| #define | FW_DROP_LEVEL(sc) (3 + MAX_SPQ_PENDING + MAX_AGG_QS(sc)) |

| #define | FW_PREFETCH_CNT 16 |

| #define | DROPLESS_FC_HEADROOM 100 |

| #define | RX_SGE_NUM_PAGES 2 /* must be a power of 2 */ |

| #define | RX_SGE_TOTAL_PER_PAGE (BCM_PAGE_SIZE / sizeof(struct eth_rx_sge)) |

| #define | RX_SGE_NEXT_PAGE_DESC_CNT 2 |

| #define | RX_SGE_USABLE_PER_PAGE (RX_SGE_TOTAL_PER_PAGE - RX_SGE_NEXT_PAGE_DESC_CNT) |

| #define | RX_SGE_PER_PAGE_MASK (RX_SGE_TOTAL_PER_PAGE - 1) |

| #define | RX_SGE_TOTAL (RX_SGE_TOTAL_PER_PAGE * RX_SGE_NUM_PAGES) |

| #define | RX_SGE_USABLE (RX_SGE_USABLE_PER_PAGE * RX_SGE_NUM_PAGES) |

| #define | RX_SGE_MAX (RX_SGE_TOTAL - 1) |

| #define | RX_SGE(x) ((x) & RX_SGE_MAX) |

| #define | RX_SGE_NEXT(x) |

| #define | RX_SGE_MASK_ELEM_SZ 64 |

| #define | RX_SGE_MASK_ELEM_SHIFT 6 |

| #define | RX_SGE_MASK_ELEM_MASK ((uint64_t)RX_SGE_MASK_ELEM_SZ - 1) |

| #define | RX_SGE_ONES_MASK(idx) (((uint64_t)0x1 << (((idx) & RX_SGE_MASK_ELEM_MASK) + 1)) - 1) |

| #define | RX_SGE_MASK_ELEM_ONE_MASK ((uint64_t)(~0)) |

| #define | RX_SGE_MASK_LEN ((RX_SGE_NUM_PAGES * RX_SGE_TOTAL_PER_PAGE) / RX_SGE_MASK_ELEM_SZ) |

| #define | RX_SGE_MASK_LEN_MASK (RX_SGE_MASK_LEN - 1) |

| #define | RX_SGE_NEXT_MASK_ELEM(el) (((el) + 1) & RX_SGE_MASK_LEN_MASK) |

| #define | NUM_SGE_REQ(sc) (MAX_AGG_QS(sc) + (BRB_SIZE(sc) - MAX_AGG_QS(sc)) / 2) |

| #define | NUM_SGE_PG_REQ(sc) ((NUM_SGE_REQ(sc) + RX_SGE_USABLE_PER_PAGE - 1) / RX_SGE_USABLE_PER_PAGE) |

| #define | SGE_TH_LO(sc) (NUM_SGE_REQ(sc) + NUM_SGE_PG_REQ(sc) * RX_SGE_NEXT_PAGE_DESC_CNT) |

| #define | SGE_TH_HI(sc) (SGE_TH_LO(sc) + DROPLESS_FC_HEADROOM) |

| #define | PAGES_PER_SGE_SHIFT 0 |

| #define | PAGES_PER_SGE (1 << PAGES_PER_SGE_SHIFT) |

| #define | SGE_PAGE_SIZE BCM_PAGE_SIZE |

| #define | SGE_PAGE_SHIFT BCM_PAGE_SHIFT |

| #define | SGE_PAGE_ALIGN(addr) BCM_PAGE_ALIGN(addr) |

| #define | SGE_PAGES (SGE_PAGE_SIZE * PAGES_PER_SGE) |

| #define | TPA_AGG_SIZE min((8 * SGE_PAGES), 0xffff) |

| #define | TX_BD_NUM_PAGES 16 /* must be a power of 2 */ |

| #define | TX_BD_TOTAL_PER_PAGE (BCM_PAGE_SIZE / sizeof(union eth_tx_bd_types)) |

| #define | TX_BD_USABLE_PER_PAGE (TX_BD_TOTAL_PER_PAGE - 1) |

| #define | TX_BD_TOTAL (TX_BD_TOTAL_PER_PAGE * TX_BD_NUM_PAGES) |

| #define | TX_BD_USABLE (TX_BD_USABLE_PER_PAGE * TX_BD_NUM_PAGES) |

| #define | TX_BD_MAX (TX_BD_TOTAL - 1) |

| #define | TX_BD_NEXT(x) |

| #define | TX_BD(x) ((x) & TX_BD_MAX) |

| #define | TX_BD_PAGE(x) (((x) & ~TX_BD_USABLE_PER_PAGE) >> 8) |

| #define | TX_BD_IDX(x) ((x) & TX_BD_USABLE_PER_PAGE) |

| #define | BXE_TX_CLEANUP_THRESHOLD (TX_BD_USABLE / 8) |

| #define | BXE_TX_TIMEOUT 5 |

| #define | RX_BD_NUM_PAGES 8 /* power of 2 */ |

| #define | RX_BD_TOTAL_PER_PAGE (BCM_PAGE_SIZE / sizeof(struct eth_rx_bd)) |

| #define | RX_BD_NEXT_PAGE_DESC_CNT 2 |

| #define | RX_BD_USABLE_PER_PAGE (RX_BD_TOTAL_PER_PAGE - RX_BD_NEXT_PAGE_DESC_CNT) |

| #define | RX_BD_PER_PAGE_MASK (RX_BD_TOTAL_PER_PAGE - 1) |

| #define | RX_BD_TOTAL (RX_BD_TOTAL_PER_PAGE * RX_BD_NUM_PAGES) |

| #define | RX_BD_USABLE (RX_BD_USABLE_PER_PAGE * RX_BD_NUM_PAGES) |

| #define | RX_BD_MAX (RX_BD_TOTAL - 1) |

| #define | RX_BD_NEXT(x) |

| #define | RX_BD(x) ((x) & RX_BD_MAX) |

| #define | RX_BD_PAGE(x) (((x) & ~RX_BD_PER_PAGE_MASK) >> 9) |

| #define | RX_BD_IDX(x) ((x) & RX_BD_PER_PAGE_MASK) |

| #define | NUM_BD_REQ(sc) BRB_SIZE(sc) |

| #define | NUM_BD_PG_REQ(sc) ((NUM_BD_REQ(sc) + RX_BD_USABLE_PER_PAGE - 1) / RX_BD_USABLE_PER_PAGE) |

| #define | BD_TH_LO(sc) |

| #define | BD_TH_HI(sc) (BD_TH_LO(sc) + DROPLESS_FC_HEADROOM) |

| #define | MIN_RX_AVAIL(sc) ((sc)->dropless_fc ? BD_TH_HI(sc) + 128 : 128) |

| #define | MIN_RX_SIZE_TPA_HW(sc) |

| #define | MIN_RX_SIZE_NONTPA_HW ETH_MIN_RX_CQES_WITHOUT_TPA |

| #define | MIN_RX_SIZE_TPA(sc) (max(MIN_RX_SIZE_TPA_HW(sc), MIN_RX_AVAIL(sc))) |

| #define | MIN_RX_SIZE_NONTPA(sc) (max(MIN_RX_SIZE_NONTPA_HW, MIN_RX_AVAIL(sc))) |

| #define | CQE_BD_REL |

| #define | RCQ_NUM_PAGES (RX_BD_NUM_PAGES * CQE_BD_REL) /* power of 2 */ |

| #define | RCQ_TOTAL_PER_PAGE (BCM_PAGE_SIZE / sizeof(union eth_rx_cqe)) |

| #define | RCQ_NEXT_PAGE_DESC_CNT 1 |

| #define | RCQ_USABLE_PER_PAGE (RCQ_TOTAL_PER_PAGE - RCQ_NEXT_PAGE_DESC_CNT) |

| #define | RCQ_TOTAL (RCQ_TOTAL_PER_PAGE * RCQ_NUM_PAGES) |

| #define | RCQ_USABLE (RCQ_USABLE_PER_PAGE * RCQ_NUM_PAGES) |

| #define | RCQ_MAX (RCQ_TOTAL - 1) |

| #define | RCQ_NEXT(x) |

| #define | RCQ(x) ((x) & RCQ_MAX) |

| #define | RCQ_PAGE(x) (((x) & ~RCQ_USABLE_PER_PAGE) >> 7) |

| #define | RCQ_IDX(x) ((x) & RCQ_USABLE_PER_PAGE) |

| #define | NUM_RCQ_REQ(sc) BRB_SIZE(sc) |

| #define | NUM_RCQ_PG_REQ(sc) ((NUM_RCQ_REQ(sc) + RCQ_USABLE_PER_PAGE - 1) / RCQ_USABLE_PER_PAGE) |

| #define | RCQ_TH_LO(sc) |

| #define | RCQ_TH_HI(sc) (RCQ_TH_LO(sc) + DROPLESS_FC_HEADROOM) |

| #define | SUB_S16(a, b) (int16_t)((int16_t)(a) - (int16_t)(b)) |

| #define | __SGE_MASK_SET_BIT(el, bit) |

| #define | __SGE_MASK_CLEAR_BIT(el, bit) |

| #define | SGE_MASK_SET_BIT(fp, idx) |

| #define | SGE_MASK_CLEAR_BIT(fp, idx) |

| #define | LOAD_NORMAL 0 |

| #define | LOAD_OPEN 1 |

| #define | LOAD_DIAG 2 |

| #define | LOAD_LOOPBACK_EXT 3 |

| #define | UNLOAD_NORMAL 0 |

| #define | UNLOAD_CLOSE 1 |

| #define | UNLOAD_RECOVERY 2 |

| #define | MAX_VNIC_NUM 4 |

| #define | MAX_FUNC_NUM 8 /* common to all chips */ |

| #define | MAX_RSS_CHAINS 16 /* a constant for HW limit */ |

| #define | MAX_MSI_VECTOR 8 /* a constant for HW limit */ |

| #define | ILT_NUM_PAGE_ENTRIES 3072 |

| #define | ILT_PER_FUNC (ILT_NUM_PAGE_ENTRIES / 8) |

| #define | FUNC_ILT_BASE(func) (func * ILT_PER_FUNC) |

| #define | ONCHIP_ADDR1(x) ((uint32_t)(((uint64_t)x >> 12) & 0xFFFFFFFF)) |

| #define | ONCHIP_ADDR2(x) ((uint32_t)((1 << 20) | ((uint64_t)x >> 44))) |

| #define | ETH_HLEN 14 |

| #define | ETH_OVERHEAD (ETH_HLEN + 8 + 8) |

| #define | ETH_MIN_PACKET_SIZE 60 |

| #define | ETH_MAX_PACKET_SIZE ETHERMTU /* 1500 */ |

| #define | ETH_MAX_JUMBO_PACKET_SIZE 9600 |

| #define | ETH_MAX_TPA_HEADER_SIZE 72 |

| #define | BXE_RX_ALIGN_SHIFT 8 |

| #define | BXE_FW_RX_ALIGN_START (1 << BXE_RX_ALIGN_SHIFT) |

| #define | BXE_FW_RX_ALIGN_END (1 << BXE_RX_ALIGN_SHIFT) |

| #define | BXE_PXP_DRAM_ALIGN (BXE_RX_ALIGN_SHIFT - 5) /* XXX ??? */ |

| #define | BXE_SET_ERROR_BIT(sc, error) |

| #define | MAX_DYNAMIC_ATTN_GRPS 8 |

| #define | BXE_TSO_SPLIT_BD (1 << 0) |

| #define | BXE_TPA_STATE_START 1 |

| #define | BXE_TPA_STATE_STOP 2 |

| #define | BXE_FP_TX_LOCK(fp) mtx_lock(&fp->tx_mtx) |

| #define | BXE_FP_TX_UNLOCK(fp) mtx_unlock(&fp->tx_mtx) |

| #define | BXE_FP_TX_LOCK_ASSERT(fp) mtx_assert(&fp->tx_mtx, MA_OWNED) |

| #define | BXE_FP_TX_TRYLOCK(fp) mtx_trylock(&fp->tx_mtx) |

| #define | BXE_FP_RX_LOCK(fp) mtx_lock(&fp->rx_mtx) |

| #define | BXE_FP_RX_UNLOCK(fp) mtx_unlock(&fp->rx_mtx) |

| #define | BXE_FP_RX_LOCK_ASSERT(fp) mtx_assert(&fp->rx_mtx, MA_OWNED) |

| #define | BXE_FP_STATE_CLOSED 0x01 |

| #define | BXE_FP_STATE_IRQ 0x02 |

| #define | BXE_FP_STATE_OPENING 0x04 |

| #define | BXE_FP_STATE_OPEN 0x08 |

| #define | BXE_FP_STATE_HALTING 0x10 |

| #define | BXE_FP_STATE_HALTED 0x20 |

| #define | FP_IDX(fp) (fp->index) |

| #define | FP_CL_ID(fp) (fp->cl_id) |

| #define | BXE_BR_SIZE 4096 |

| #define | BXE_MAX_NUM_OF_VFS 64 |

| #define | BXE_VF_CID_WND 0 |

| #define | BXE_CIDS_PER_VF (1 << BXE_VF_CID_WND) |

| #define | BXE_CLIENTS_PER_VF 1 |

| #define | BXE_FIRST_VF_CID 256 |

| #define | BXE_VF_CIDS (BXE_MAX_NUM_OF_VFS * BXE_CIDS_PER_VF) |

| #define | BXE_VF_ID_INVALID 0xFF |

| #define | IS_SRIOV(sc) 0 |

| #define | GET_NUM_VFS_PER_PATH(sc) 0 |

| #define | GET_NUM_VFS_PER_PF(sc) 0 |

| #define | FP_SB_MAX_E1x 16 |

| #define | FP_SB_MAX_E2 HC_SB_MAX_SB_E2 |

| #define | CDU_ILT_PAGE_SZ_HW 2 |

| #define | CDU_ILT_PAGE_SZ (8192 << CDU_ILT_PAGE_SZ_HW) /* 32K */ |

| #define | ILT_PAGE_CIDS (CDU_ILT_PAGE_SZ / sizeof(union cdu_context)) |

| #define | CNIC_ISCSI_CID_MAX 256 |

| #define | CNIC_FCOE_CID_MAX 2048 |

| #define | CNIC_CID_MAX (CNIC_ISCSI_CID_MAX + CNIC_FCOE_CID_MAX) |

| #define | CNIC_ILT_LINES DIV_ROUND_UP(CNIC_CID_MAX, ILT_PAGE_CIDS) |

| #define | QM_ILT_PAGE_SZ_HW 0 |

| #define | QM_ILT_PAGE_SZ (4096 << QM_ILT_PAGE_SZ_HW) /* 4K */ |

| #define | QM_CID_ROUND 1024 |

| #define | TM_ILT_PAGE_SZ_HW 0 |

| #define | TM_ILT_PAGE_SZ (4096 << TM_ILT_PAGE_SZ_HW) /* 4K */ |

| #define | TM_CONN_NUM 1024 |

| #define | TM_ILT_SZ (8 * TM_CONN_NUM) |

| #define | TM_ILT_LINES DIV_ROUND_UP(TM_ILT_SZ, TM_ILT_PAGE_SZ) |

| #define | SRC_ILT_PAGE_SZ_HW 0 |

| #define | SRC_ILT_PAGE_SZ (4096 << SRC_ILT_PAGE_SZ_HW) /* 4K */ |

| #define | SRC_HASH_BITS 10 |

| #define | SRC_CONN_NUM (1 << SRC_HASH_BITS) /* 1024 */ |

| #define | SRC_ILT_SZ (sizeof(struct src_ent) * SRC_CONN_NUM) |

| #define | SRC_T2_SZ SRC_ILT_SZ |

| #define | SRC_ILT_LINES DIV_ROUND_UP(SRC_ILT_SZ, SRC_ILT_PAGE_SZ) |

| #define | SM_RX_ID 0 |

| #define | SM_TX_ID 1 |

| #define | FIRST_TX_ONLY_COS_INDEX 1 |

| #define | FIRST_TX_COS_INDEX 0 |

| #define | CID_TO_FP(cid, sc) ((cid) % BXE_NUM_NON_CNIC_QUEUES(sc)) |

| #define | HC_INDEX_ETH_RX_CQ_CONS 1 |

| #define | HC_INDEX_OOO_TX_CQ_CONS 4 |

| #define | HC_INDEX_ETH_TX_CQ_CONS_COS0 5 |

| #define | HC_INDEX_ETH_TX_CQ_CONS_COS1 6 |

| #define | HC_INDEX_ETH_TX_CQ_CONS_COS2 7 |

| #define | HC_INDEX_ETH_FIRST_TX_CQ_CONS HC_INDEX_ETH_TX_CQ_CONS_COS0 |

| #define | CMNG_FNS_NONE 0 |

| #define | CMNG_FNS_MINMAX 1 |

| #define | DEF_MIN_RATE 100 |

| #define | RS_PERIODIC_TIMEOUT_USEC 400 |

| #define | QM_ARB_BYTES 160000 |

| #define | MIN_RES 100 |

| #define | MIN_ABOVE_THRESH 32768 |

| #define | T_FAIR_COEF ((MIN_ABOVE_THRESH + QM_ARB_BYTES) * 8 * MIN_RES) |

| #define | FAIR_MEM 2 |

| #define | HC_SEG_ACCESS_DEF 0 /* Driver decision 0-3 */ |

| #define | HC_SEG_ACCESS_ATTN 4 |

| #define | HC_SEG_ACCESS_NORM 0 /* Driver decision 0-1 */ |

| #define | BXE_NUM_QUEUES(sc) ((sc)->num_queues) |

| #define | BXE_NUM_ETH_QUEUES(sc) BXE_NUM_QUEUES(sc) |

| #define | BXE_NUM_NON_CNIC_QUEUES(sc) BXE_NUM_QUEUES(sc) |

| #define | BXE_NUM_RX_QUEUES(sc) BXE_NUM_QUEUES(sc) |

| #define | FOR_EACH_QUEUE(sc, var) for ((var) = 0; (var) < BXE_NUM_QUEUES(sc); (var)++) |

| #define | FOR_EACH_NONDEFAULT_QUEUE(sc, var) for ((var) = 1; (var) < BXE_NUM_QUEUES(sc); (var)++) |

| #define | FOR_EACH_ETH_QUEUE(sc, var) for ((var) = 0; (var) < BXE_NUM_ETH_QUEUES(sc); (var)++) |

| #define | FOR_EACH_NONDEFAULT_ETH_QUEUE(sc, var) for ((var) = 1; (var) < BXE_NUM_ETH_QUEUES(sc); (var)++) |

| #define | FOR_EACH_COS_IN_TX_QUEUE(sc, var) for ((var) = 0; (var) < (sc)->max_cos; (var)++) |

| #define | FOR_EACH_CNIC_QUEUE(sc, var) |

| #define | FCOE_IDX(sc) (BXE_NUM_NON_CNIC_QUEUES(sc) + FCOE_IDX_OFFSET) |

| #define | bxe_fcoe_fp(sc) (&sc->fp[FCOE_IDX(sc)]) |

| #define | bxe_fcoe(sc, var) (bxe_fcoe_fp(sc)->var) |

| #define | bxe_fcoe_inner_sp_obj(sc) (&sc->sp_objs[FCOE_IDX(sc)]) |

| #define | bxe_fcoe_sp_obj(sc, var) (bxe_fcoe_inner_sp_obj(sc)->var) |

| #define | bxe_fcoe_tx(sc, var) (bxe_fcoe_fp(sc)->txdata_ptr[FIRST_TX_COS_INDEX]->var) |

| #define | OOO_IDX(sc) (BXE_NUM_NON_CNIC_QUEUES(sc) + OOO_IDX_OFFSET) |

| #define | bxe_ooo_fp(sc) (&sc->fp[OOO_IDX(sc)]) |

| #define | bxe_ooo(sc, var) (bxe_ooo_fp(sc)->var) |

| #define | bxe_ooo_inner_sp_obj(sc) (&sc->sp_objs[OOO_IDX(sc)]) |

| #define | bxe_ooo_sp_obj(sc, var) (bxe_ooo_inner_sp_obj(sc)->var) |

| #define | FWD_IDX(sc) (BXE_NUM_NON_CNIC_QUEUES(sc) + FWD_IDX_OFFSET) |

| #define | bxe_fwd_fp(sc) (&sc->fp[FWD_IDX(sc)]) |

| #define | bxe_fwd(sc, var) (bxe_fwd_fp(sc)->var) |

| #define | bxe_fwd_inner_sp_obj(sc) (&sc->sp_objs[FWD_IDX(sc)]) |

| #define | bxe_fwd_sp_obj(sc, var) (bxe_fwd_inner_sp_obj(sc)->var) |

| #define | bxe_fwd_txdata(fp) (fp->txdata_ptr[FIRST_TX_COS_INDEX]) |

| #define | IS_ETH_FP(fp) ((fp)->index < BXE_NUM_ETH_QUEUES((fp)->sc)) |

| #define | IS_FCOE_FP(fp) ((fp)->index == FCOE_IDX((fp)->sc)) |

| #define | IS_FCOE_IDX(idx) ((idx) == FCOE_IDX(sc)) |

| #define | IS_FWD_FP(fp) ((fp)->index == FWD_IDX((fp)->sc)) |

| #define | IS_FWD_IDX(idx) ((idx) == FWD_IDX(sc)) |

| #define | IS_OOO_FP(fp) ((fp)->index == OOO_IDX((fp)->sc)) |

| #define | IS_OOO_IDX(idx) ((idx) == OOO_IDX(sc)) |

| #define | BXE_IGU_STAS_MSG_VF_CNT 64 |

| #define | BXE_IGU_STAS_MSG_PF_CNT 4 |

| #define | MAX_DMAE_C 8 |

| #define | BXE_CORE_LOCK_SX |

| #define | ADVERTISED_10baseT_Half (1 << 1) |

| #define | ADVERTISED_10baseT_Full (1 << 2) |

| #define | ADVERTISED_100baseT_Half (1 << 3) |

| #define | ADVERTISED_100baseT_Full (1 << 4) |

| #define | ADVERTISED_1000baseT_Half (1 << 5) |

| #define | ADVERTISED_1000baseT_Full (1 << 6) |

| #define | ADVERTISED_TP (1 << 7) |

| #define | ADVERTISED_FIBRE (1 << 8) |

| #define | ADVERTISED_Autoneg (1 << 9) |

| #define | ADVERTISED_Asym_Pause (1 << 10) |

| #define | ADVERTISED_Pause (1 << 11) |

| #define | ADVERTISED_2500baseX_Full (1 << 15) |

| #define | ADVERTISED_10000baseT_Full (1 << 16) |

| #define | BXE_PHY_LOCK(sc) mtx_lock(&sc->port.phy_mtx) |

| #define | BXE_PHY_UNLOCK(sc) mtx_unlock(&sc->port.phy_mtx) |

| #define | BXE_PHY_LOCK_ASSERT(sc) mtx_assert(&sc->port.phy_mtx, MA_OWNED) |

| #define | IS_MULTI_VNIC(sc) ((sc)->devinfo.mf_info.multi_vnics_mode) |

| #define | VNICS_PER_PORT(sc) ((sc)->devinfo.mf_info.vnics_per_port) |

| #define | VNICS_PER_PATH(sc) |

| #define | VALID_OVLAN(ovlan) ((ovlan) <= 4096) |

| #define | INVALID_VIF_ID 0xFFFF |

| #define | OVLAN(sc) ((sc)->devinfo.mf_info.ext_id) |

| #define | VIF_ID(sc) ((sc)->devinfo.mf_info.ext_id) |

| #define | NIV_DEFAULT_VLAN(sc) ((sc)->devinfo.mf_info.default_vlan) |

| #define | NIV_ALLOWED_PRIORITIES(sc) ((sc)->devinfo.mf_info.niv_allowed_priorities) |

| #define | NIV_DEFAULT_COS(sc) ((sc)->devinfo.mf_info.niv_default_cos) |

| #define | AFEX_VLAN_MODE(sc) ((sc)->devinfo.mf_info.afex_vlan_mode) |

| #define | MF_INFO_VALID_MAC 0x0001 |

| #define | IS_MF(sc) |

| #define | IS_MF_SD(sc) |

| #define | IS_MF_SI(sc) |

| #define | IS_MF_AFEX(sc) |

| #define | IS_MF_SD_MODE(sc) IS_MF_SD(sc) |

| #define | IS_MF_SI_MODE(sc) IS_MF_SI(sc) |

| #define | IS_MF_AFEX_MODE(sc) IS_MF_AFEX(sc) |

| #define | MF_PROTO_SUPPORT_ETHERNET 0x1 |

| #define | MF_PROTO_SUPPORT_ISCSI 0x2 |

| #define | MF_PROTO_SUPPORT_FCOE 0x4 |

| #define | CHIP_ID(sc) ((sc)->devinfo.chip_id & 0xffff0000) |

| #define | CHIP_NUM(sc) ((sc)->devinfo.chip_id >> 16) |

| #define | CHIP_NUM_57710 0x164e |

| #define | CHIP_NUM_57711 0x164f |

| #define | CHIP_NUM_57711E 0x1650 |

| #define | CHIP_NUM_57712 0x1662 |

| #define | CHIP_NUM_57712_MF 0x1663 |

| #define | CHIP_NUM_57712_VF 0x166f |

| #define | CHIP_NUM_57800 0x168a |

| #define | CHIP_NUM_57800_MF 0x16a5 |

| #define | CHIP_NUM_57800_VF 0x16a9 |

| #define | CHIP_NUM_57810 0x168e |

| #define | CHIP_NUM_57810_MF 0x16ae |

| #define | CHIP_NUM_57810_VF 0x16af |

| #define | CHIP_NUM_57811 0x163d |

| #define | CHIP_NUM_57811_MF 0x163e |

| #define | CHIP_NUM_57811_VF 0x163f |

| #define | CHIP_NUM_57840_OBS 0x168d |

| #define | CHIP_NUM_57840_OBS_MF 0x16ab |

| #define | CHIP_NUM_57840_4_10 0x16a1 |

| #define | CHIP_NUM_57840_2_20 0x16a2 |

| #define | CHIP_NUM_57840_MF 0x16a4 |

| #define | CHIP_NUM_57840_VF 0x16ad |

| #define | CHIP_REV_SHIFT 12 |

| #define | CHIP_REV_MASK (0xF << CHIP_REV_SHIFT) |

| #define | CHIP_REV(sc) ((sc)->devinfo.chip_id & CHIP_REV_MASK) |

| #define | CHIP_REV_Ax (0x0 << CHIP_REV_SHIFT) |

| #define | CHIP_REV_Bx (0x1 << CHIP_REV_SHIFT) |

| #define | CHIP_REV_Cx (0x2 << CHIP_REV_SHIFT) |

| #define | CHIP_REV_IS_SLOW(sc) (CHIP_REV(sc) > 0x00005000) |

| #define | CHIP_REV_IS_FPGA(sc) (CHIP_REV_IS_SLOW(sc) && (CHIP_REV(sc) & 0x00001000)) |

| #define | CHIP_REV_IS_EMUL(sc) (CHIP_REV_IS_SLOW(sc) && !(CHIP_REV(sc) & 0x00001000)) |

| #define | CHIP_REV_IS_ASIC(sc) (!CHIP_REV_IS_SLOW(sc)) |

| #define | CHIP_METAL(sc) ((sc->devinfo.chip_id) & 0x00000ff0) |

| #define | CHIP_BOND_ID(sc) ((sc->devinfo.chip_id) & 0x0000000f) |

| #define | CHIP_IS_E1(sc) (CHIP_NUM(sc) == CHIP_NUM_57710) |

| #define | CHIP_IS_57710(sc) (CHIP_NUM(sc) == CHIP_NUM_57710) |

| #define | CHIP_IS_57711(sc) (CHIP_NUM(sc) == CHIP_NUM_57711) |

| #define | CHIP_IS_57711E(sc) (CHIP_NUM(sc) == CHIP_NUM_57711E) |

| #define | CHIP_IS_E1H(sc) |

| #define | CHIP_IS_E1x(sc) |

| #define | CHIP_IS_57712(sc) (CHIP_NUM(sc) == CHIP_NUM_57712) |

| #define | CHIP_IS_57712_MF(sc) (CHIP_NUM(sc) == CHIP_NUM_57712_MF) |

| #define | CHIP_IS_57712_VF(sc) (CHIP_NUM(sc) == CHIP_NUM_57712_VF) |

| #define | CHIP_IS_E2(sc) |

| #define | CHIP_IS_57800(sc) (CHIP_NUM(sc) == CHIP_NUM_57800) |

| #define | CHIP_IS_57800_MF(sc) (CHIP_NUM(sc) == CHIP_NUM_57800_MF) |

| #define | CHIP_IS_57800_VF(sc) (CHIP_NUM(sc) == CHIP_NUM_57800_VF) |

| #define | CHIP_IS_57810(sc) (CHIP_NUM(sc) == CHIP_NUM_57810) |

| #define | CHIP_IS_57810_MF(sc) (CHIP_NUM(sc) == CHIP_NUM_57810_MF) |

| #define | CHIP_IS_57810_VF(sc) (CHIP_NUM(sc) == CHIP_NUM_57810_VF) |

| #define | CHIP_IS_57811(sc) (CHIP_NUM(sc) == CHIP_NUM_57811) |

| #define | CHIP_IS_57811_MF(sc) (CHIP_NUM(sc) == CHIP_NUM_57811_MF) |

| #define | CHIP_IS_57811_VF(sc) (CHIP_NUM(sc) == CHIP_NUM_57811_VF) |

| #define | CHIP_IS_57840(sc) |

| #define | CHIP_IS_57840_MF(sc) |

| #define | CHIP_IS_57840_VF(sc) (CHIP_NUM(sc) == CHIP_NUM_57840_VF) |

| #define | CHIP_IS_E3(sc) |

| #define | CHIP_IS_E3A0(sc) |

| #define | CHIP_IS_E3B0(sc) |

| #define | USES_WARPCORE(sc) (CHIP_IS_E3(sc)) |

| #define | CHIP_IS_E2E3(sc) |

| #define | CHIP_IS_MF_CAP(sc) |

| #define | IS_VF(sc) |

| #define | IS_PF(sc) (!IS_VF(sc)) |

| #define | CONFIGURE_NIC_MODE(sc) (!CHIP_IS_E1x(sc) && !CNIC_ENABLED(sc)) |

| #define | CHIP_4_PORT_MODE 0x0 |

| #define | CHIP_2_PORT_MODE 0x1 |

| #define | CHIP_PORT_MODE_NONE 0x2 |

| #define | CHIP_PORT_MODE(sc) ((sc)->devinfo.chip_port_mode) |

| #define | CHIP_IS_MODE_4_PORT(sc) (CHIP_PORT_MODE(sc) == CHIP_4_PORT_MODE) |

| #define | INT_BLOCK_HC 0 |

| #define | INT_BLOCK_IGU 1 |

| #define | INT_BLOCK_MODE_NORMAL 0 |

| #define | INT_BLOCK_MODE_BW_COMP 2 |

| #define | CHIP_INT_MODE_IS_NBC(sc) |

| #define | CHIP_INT_MODE_IS_BC(sc) (!CHIP_INT_MODE_IS_NBC(sc)) |

| #define | NVRAM_1MB_SIZE 0x20000 |

| #define | NVRAM_TIMEOUT_COUNT 30000 |

| #define | NVRAM_PAGE_SIZE 256 |

| #define | BXE_PM_CAPABLE_FLAG 0x00000001 |

| #define | BXE_PCIE_CAPABLE_FLAG 0x00000002 |

| #define | BXE_MSI_CAPABLE_FLAG 0x00000004 |

| #define | BXE_MSIX_CAPABLE_FLAG 0x00000008 |

| #define | BXE_STATE_CLOSED 0x0000 |

| #define | BXE_STATE_OPENING_WAITING_LOAD 0x1000 |

| #define | BXE_STATE_OPENING_WAITING_PORT 0x2000 |

| #define | BXE_STATE_OPEN 0x3000 |

| #define | BXE_STATE_CLOSING_WAITING_HALT 0x4000 |

| #define | BXE_STATE_CLOSING_WAITING_DELETE 0x5000 |

| #define | BXE_STATE_CLOSING_WAITING_UNLOAD 0x6000 |

| #define | BXE_STATE_DISABLED 0xD000 |

| #define | BXE_STATE_DIAG 0xE000 |

| #define | BXE_STATE_ERROR 0xF000 |

| #define | BXE_ONE_PORT_FLAG 0x00000001 |

| #define | BXE_NO_ISCSI 0x00000002 |

| #define | BXE_NO_FCOE 0x00000004 |

| #define | BXE_ONE_PORT(sc) (sc->flags & BXE_ONE_PORT_FLAG) |

| #define | BXE_NO_MCP_FLAG 0x00000200 |

| #define | BXE_NOMCP(sc) (sc->flags & BXE_NO_MCP_FLAG) |

| #define | BXE_MF_FUNC_DIS 0x00000800 |

| #define | BXE_TX_SWITCHING 0x00001000 |

| #define | BXE_NO_PULSE 0x00002000 |

| #define | MAX_BARS 5 |

| #define | PERIODIC_STOP 0 |

| #define | PERIODIC_GO 1 |

| #define | CHIP_TQ_NONE 0 |

| #define | CHIP_TQ_START 1 |

| #define | CHIP_TQ_STOP 2 |

| #define | CHIP_TQ_REINIT 3 |

| #define | SC_PATH(sc) (sc->path_id) |

| #define | SC_PORT(sc) (sc->pfunc_rel & 1) |

| #define | SC_FUNC(sc) (sc->pfunc_rel) |

| #define | SC_ABS_FUNC(sc) (sc->pfunc_abs) |

| #define | SC_VN(sc) (sc->pfunc_rel >> 1) |

| #define | SC_L_ID(sc) (SC_VN(sc) << 2) |

| #define | PORT_ID(sc) SC_PORT(sc) |

| #define | PATH_ID(sc) SC_PATH(sc) |

| #define | VNIC_ID(sc) SC_VN(sc) |

| #define | FUNC_ID(sc) SC_FUNC(sc) |

| #define | ABS_FUNC_ID(sc) SC_ABS_FUNC(sc) |

| #define | SC_FW_MB_IDX_VN(sc, vn) |

| #define | SC_FW_MB_IDX(sc) SC_FW_MB_IDX_VN(sc, SC_VN(sc)) |

| #define | BXE_CORE_TRYLOCK(sc) sx_try_xlock(&sc->core_sx) |

| #define | BXE_CORE_LOCK(sc) sx_xlock(&sc->core_sx) |

| #define | BXE_CORE_UNLOCK(sc) sx_xunlock(&sc->core_sx) |

| #define | BXE_CORE_LOCK_ASSERT(sc) sx_assert(&sc->core_sx, SA_XLOCKED) |

| #define | BXE_SP_LOCK(sc) mtx_lock(&sc->sp_mtx) |

| #define | BXE_SP_UNLOCK(sc) mtx_unlock(&sc->sp_mtx) |

| #define | BXE_SP_LOCK_ASSERT(sc) mtx_assert(&sc->sp_mtx, MA_OWNED) |

| #define | BXE_DMAE_LOCK(sc) mtx_lock(&sc->dmae_mtx) |

| #define | BXE_DMAE_UNLOCK(sc) mtx_unlock(&sc->dmae_mtx) |

| #define | BXE_DMAE_LOCK_ASSERT(sc) mtx_assert(&sc->dmae_mtx, MA_OWNED) |

| #define | BXE_FWMB_LOCK(sc) mtx_lock(&sc->fwmb_mtx) |

| #define | BXE_FWMB_UNLOCK(sc) mtx_unlock(&sc->fwmb_mtx) |

| #define | BXE_FWMB_LOCK_ASSERT(sc) mtx_assert(&sc->fwmb_mtx, MA_OWNED) |

| #define | BXE_PRINT_LOCK(sc) mtx_lock(&sc->print_mtx) |

| #define | BXE_PRINT_UNLOCK(sc) mtx_unlock(&sc->print_mtx) |

| #define | BXE_PRINT_LOCK_ASSERT(sc) mtx_assert(&sc->print_mtx, MA_OWNED) |

| #define | BXE_STATS_LOCK(sc) mtx_lock(&sc->stats_mtx) |

| #define | BXE_STATS_UNLOCK(sc) mtx_unlock(&sc->stats_mtx) |

| #define | BXE_STATS_LOCK_ASSERT(sc) mtx_assert(&sc->stats_mtx, MA_OWNED) |

| #define | BXE_MCAST_LOCK(sc) mtx_lock(&sc->mcast_mtx); |

| #define | BXE_MCAST_UNLOCK(sc) mtx_unlock(&sc->mcast_mtx); |

| #define | BXE_MCAST_LOCK_ASSERT(sc) mtx_assert(&sc->mcast_mtx, MA_OWNED) |

| #define | DMAE_READY(sc) (sc->dmae_ready) |

| #define | BXE_RECOVERY_DONE 1 |

| #define | BXE_RECOVERY_INIT 2 |

| #define | BXE_RECOVERY_WAIT 3 |

| #define | BXE_RECOVERY_FAILED 4 |

| #define | BXE_RECOVERY_NIC_LOADING 5 |

| #define | BXE_ERR_TXQ_STUCK 0x1 /* Tx queue stuck detected by driver. */ |

| #define | BXE_ERR_MISC 0x2 /* MISC ERR */ |

| #define | BXE_ERR_PARITY 0x4 /* Parity error detected. */ |

| #define | BXE_ERR_STATS_TO 0x8 /* Statistics timeout detected. */ |

| #define | BXE_ERR_MC_ASSERT 0x10 /* MC assert attention received. */ |

| #define | BXE_ERR_PANIC 0x20 /* Driver asserted. */ |

| #define | BXE_ERR_MCP_ASSERT 0x40 /* MCP assert attention received. No Recovery*/ |

| #define | BXE_ERR_GLOBAL 0x80 /* PCIe/PXP/IGU/MISC/NIG device blocks error- needs PCIe/Fundamental reset */ |

| #define | BXE_RX_MODE_NONE 0 |

| #define | BXE_RX_MODE_NORMAL 1 |

| #define | BXE_RX_MODE_ALLMULTI 2 |

| #define | BXE_RX_MODE_PROMISC 3 |

| #define | BXE_MAX_MULTICAST 64 |

| #define | AUTO_GREEN_HW_DEFAULT 0 |

| #define | AUTO_GREEN_FORCE_ON 1 |

| #define | AUTO_GREEN_FORCE_OFF 2 |

| #define | INTR_MODE_INTX 0 |

| #define | INTR_MODE_MSI 1 |

| #define | INTR_MODE_MSIX 2 |

| #define | DEF_SB_IGU_ID 16 |

| #define | DEF_SB_ID HC_SP_SB_ID |

| #define | HC_SP_INDEX_ETH_DEF_CONS 3 |

| #define | HC_SP_INDEX_EQ_CONS 7 |

| #define | HC_SP_INDEX_ETH_FCOE_TX_CQ_CONS 6 |

| #define | HC_SP_INDEX_ETH_FCOE_RX_CQ_CONS 4 |

| #define | HC_SP_INDEX_ETH_ISCSI_CQ_CONS 5 |

| #define | HC_SP_INDEX_ETH_ISCSI_RX_CQ_CONS 1 |

| #define | NUM_EQ_PAGES 1 /* must be a power of 2 */ |

| #define | EQ_DESC_CNT_PAGE (BCM_PAGE_SIZE / sizeof(union event_ring_elem)) |

| #define | EQ_DESC_MAX_PAGE (EQ_DESC_CNT_PAGE - 1) |

| #define | NUM_EQ_DESC (EQ_DESC_CNT_PAGE * NUM_EQ_PAGES) |

| #define | EQ_DESC_MASK (NUM_EQ_DESC - 1) |

| #define | MAX_EQ_AVAIL (EQ_DESC_MAX_PAGE * NUM_EQ_PAGES - 2) |

| #define | NEXT_EQ_IDX(x) |

| #define | EQ_DESC(x) ((x) & EQ_DESC_MASK) |

| #define | SP_DESC_CNT (BCM_PAGE_SIZE / sizeof(struct eth_spe)) |

| #define | MAX_SP_DESC_CNT (SP_DESC_CNT - 1) |

| #define | MAX_SPQ_PENDING 8 |

| #define | GUNZIP_BUF(sc) (sc->gz_buf) |

| #define | GUNZIP_OUTLEN(sc) (sc->gz_outlen) |

| #define | GUNZIP_PHYS(sc) (sc->gz_buf_dma.paddr) |

| #define | FW_BUF_SIZE 0x40000 |

| #define | INIT_MODE_FLAGS(sc) (sc->init_mode_flags) |

| #define | INIT_OPS(sc) (sc->init_ops) |

| #define | INIT_OPS_OFFSETS(sc) (sc->init_ops_offsets) |

| #define | INIT_DATA(sc) (sc->init_data) |

| #define | INIT_TSEM_INT_TABLE_DATA(sc) (sc->tsem_int_table_data) |

| #define | INIT_TSEM_PRAM_DATA(sc) (sc->tsem_pram_data) |

| #define | INIT_USEM_INT_TABLE_DATA(sc) (sc->usem_int_table_data) |

| #define | INIT_USEM_PRAM_DATA(sc) (sc->usem_pram_data) |

| #define | INIT_XSEM_INT_TABLE_DATA(sc) (sc->xsem_int_table_data) |

| #define | INIT_XSEM_PRAM_DATA(sc) (sc->xsem_pram_data) |

| #define | INIT_CSEM_INT_TABLE_DATA(sc) (sc->csem_int_table_data) |

| #define | INIT_CSEM_PRAM_DATA(sc) (sc->csem_pram_data) |

| #define | ILT_MAX_L2_LINES 8 |

| #define | ILT_MAX_LINES 256 |

| #define | BXE_MAX_RSS_COUNT(sc) ((sc)->igu_sb_cnt - CNIC_SUPPORT(sc)) |

| #define | BXE_L2_MAX_CID(sc) (BXE_MAX_RSS_COUNT(sc) * ECORE_MULTI_TX_COS + 2 * CNIC_SUPPORT(sc)) |

| #define | BXE_L2_CID_COUNT(sc) (BXE_NUM_ETH_QUEUES(sc) * ECORE_MULTI_TX_COS + 2 * CNIC_SUPPORT(sc)) |

| #define | L2_ILT_LINES(sc) (DIV_ROUND_UP(BXE_L2_CID_COUNT(sc), ILT_PAGE_CIDS)) |

| #define | BXE_DCB_STATE_OFF 0 |

| #define | BXE_DCB_STATE_ON 1 |

| #define | BXE_DCBX_ENABLED_OFF 0 |

| #define | BXE_DCBX_ENABLED_ON_NEG_OFF 1 |

| #define | BXE_DCBX_ENABLED_ON_NEG_ON 2 |

| #define | BXE_DCBX_ENABLED_INVALID -1 |

| #define | CNIC_SUPPORT(sc) 0 /* ((sc)->cnic_support) */ |

| #define | CNIC_ENABLED(sc) 0 /* ((sc)->cnic_enabled) */ |

| #define | CNIC_LOADED(sc) 0 /* ((sc)->cnic_loaded) */ |

| #define | BXE_MAX_PRIORITY 8 |

| #define | BXE_IOC_RD_NVRAM 1 |

| #define | BXE_IOC_WR_NVRAM 2 |

| #define | BXE_IOC_STATS_SHOW_NUM 3 |

| #define | BXE_IOC_STATS_SHOW_STR 4 |

| #define | BXE_IOC_STATS_SHOW_CNT 5 |

| #define | FUNC_FLG_RSS 0x0001 |

| #define | FUNC_FLG_STATS 0x0002 |

| #define | FUNC_FLG_TPA 0x0008 |

| #define | FUNC_FLG_SPQ 0x0010 |

| #define | FUNC_FLG_LEADING 0x0020 /* PF only */ |

| #define | BAR0 0 |

| #define | BAR1 2 |

| #define | BAR2 4 |

| #define | REG_WR8(sc, offset, val) |

| #define | REG_WR16(sc, offset, val) |

| #define | REG_WR32(sc, offset, val) |

| #define | REG_RD8(sc, offset) |

| #define | REG_RD16(sc, offset) |

| #define | REG_RD32(sc, offset) |

| #define | REG_RD(sc, offset) REG_RD32(sc, offset) |

| #define | REG_WR(sc, offset, val) REG_WR32(sc, offset, val) |

| #define | REG_RD_IND(sc, offset) bxe_reg_rd_ind(sc, offset) |

| #define | REG_WR_IND(sc, offset, val) bxe_reg_wr_ind(sc, offset, val) |

| #define | BXE_SP(sc, var) (&(sc)->sp->var) |

| #define | BXE_SP_MAPPING(sc, var) (sc->sp_dma.paddr + offsetof(struct bxe_slowpath, var)) |

| #define | BXE_FP(sc, nr, var) ((sc)->fp[(nr)].var) |

| #define | BXE_SP_OBJ(sc, fp) ((sc)->sp_objs[(fp)->index]) |

| #define | REG_RD_DMAE(sc, offset, valp, len32) |

| #define | REG_WR_DMAE(sc, offset, valp, len32) |

| #define | REG_WR_DMAE_LEN(sc, offset, valp, len32) REG_WR_DMAE(sc, offset, valp, len32) |

| #define | REG_RD_DMAE_LEN(sc, offset, valp, len32) REG_RD_DMAE(sc, offset, valp, len32) |

| #define | VIRT_WR_DMAE_LEN(sc, data, addr, len32, le32_swap) |

| #define | BXE_DB_MIN_SHIFT 3 /* 8 bytes */ |

| #define | BXE_DB_SHIFT 7 /* 128 bytes */ |

| #define | DPM_TRIGGER_TYPE 0x40 |

| #define | DOORBELL(sc, cid, val) |

| #define | SHMEM_ADDR(sc, field) (sc->devinfo.shmem_base + offsetof(struct shmem_region, field)) |

| #define | SHMEM_RD(sc, field) REG_RD(sc, SHMEM_ADDR(sc, field)) |

| #define | SHMEM_RD16(sc, field) REG_RD16(sc, SHMEM_ADDR(sc, field)) |

| #define | SHMEM_WR(sc, field, val) REG_WR(sc, SHMEM_ADDR(sc, field), val) |

| #define | SHMEM2_ADDR(sc, field) (sc->devinfo.shmem2_base + offsetof(struct shmem2_region, field)) |

| #define | SHMEM2_HAS(sc, field) |

| #define | SHMEM2_RD(sc, field) REG_RD(sc, SHMEM2_ADDR(sc, field)) |

| #define | SHMEM2_WR(sc, field, val) REG_WR(sc, SHMEM2_ADDR(sc, field), val) |

| #define | MFCFG_ADDR(sc, field) (sc->devinfo.mf_cfg_base + offsetof(struct mf_cfg, field)) |

| #define | MFCFG_RD(sc, field) REG_RD(sc, MFCFG_ADDR(sc, field)) |

| #define | MFCFG_RD16(sc, field) REG_RD16(sc, MFCFG_ADDR(sc, field)) |

| #define | MFCFG_WR(sc, field, val) REG_WR(sc, MFCFG_ADDR(sc, field), val) |

| #define | DMAE_TIMEOUT -1 |

| #define | DMAE_PCI_ERROR -2 /* E2 and onward */ |

| #define | DMAE_NOT_RDY -3 |

| #define | DMAE_PCI_ERR_FLAG 0x80000000 |

| #define | DMAE_SRC_PCI 0 |

| #define | DMAE_SRC_GRC 1 |

| #define | DMAE_DST_NONE 0 |

| #define | DMAE_DST_PCI 1 |

| #define | DMAE_DST_GRC 2 |

| #define | DMAE_COMP_PCI 0 |

| #define | DMAE_COMP_GRC 1 |

| #define | DMAE_COMP_REGULAR 0 |

| #define | DMAE_COM_SET_ERR 1 |

| #define | DMAE_CMD_SRC_PCI (DMAE_SRC_PCI << DMAE_CMD_SRC_SHIFT) |

| #define | DMAE_CMD_SRC_GRC (DMAE_SRC_GRC << DMAE_CMD_SRC_SHIFT) |

| #define | DMAE_CMD_DST_PCI (DMAE_DST_PCI << DMAE_CMD_DST_SHIFT) |

| #define | DMAE_CMD_DST_GRC (DMAE_DST_GRC << DMAE_CMD_DST_SHIFT) |

| #define | DMAE_CMD_C_DST_PCI (DMAE_COMP_PCI << DMAE_CMD_C_DST_SHIFT) |

| #define | DMAE_CMD_C_DST_GRC (DMAE_COMP_GRC << DMAE_CMD_C_DST_SHIFT) |

| #define | DMAE_CMD_ENDIANITY_NO_SWAP (0 << DMAE_CMD_ENDIANITY_SHIFT) |

| #define | DMAE_CMD_ENDIANITY_B_SWAP (1 << DMAE_CMD_ENDIANITY_SHIFT) |

| #define | DMAE_CMD_ENDIANITY_DW_SWAP (2 << DMAE_CMD_ENDIANITY_SHIFT) |

| #define | DMAE_CMD_ENDIANITY_B_DW_SWAP (3 << DMAE_CMD_ENDIANITY_SHIFT) |

| #define | DMAE_CMD_PORT_0 0 |

| #define | DMAE_CMD_PORT_1 DMAE_CMD_PORT |

| #define | DMAE_SRC_PF 0 |

| #define | DMAE_SRC_VF 1 |

| #define | DMAE_DST_PF 0 |

| #define | DMAE_DST_VF 1 |

| #define | DMAE_C_SRC 0 |

| #define | DMAE_C_DST 1 |

| #define | DMAE_LEN32_RD_MAX 0x80 |

| #define | DMAE_LEN32_WR_MAX(sc) (CHIP_IS_E1(sc) ? 0x400 : 0x2000) |

| #define | DMAE_COMP_VAL 0x60d0d0ae /* E2 and beyond, upper bit indicates error */ |

| #define | MAX_DMAE_C_PER_PORT 8 |

| #define | INIT_DMAE_C(sc) ((SC_PORT(sc) * MAX_DMAE_C_PER_PORT) + SC_VN(sc)) |

| #define | PMF_DMAE_C(sc) ((SC_PORT(sc) * MAX_DMAE_C_PER_PORT) + E1HVN_MAX) |

| #define | ATTN_NIG_FOR_FUNC (1L << 8) |

| #define | ATTN_SW_TIMER_4_FUNC (1L << 9) |

| #define | GPIO_2_FUNC (1L << 10) |

| #define | GPIO_3_FUNC (1L << 11) |

| #define | GPIO_4_FUNC (1L << 12) |

| #define | ATTN_GENERAL_ATTN_1 (1L << 13) |

| #define | ATTN_GENERAL_ATTN_2 (1L << 14) |

| #define | ATTN_GENERAL_ATTN_3 (1L << 15) |

| #define | ATTN_GENERAL_ATTN_4 (1L << 13) |

| #define | ATTN_GENERAL_ATTN_5 (1L << 14) |

| #define | ATTN_GENERAL_ATTN_6 (1L << 15) |

| #define | ATTN_HARD_WIRED_MASK 0xff00 |

| #define | ATTENTION_ID 4 |

| #define | AEU_IN_ATTN_BITS_PXPPCICLOCKCLIENT_PARITY_ERROR AEU_INPUTS_ATTN_BITS_PXPPCICLOCKCLIENT_PARITY_ERROR |

| #define | MAX_IGU_ATTN_ACK_TO 100 |

| #define | STORM_ASSERT_ARRAY_SIZE 50 |

| #define | BXE_PMF_LINK_ASSERT(sc) GENERAL_ATTEN_OFFSET(LINK_SYNC_ATTENTION_BIT_FUNC_0 + SC_FUNC(sc)) |

| #define | BXE_MC_ASSERT_BITS |

| #define | BXE_MCP_ASSERT GENERAL_ATTEN_OFFSET(MCP_FATAL_ASSERT_ATTENTION_BIT) |

| #define | BXE_GRC_TIMEOUT GENERAL_ATTEN_OFFSET(LATCHED_ATTN_TIMEOUT_GRC) |

| #define | BXE_GRC_RSV |

| #define | MULTI_MASK 0x7f |

| #define | PFS_PER_PORT(sc) ((CHIP_PORT_MODE(sc) == CHIP_4_PORT_MODE) ? 2 : 4) |

| #define | SC_MAX_VN_NUM(sc) PFS_PER_PORT(sc) |

| #define | FIRST_ABS_FUNC_IN_PORT(sc) |

| #define | FOREACH_ABS_FUNC_IN_PORT(sc, i) |

| #define | BXE_SWCID_SHIFT 17 |

| #define | BXE_SWCID_MASK ((0x1 << BXE_SWCID_SHIFT) - 1) |

| #define | SW_CID(x) (le32toh(x) & BXE_SWCID_MASK) |

| #define | CQE_CMD(x) (le32toh(x) >> COMMON_RAMROD_ETH_RX_CQE_CMD_ID_SHIFT) |

| #define | CQE_TYPE(cqe_fp_flags) ((cqe_fp_flags) & ETH_FAST_PATH_RX_CQE_TYPE) |

| #define | CQE_TYPE_START(cqe_type) ((cqe_type) == RX_ETH_CQE_TYPE_ETH_START_AGG) |

| #define | CQE_TYPE_STOP(cqe_type) ((cqe_type) == RX_ETH_CQE_TYPE_ETH_STOP_AGG) |

| #define | CQE_TYPE_SLOW(cqe_type) ((cqe_type) == RX_ETH_CQE_TYPE_ETH_RAMROD) |

| #define | CQE_TYPE_FAST(cqe_type) ((cqe_type) == RX_ETH_CQE_TYPE_ETH_FASTPATH) |

| #define | HW_CID(sc, x) ((SC_PORT(sc) << 23) | (SC_VN(sc) << BXE_SWCID_SHIFT) | (x)) |

| #define | SPEED_10 10 |

| #define | SPEED_100 100 |

| #define | SPEED_1000 1000 |

| #define | SPEED_2500 2500 |

| #define | SPEED_10000 10000 |

| #define | PCI_PM_D0 1 |

| #define | PCI_PM_D3hot 2 |

| #define | DUPLEX_UNKNOWN (0xff) |

| #define | SPEED_UNKNOWN (-1) |

| #define | AUTONEG_DISABLE 0x00 |

| #define | AUTONEG_ENABLE 0x01 |

| #define | PORT_TP 0x00 |

| #define | PORT_AUI 0x01 |

| #define | PORT_MII 0x02 |

| #define | PORT_FIBRE 0x03 |

| #define | PORT_BNC 0x04 |

| #define | PORT_DA 0x05 |

| #define | PORT_NONE 0xef |

| #define | PORT_OTHER 0xff |

| #define | DBG_LOAD 0x00000001 /* load and unload */ |

| #define | DBG_INTR 0x00000002 /* interrupt handling */ |

| #define | DBG_SP 0x00000004 /* slowpath handling */ |

| #define | DBG_STATS 0x00000008 /* stats updates */ |

| #define | DBG_TX 0x00000010 /* packet transmit */ |

| #define | DBG_RX 0x00000020 /* packet receive */ |

| #define | DBG_PHY 0x00000040 /* phy/link handling */ |

| #define | DBG_IOCTL 0x00000080 /* ioctl handling */ |

| #define | DBG_MBUF 0x00000100 /* dumping mbuf info */ |

| #define | DBG_REGS 0x00000200 /* register access */ |

| #define | DBG_LRO 0x00000400 /* lro processing */ |

| #define | DBG_ASSERT 0x80000000 /* debug assert */ |

| #define | DBG_ALL 0xFFFFFFFF /* flying monkeys */ |

| #define | DBASSERT(sc, exp, msg) |

| #define | BLOGD(sc, codepath, format, args...) |

| #define | BLOGI(sc, format, args...) |

| #define | BLOGW(sc, format, args...) |

| #define | BLOGE(sc, format, args...) |

| #define | bxe_panic(sc, msg) device_printf((sc)->dev, "%s (%s,%d)\n", __FUNCTION__, __FILE__, __LINE__); |

| #define | CATC_TRIGGER(sc, data) REG_WR((sc), 0x2000, (data)); |

| #define | CATC_TRIGGER_START(sc) CATC_TRIGGER((sc), 0xcafecafe) |

| #define | BXE_SET_FLOWID(m) M_HASHTYPE_SET(m, M_HASHTYPE_OPAQUE) |

| #define | BXE_VALID_FLOWID(m) (M_HASHTYPE_GET(m) != M_HASHTYPE_NONE) |

Enumerations | |

| enum | { OOO_IDX_OFFSET , FCOE_IDX_OFFSET , FWD_IDX_OFFSET } |

| enum | { BXE_PORT_QUERY_IDX , BXE_PF_QUERY_IDX , BXE_FCOE_QUERY_IDX , BXE_FIRST_QUEUE_QUERY_IDX } |

| enum | { BXE_LINK_REPORT_FULL_DUPLEX , BXE_LINK_REPORT_LINK_DOWN , BXE_LINK_REPORT_RX_FC_ON , BXE_LINK_REPORT_TX_FC_ON } |

Functions | |

| __FBSDID ("$FreeBSD$") | |

| static int | bxe_ilog2 (int x) |

| int | bxe_test_bit (int nr, volatile unsigned long *addr) |

| void | bxe_set_bit (unsigned int nr, volatile unsigned long *addr) |

| void | bxe_clear_bit (int nr, volatile unsigned long *addr) |

| int | bxe_test_and_set_bit (int nr, volatile unsigned long *addr) |

| int | bxe_test_and_clear_bit (int nr, volatile unsigned long *addr) |

| int | bxe_cmpxchg (volatile int *addr, int old, int new) |

| void | bxe_reg_wr_ind (struct bxe_softc *sc, uint32_t addr, uint32_t val) |

| uint32_t | bxe_reg_rd_ind (struct bxe_softc *sc, uint32_t addr) |

| int | bxe_dma_alloc (struct bxe_softc *sc, bus_size_t size, struct bxe_dma *dma, const char *msg) |

| void | bxe_dma_free (struct bxe_softc *sc, struct bxe_dma *dma) |

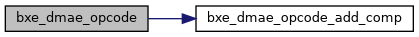

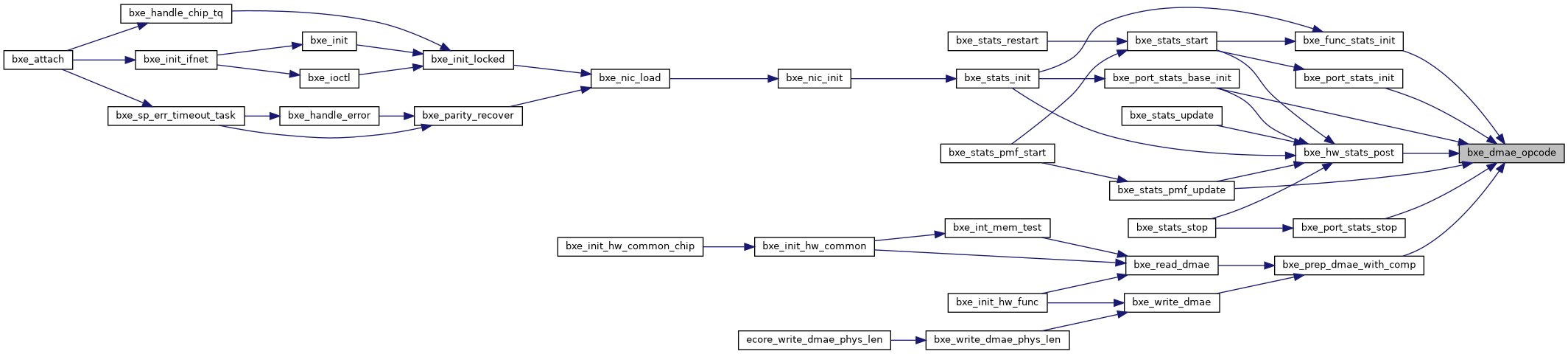

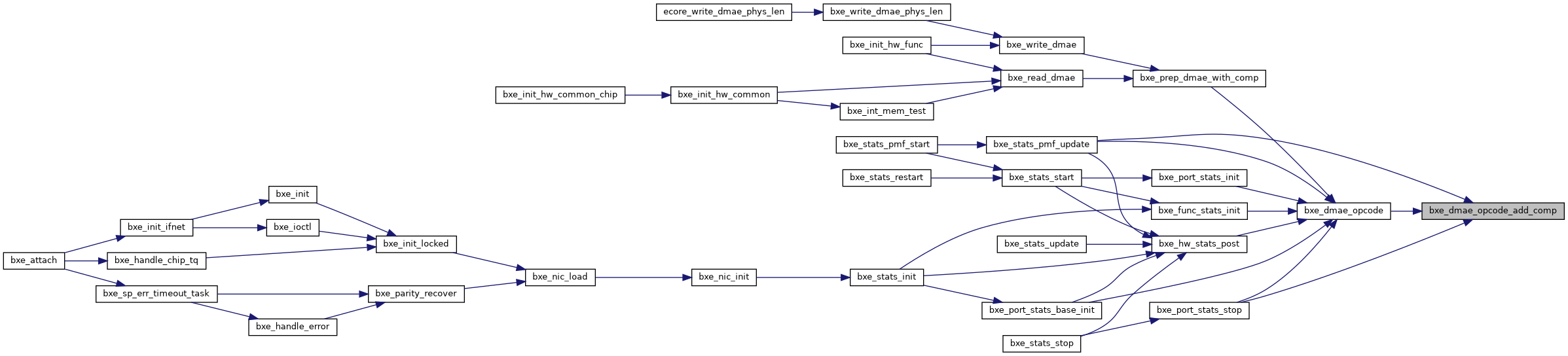

| uint32_t | bxe_dmae_opcode_add_comp (uint32_t opcode, uint8_t comp_type) |

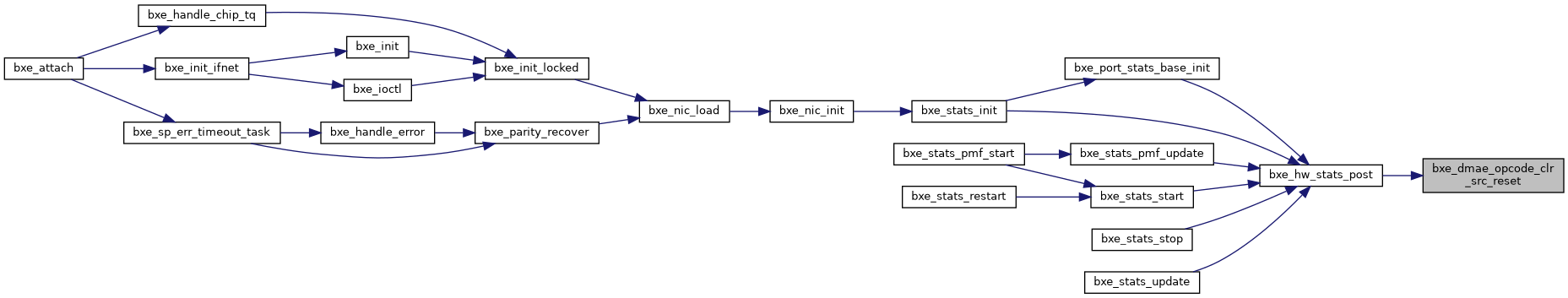

| uint32_t | bxe_dmae_opcode_clr_src_reset (uint32_t opcode) |

| uint32_t | bxe_dmae_opcode (struct bxe_softc *sc, uint8_t src_type, uint8_t dst_type, uint8_t with_comp, uint8_t comp_type) |

| void | bxe_post_dmae (struct bxe_softc *sc, struct dmae_cmd *dmae, int idx) |

| void | bxe_read_dmae (struct bxe_softc *sc, uint32_t src_addr, uint32_t len32) |

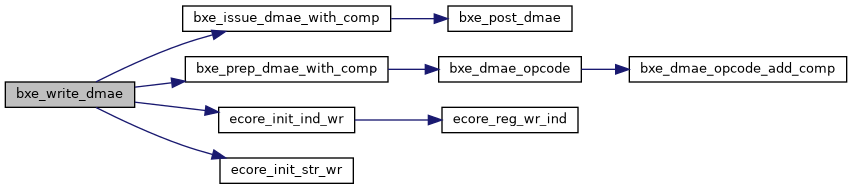

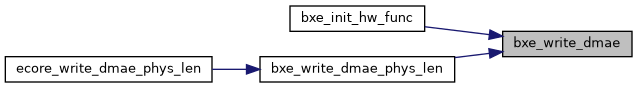

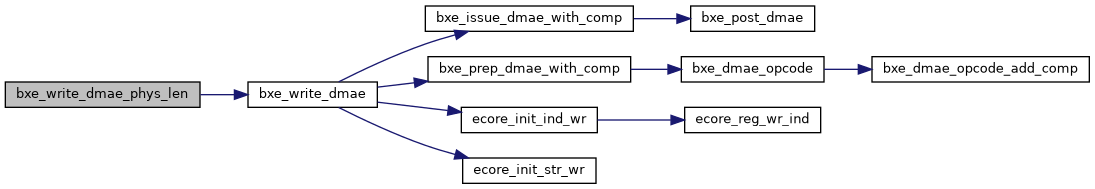

| void | bxe_write_dmae (struct bxe_softc *sc, bus_addr_t dma_addr, uint32_t dst_addr, uint32_t len32) |

| void | bxe_write_dmae_phys_len (struct bxe_softc *sc, bus_addr_t phys_addr, uint32_t addr, uint32_t len) |

| void | bxe_set_ctx_validation (struct bxe_softc *sc, struct eth_context *cxt, uint32_t cid) |

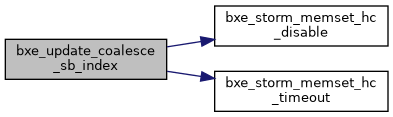

| void | bxe_update_coalesce_sb_index (struct bxe_softc *sc, uint8_t fw_sb_id, uint8_t sb_index, uint8_t disable, uint16_t usec) |

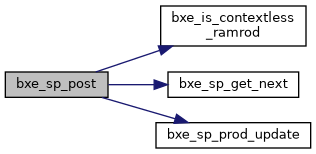

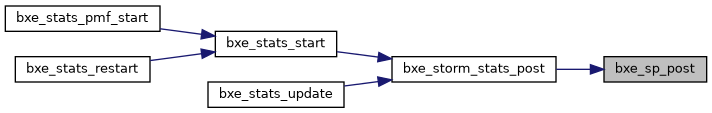

| int | bxe_sp_post (struct bxe_softc *sc, int command, int cid, uint32_t data_hi, uint32_t data_lo, int cmd_type) |

| void | bxe_igu_ack_sb (struct bxe_softc *sc, uint8_t igu_sb_id, uint8_t segment, uint16_t index, uint8_t op, uint8_t update) |

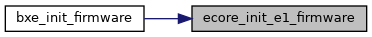

| void | ecore_init_e1_firmware (struct bxe_softc *sc) |

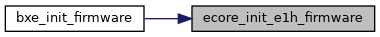

| void | ecore_init_e1h_firmware (struct bxe_softc *sc) |

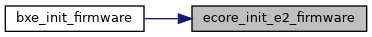

| void | ecore_init_e2_firmware (struct bxe_softc *sc) |

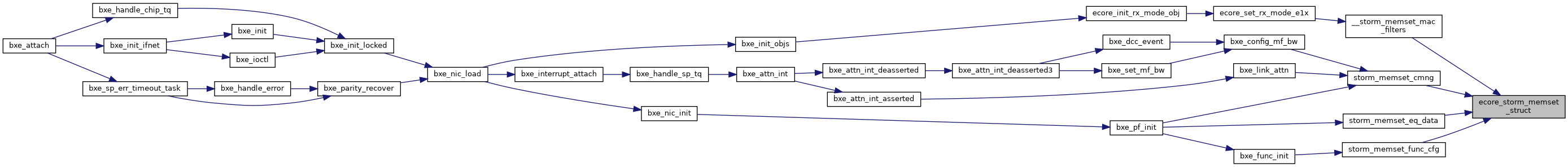

| void | ecore_storm_memset_struct (struct bxe_softc *sc, uint32_t addr, size_t size, uint32_t *data) |

| void | bxe_dump_mem (struct bxe_softc *sc, char *tag, uint8_t *mem, uint32_t len) |

| void | bxe_dump_mbuf_data (struct bxe_softc *sc, char *pTag, struct mbuf *m, uint8_t contents) |

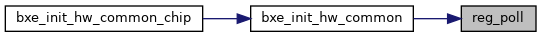

| static uint32_t | reg_poll (struct bxe_softc *sc, uint32_t reg, uint32_t expected, int ms, int wait) |

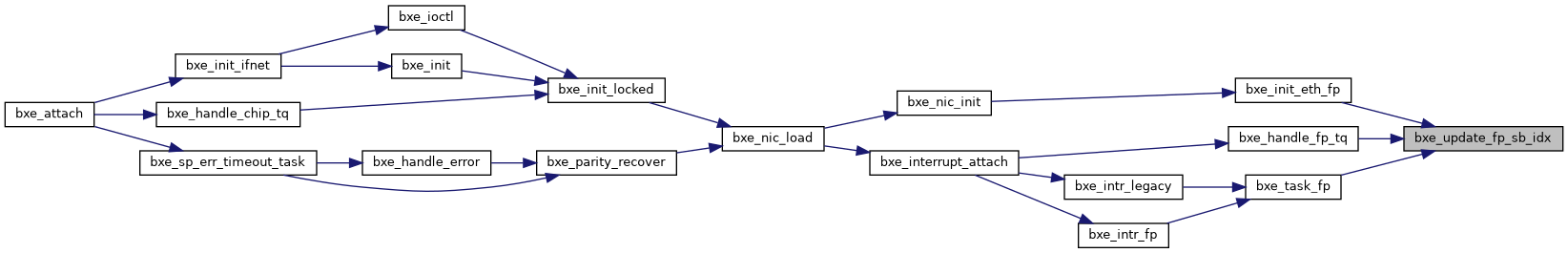

| static void | bxe_update_fp_sb_idx (struct bxe_fastpath *fp) |

| static void | bxe_igu_ack_sb_gen (struct bxe_softc *sc, uint8_t igu_sb_id, uint8_t segment, uint16_t index, uint8_t op, uint8_t update, uint32_t igu_addr) |

| static void | bxe_hc_ack_sb (struct bxe_softc *sc, uint8_t sb_id, uint8_t storm, uint16_t index, uint8_t op, uint8_t update) |

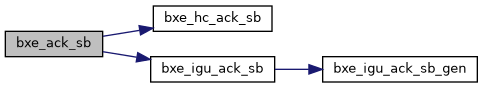

| static void | bxe_ack_sb (struct bxe_softc *sc, uint8_t igu_sb_id, uint8_t storm, uint16_t index, uint8_t op, uint8_t update) |

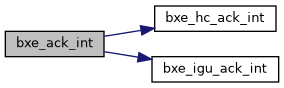

| static uint16_t | bxe_hc_ack_int (struct bxe_softc *sc) |

| static uint16_t | bxe_igu_ack_int (struct bxe_softc *sc) |

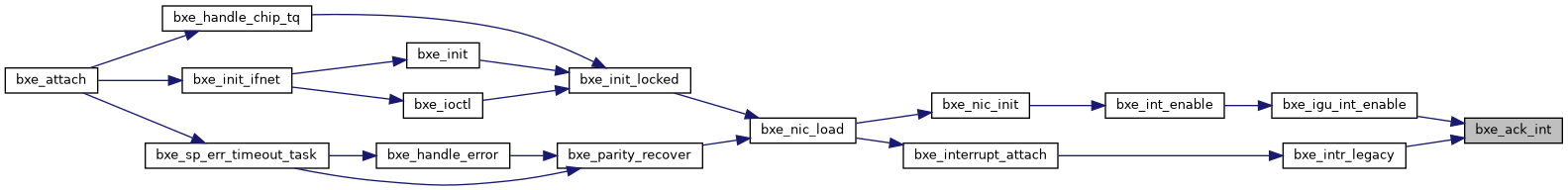

| static uint16_t | bxe_ack_int (struct bxe_softc *sc) |

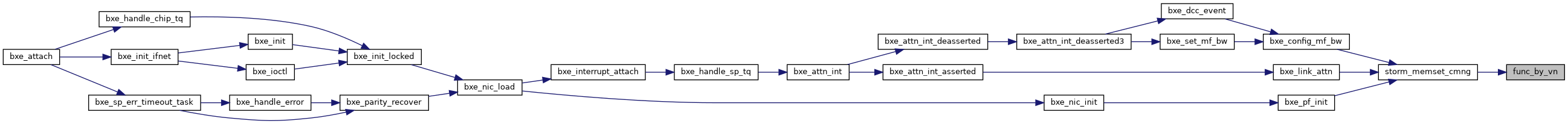

| static int | func_by_vn (struct bxe_softc *sc, int vn) |

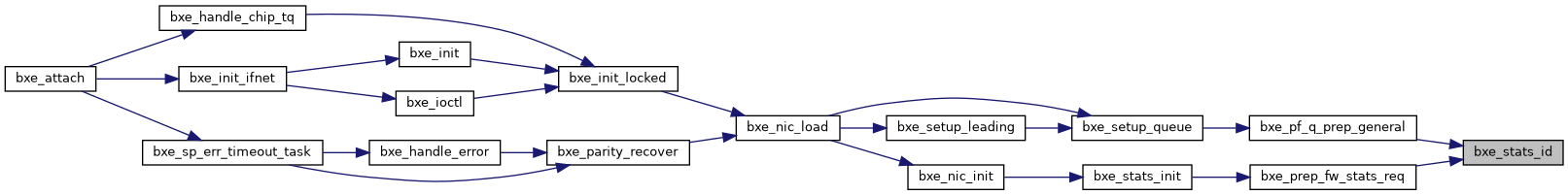

| static uint8_t | bxe_stats_id (struct bxe_fastpath *fp) |

Variables | |

| static const uint32_t | dmae_reg_go_c [] |

Macro Definition Documentation

◆ __LITTLE_ENDIAN

◆ __SGE_MASK_CLEAR_BIT

| #define __SGE_MASK_CLEAR_BIT | ( | el, | |

| bit | |||

| ) |

◆ __SGE_MASK_SET_BIT

| #define __SGE_MASK_SET_BIT | ( | el, | |

| bit | |||

| ) |

◆ ABS_FUNC_ID

| #define ABS_FUNC_ID | ( | sc | ) | SC_ABS_FUNC(sc) |

◆ ADVERTISED_10000baseT_Full

◆ ADVERTISED_1000baseT_Full

◆ ADVERTISED_1000baseT_Half

◆ ADVERTISED_100baseT_Full

◆ ADVERTISED_100baseT_Half

◆ ADVERTISED_10baseT_Full

◆ ADVERTISED_10baseT_Half

◆ ADVERTISED_2500baseX_Full

◆ ADVERTISED_Asym_Pause

◆ ADVERTISED_Autoneg

◆ ADVERTISED_FIBRE

◆ ADVERTISED_Pause

◆ ADVERTISED_TP

◆ AEU_IN_ATTN_BITS_PXPPCICLOCKCLIENT_PARITY_ERROR

| #define AEU_IN_ATTN_BITS_PXPPCICLOCKCLIENT_PARITY_ERROR AEU_INPUTS_ATTN_BITS_PXPPCICLOCKCLIENT_PARITY_ERROR |

◆ AFEX_VLAN_MODE

| #define AFEX_VLAN_MODE | ( | sc | ) | ((sc)->devinfo.mf_info.afex_vlan_mode) |

◆ ARRSIZE

◆ ATTENTION_ID

◆ ATTN_GENERAL_ATTN_1

◆ ATTN_GENERAL_ATTN_2

◆ ATTN_GENERAL_ATTN_3

◆ ATTN_GENERAL_ATTN_4

◆ ATTN_GENERAL_ATTN_5

◆ ATTN_GENERAL_ATTN_6

◆ ATTN_HARD_WIRED_MASK

◆ ATTN_NIG_FOR_FUNC

◆ ATTN_SW_TIMER_4_FUNC

◆ AUTO_GREEN_FORCE_OFF

◆ AUTO_GREEN_FORCE_ON

◆ AUTO_GREEN_HW_DEFAULT

◆ AUTONEG_DISABLE

◆ AUTONEG_ENABLE

◆ BAR0

◆ BAR1

◆ BAR2

◆ BCM_PAGE_ALIGN

| #define BCM_PAGE_ALIGN | ( | addr | ) | ((addr + BCM_PAGE_SIZE - 1) & BCM_PAGE_MASK) |

◆ BCM_PAGE_MASK

| #define BCM_PAGE_MASK (~(BCM_PAGE_SIZE - 1)) |

◆ BCM_PAGE_SHIFT

◆ BCM_PAGE_SIZE

| #define BCM_PAGE_SIZE (1 << BCM_PAGE_SHIFT) |

◆ BD_TH_HI

| #define BD_TH_HI | ( | sc | ) | (BD_TH_LO(sc) + DROPLESS_FC_HEADROOM) |

◆ BD_TH_LO

| #define BD_TH_LO | ( | sc | ) |

◆ BLOGD

| #define BLOGD | ( | sc, | |

| codepath, | |||

| format, | |||

| args... | |||

| ) |

◆ BLOGE

| #define BLOGE | ( | sc, | |

| format, | |||

| args... | |||

| ) |

◆ BLOGI

| #define BLOGI | ( | sc, | |

| format, | |||

| args... | |||

| ) |

◆ BLOGW

| #define BLOGW | ( | sc, | |

| format, | |||

| args... | |||

| ) |

◆ BRB_SIZE

| #define BRB_SIZE | ( | sc | ) | (CHIP_IS_E3(sc) ? 1024 : 512) |

◆ BRCM_VENDORID

◆ BXE_BR_SIZE

◆ BXE_CIDS_PER_VF

| #define BXE_CIDS_PER_VF (1 << BXE_VF_CID_WND) |

◆ BXE_CLIENTS_PER_VF

◆ BXE_CORE_LOCK

◆ BXE_CORE_LOCK_ASSERT

| #define BXE_CORE_LOCK_ASSERT | ( | sc | ) | sx_assert(&sc->core_sx, SA_XLOCKED) |

◆ BXE_CORE_LOCK_SX

◆ BXE_CORE_TRYLOCK

◆ BXE_CORE_UNLOCK

◆ BXE_DB_MIN_SHIFT

◆ BXE_DB_SHIFT

◆ BXE_DCB_STATE_OFF

◆ BXE_DCB_STATE_ON

◆ BXE_DCBX_ENABLED_INVALID

◆ BXE_DCBX_ENABLED_OFF

◆ BXE_DCBX_ENABLED_ON_NEG_OFF

◆ BXE_DCBX_ENABLED_ON_NEG_ON

◆ BXE_DMAE_LOCK

◆ BXE_DMAE_LOCK_ASSERT

| #define BXE_DMAE_LOCK_ASSERT | ( | sc | ) | mtx_assert(&sc->dmae_mtx, MA_OWNED) |

◆ BXE_DMAE_UNLOCK

◆ BXE_ERR_GLOBAL

| #define BXE_ERR_GLOBAL 0x80 /* PCIe/PXP/IGU/MISC/NIG device blocks error- needs PCIe/Fundamental reset */ |

◆ BXE_ERR_MC_ASSERT

| #define BXE_ERR_MC_ASSERT 0x10 /* MC assert attention received. */ |

◆ BXE_ERR_MCP_ASSERT

| #define BXE_ERR_MCP_ASSERT 0x40 /* MCP assert attention received. No Recovery*/ |

◆ BXE_ERR_MISC

◆ BXE_ERR_PANIC

◆ BXE_ERR_PARITY

◆ BXE_ERR_STATS_TO

| #define BXE_ERR_STATS_TO 0x8 /* Statistics timeout detected. */ |

◆ BXE_ERR_TXQ_STUCK

| #define BXE_ERR_TXQ_STUCK 0x1 /* Tx queue stuck detected by driver. */ |

◆ bxe_fcoe

| #define bxe_fcoe | ( | sc, | |

| var | |||

| ) | (bxe_fcoe_fp(sc)->var) |

◆ bxe_fcoe_fp

◆ bxe_fcoe_inner_sp_obj

| #define bxe_fcoe_inner_sp_obj | ( | sc | ) | (&sc->sp_objs[FCOE_IDX(sc)]) |

◆ bxe_fcoe_sp_obj

| #define bxe_fcoe_sp_obj | ( | sc, | |

| var | |||

| ) | (bxe_fcoe_inner_sp_obj(sc)->var) |

◆ bxe_fcoe_tx

| #define bxe_fcoe_tx | ( | sc, | |

| var | |||

| ) | (bxe_fcoe_fp(sc)->txdata_ptr[FIRST_TX_COS_INDEX]->var) |

◆ BXE_FIRST_VF_CID

◆ BXE_FP

◆ BXE_FP_RX_LOCK

◆ BXE_FP_RX_LOCK_ASSERT

| #define BXE_FP_RX_LOCK_ASSERT | ( | fp | ) | mtx_assert(&fp->rx_mtx, MA_OWNED) |

◆ BXE_FP_RX_UNLOCK

◆ BXE_FP_STATE_CLOSED

◆ BXE_FP_STATE_HALTED

◆ BXE_FP_STATE_HALTING

◆ BXE_FP_STATE_IRQ

◆ BXE_FP_STATE_OPEN

◆ BXE_FP_STATE_OPENING

◆ BXE_FP_TX_LOCK

◆ BXE_FP_TX_LOCK_ASSERT

| #define BXE_FP_TX_LOCK_ASSERT | ( | fp | ) | mtx_assert(&fp->tx_mtx, MA_OWNED) |

◆ BXE_FP_TX_TRYLOCK

◆ BXE_FP_TX_UNLOCK

◆ BXE_FW_RX_ALIGN_END

| #define BXE_FW_RX_ALIGN_END (1 << BXE_RX_ALIGN_SHIFT) |

◆ BXE_FW_RX_ALIGN_START

| #define BXE_FW_RX_ALIGN_START (1 << BXE_RX_ALIGN_SHIFT) |

◆ bxe_fwd

| #define bxe_fwd | ( | sc, | |

| var | |||

| ) | (bxe_fwd_fp(sc)->var) |

◆ bxe_fwd_fp

◆ bxe_fwd_inner_sp_obj

| #define bxe_fwd_inner_sp_obj | ( | sc | ) | (&sc->sp_objs[FWD_IDX(sc)]) |

◆ bxe_fwd_sp_obj

| #define bxe_fwd_sp_obj | ( | sc, | |

| var | |||

| ) | (bxe_fwd_inner_sp_obj(sc)->var) |

◆ bxe_fwd_txdata

| #define bxe_fwd_txdata | ( | fp | ) | (fp->txdata_ptr[FIRST_TX_COS_INDEX]) |

◆ BXE_FWMB_LOCK

◆ BXE_FWMB_LOCK_ASSERT

| #define BXE_FWMB_LOCK_ASSERT | ( | sc | ) | mtx_assert(&sc->fwmb_mtx, MA_OWNED) |

◆ BXE_FWMB_UNLOCK

◆ BXE_GRC_RSV

| #define BXE_GRC_RSV |

◆ BXE_GRC_TIMEOUT

| #define BXE_GRC_TIMEOUT GENERAL_ATTEN_OFFSET(LATCHED_ATTN_TIMEOUT_GRC) |

◆ BXE_IGU_STAS_MSG_PF_CNT

◆ BXE_IGU_STAS_MSG_VF_CNT

◆ BXE_IOC_RD_NVRAM

◆ BXE_IOC_STATS_SHOW_CNT

◆ BXE_IOC_STATS_SHOW_NUM

◆ BXE_IOC_STATS_SHOW_STR

◆ BXE_IOC_WR_NVRAM

◆ BXE_L2_CID_COUNT

| #define BXE_L2_CID_COUNT | ( | sc | ) | (BXE_NUM_ETH_QUEUES(sc) * ECORE_MULTI_TX_COS + 2 * CNIC_SUPPORT(sc)) |

◆ BXE_L2_MAX_CID

| #define BXE_L2_MAX_CID | ( | sc | ) | (BXE_MAX_RSS_COUNT(sc) * ECORE_MULTI_TX_COS + 2 * CNIC_SUPPORT(sc)) |

◆ BXE_MAX_MULTICAST

◆ BXE_MAX_NUM_OF_VFS

◆ BXE_MAX_PRIORITY

◆ BXE_MAX_RSS_COUNT

| #define BXE_MAX_RSS_COUNT | ( | sc | ) | ((sc)->igu_sb_cnt - CNIC_SUPPORT(sc)) |

◆ BXE_MAX_SEGMENTS

◆ BXE_MC_ASSERT_BITS

| #define BXE_MC_ASSERT_BITS |

◆ BXE_MCAST_LOCK

◆ BXE_MCAST_LOCK_ASSERT

| #define BXE_MCAST_LOCK_ASSERT | ( | sc | ) | mtx_assert(&sc->mcast_mtx, MA_OWNED) |

◆ BXE_MCAST_UNLOCK

◆ BXE_MCP_ASSERT

| #define BXE_MCP_ASSERT GENERAL_ATTEN_OFFSET(MCP_FATAL_ASSERT_ATTENTION_BIT) |

◆ BXE_MF_FUNC_DIS

◆ BXE_MSI_CAPABLE_FLAG

◆ BXE_MSIX_CAPABLE_FLAG

◆ BXE_NO_FCOE

◆ BXE_NO_ISCSI

◆ BXE_NO_MCP_FLAG

◆ BXE_NO_PULSE

◆ BXE_NOMCP

| #define BXE_NOMCP | ( | sc | ) | (sc->flags & BXE_NO_MCP_FLAG) |

◆ BXE_NUM_ETH_QUEUES

| #define BXE_NUM_ETH_QUEUES | ( | sc | ) | BXE_NUM_QUEUES(sc) |

◆ BXE_NUM_NON_CNIC_QUEUES

| #define BXE_NUM_NON_CNIC_QUEUES | ( | sc | ) | BXE_NUM_QUEUES(sc) |

◆ BXE_NUM_QUEUES

◆ BXE_NUM_RX_QUEUES

| #define BXE_NUM_RX_QUEUES | ( | sc | ) | BXE_NUM_QUEUES(sc) |

◆ BXE_ONE_PORT

| #define BXE_ONE_PORT | ( | sc | ) | (sc->flags & BXE_ONE_PORT_FLAG) |

◆ BXE_ONE_PORT_FLAG

◆ bxe_ooo

| #define bxe_ooo | ( | sc, | |

| var | |||

| ) | (bxe_ooo_fp(sc)->var) |

◆ bxe_ooo_fp

◆ bxe_ooo_inner_sp_obj

| #define bxe_ooo_inner_sp_obj | ( | sc | ) | (&sc->sp_objs[OOO_IDX(sc)]) |

◆ bxe_ooo_sp_obj

| #define bxe_ooo_sp_obj | ( | sc, | |

| var | |||

| ) | (bxe_ooo_inner_sp_obj(sc)->var) |

◆ bxe_panic

| #define bxe_panic | ( | sc, | |

| msg | |||

| ) | device_printf((sc)->dev, "%s (%s,%d)\n", __FUNCTION__, __FILE__, __LINE__); |

◆ BXE_PCIE_CAPABLE_FLAG

◆ BXE_PHY_LOCK

◆ BXE_PHY_LOCK_ASSERT

| #define BXE_PHY_LOCK_ASSERT | ( | sc | ) | mtx_assert(&sc->port.phy_mtx, MA_OWNED) |

◆ BXE_PHY_UNLOCK

◆ BXE_PM_CAPABLE_FLAG

◆ BXE_PMF_LINK_ASSERT

| #define BXE_PMF_LINK_ASSERT | ( | sc | ) | GENERAL_ATTEN_OFFSET(LINK_SYNC_ATTENTION_BIT_FUNC_0 + SC_FUNC(sc)) |

◆ BXE_PRINT_LOCK

◆ BXE_PRINT_LOCK_ASSERT

| #define BXE_PRINT_LOCK_ASSERT | ( | sc | ) | mtx_assert(&sc->print_mtx, MA_OWNED) |

◆ BXE_PRINT_UNLOCK

◆ BXE_PXP_DRAM_ALIGN

| #define BXE_PXP_DRAM_ALIGN (BXE_RX_ALIGN_SHIFT - 5) /* XXX ??? */ |

◆ BXE_RECOVERY_DONE

◆ BXE_RECOVERY_FAILED

◆ BXE_RECOVERY_INIT

◆ BXE_RECOVERY_NIC_LOADING

◆ BXE_RECOVERY_WAIT

◆ BXE_RX_ALIGN_SHIFT

◆ BXE_RX_MODE_ALLMULTI

◆ BXE_RX_MODE_NONE

◆ BXE_RX_MODE_NORMAL

◆ BXE_RX_MODE_PROMISC

◆ BXE_SET_ERROR_BIT

| #define BXE_SET_ERROR_BIT | ( | sc, | |

| error | |||

| ) |

◆ BXE_SET_FLOWID

| #define BXE_SET_FLOWID | ( | m | ) | M_HASHTYPE_SET(m, M_HASHTYPE_OPAQUE) |

◆ BXE_SP

◆ BXE_SP_LOCK

◆ BXE_SP_LOCK_ASSERT

| #define BXE_SP_LOCK_ASSERT | ( | sc | ) | mtx_assert(&sc->sp_mtx, MA_OWNED) |

◆ BXE_SP_MAPPING

| #define BXE_SP_MAPPING | ( | sc, | |

| var | |||

| ) | (sc->sp_dma.paddr + offsetof(struct bxe_slowpath, var)) |

◆ BXE_SP_OBJ

◆ BXE_SP_UNLOCK

◆ BXE_STATE_CLOSED

◆ BXE_STATE_CLOSING_WAITING_DELETE

◆ BXE_STATE_CLOSING_WAITING_HALT

◆ BXE_STATE_CLOSING_WAITING_UNLOAD

◆ BXE_STATE_DIAG

◆ BXE_STATE_DISABLED

◆ BXE_STATE_ERROR

◆ BXE_STATE_OPEN

◆ BXE_STATE_OPENING_WAITING_LOAD

◆ BXE_STATE_OPENING_WAITING_PORT

◆ BXE_STATS_LOCK

◆ BXE_STATS_LOCK_ASSERT

| #define BXE_STATS_LOCK_ASSERT | ( | sc | ) | mtx_assert(&sc->stats_mtx, MA_OWNED) |

◆ BXE_STATS_UNLOCK

◆ BXE_SWCID_MASK

| #define BXE_SWCID_MASK ((0x1 << BXE_SWCID_SHIFT) - 1) |

◆ BXE_SWCID_SHIFT

◆ BXE_TPA_STATE_START

◆ BXE_TPA_STATE_STOP

◆ BXE_TSO_MAX_SEG_SIZE

◆ BXE_TSO_MAX_SEGMENTS

◆ BXE_TSO_MAX_SIZE

| #define BXE_TSO_MAX_SIZE (65535 + sizeof(struct ether_vlan_header)) |

◆ BXE_TSO_SPLIT_BD

◆ BXE_TX_CLEANUP_THRESHOLD

| #define BXE_TX_CLEANUP_THRESHOLD (TX_BD_USABLE / 8) |

◆ BXE_TX_SWITCHING

◆ BXE_TX_TIMEOUT

◆ BXE_VALID_FLOWID

| #define BXE_VALID_FLOWID | ( | m | ) | (M_HASHTYPE_GET(m) != M_HASHTYPE_NONE) |

◆ BXE_VF_CID_WND

◆ BXE_VF_CIDS

| #define BXE_VF_CIDS (BXE_MAX_NUM_OF_VFS * BXE_CIDS_PER_VF) |

◆ BXE_VF_ID_INVALID

◆ CATC_TRIGGER

| #define CATC_TRIGGER | ( | sc, | |

| data | |||

| ) | REG_WR((sc), 0x2000, (data)); |

◆ CATC_TRIGGER_START

| #define CATC_TRIGGER_START | ( | sc | ) | CATC_TRIGGER((sc), 0xcafecafe) |

◆ CDU_ILT_PAGE_SZ

| #define CDU_ILT_PAGE_SZ (8192 << CDU_ILT_PAGE_SZ_HW) /* 32K */ |

◆ CDU_ILT_PAGE_SZ_HW

◆ CHIP_2_PORT_MODE

◆ CHIP_4_PORT_MODE

◆ CHIP_BOND_ID

| #define CHIP_BOND_ID | ( | sc | ) | ((sc->devinfo.chip_id) & 0x0000000f) |

◆ CHIP_ID

◆ CHIP_INT_MODE_IS_BC

| #define CHIP_INT_MODE_IS_BC | ( | sc | ) | (!CHIP_INT_MODE_IS_NBC(sc)) |

◆ CHIP_INT_MODE_IS_NBC

| #define CHIP_INT_MODE_IS_NBC | ( | sc | ) |

◆ CHIP_IS_57710

| #define CHIP_IS_57710 | ( | sc | ) | (CHIP_NUM(sc) == CHIP_NUM_57710) |

◆ CHIP_IS_57711

| #define CHIP_IS_57711 | ( | sc | ) | (CHIP_NUM(sc) == CHIP_NUM_57711) |

◆ CHIP_IS_57711E

| #define CHIP_IS_57711E | ( | sc | ) | (CHIP_NUM(sc) == CHIP_NUM_57711E) |

◆ CHIP_IS_57712

| #define CHIP_IS_57712 | ( | sc | ) | (CHIP_NUM(sc) == CHIP_NUM_57712) |

◆ CHIP_IS_57712_MF

| #define CHIP_IS_57712_MF | ( | sc | ) | (CHIP_NUM(sc) == CHIP_NUM_57712_MF) |

◆ CHIP_IS_57712_VF

| #define CHIP_IS_57712_VF | ( | sc | ) | (CHIP_NUM(sc) == CHIP_NUM_57712_VF) |

◆ CHIP_IS_57800

| #define CHIP_IS_57800 | ( | sc | ) | (CHIP_NUM(sc) == CHIP_NUM_57800) |

◆ CHIP_IS_57800_MF

| #define CHIP_IS_57800_MF | ( | sc | ) | (CHIP_NUM(sc) == CHIP_NUM_57800_MF) |

◆ CHIP_IS_57800_VF

| #define CHIP_IS_57800_VF | ( | sc | ) | (CHIP_NUM(sc) == CHIP_NUM_57800_VF) |

◆ CHIP_IS_57810

| #define CHIP_IS_57810 | ( | sc | ) | (CHIP_NUM(sc) == CHIP_NUM_57810) |

◆ CHIP_IS_57810_MF

| #define CHIP_IS_57810_MF | ( | sc | ) | (CHIP_NUM(sc) == CHIP_NUM_57810_MF) |

◆ CHIP_IS_57810_VF

| #define CHIP_IS_57810_VF | ( | sc | ) | (CHIP_NUM(sc) == CHIP_NUM_57810_VF) |

◆ CHIP_IS_57811

| #define CHIP_IS_57811 | ( | sc | ) | (CHIP_NUM(sc) == CHIP_NUM_57811) |

◆ CHIP_IS_57811_MF

| #define CHIP_IS_57811_MF | ( | sc | ) | (CHIP_NUM(sc) == CHIP_NUM_57811_MF) |

◆ CHIP_IS_57811_VF

| #define CHIP_IS_57811_VF | ( | sc | ) | (CHIP_NUM(sc) == CHIP_NUM_57811_VF) |

◆ CHIP_IS_57840

| #define CHIP_IS_57840 | ( | sc | ) |

◆ CHIP_IS_57840_MF

| #define CHIP_IS_57840_MF | ( | sc | ) |

◆ CHIP_IS_57840_VF

| #define CHIP_IS_57840_VF | ( | sc | ) | (CHIP_NUM(sc) == CHIP_NUM_57840_VF) |

◆ CHIP_IS_E1

| #define CHIP_IS_E1 | ( | sc | ) | (CHIP_NUM(sc) == CHIP_NUM_57710) |

◆ CHIP_IS_E1H

| #define CHIP_IS_E1H | ( | sc | ) |

◆ CHIP_IS_E1x

| #define CHIP_IS_E1x | ( | sc | ) |

◆ CHIP_IS_E2

| #define CHIP_IS_E2 | ( | sc | ) |

◆ CHIP_IS_E2E3

| #define CHIP_IS_E2E3 | ( | sc | ) |

◆ CHIP_IS_E3

| #define CHIP_IS_E3 | ( | sc | ) |

◆ CHIP_IS_E3A0

| #define CHIP_IS_E3A0 | ( | sc | ) |

◆ CHIP_IS_E3B0

| #define CHIP_IS_E3B0 | ( | sc | ) |

◆ CHIP_IS_MF_CAP

| #define CHIP_IS_MF_CAP | ( | sc | ) |

◆ CHIP_IS_MODE_4_PORT

| #define CHIP_IS_MODE_4_PORT | ( | sc | ) | (CHIP_PORT_MODE(sc) == CHIP_4_PORT_MODE) |

◆ CHIP_METAL

| #define CHIP_METAL | ( | sc | ) | ((sc->devinfo.chip_id) & 0x00000ff0) |

◆ CHIP_NUM

◆ CHIP_NUM_57710

◆ CHIP_NUM_57711

◆ CHIP_NUM_57711E

◆ CHIP_NUM_57712

◆ CHIP_NUM_57712_MF

◆ CHIP_NUM_57712_VF

◆ CHIP_NUM_57800

◆ CHIP_NUM_57800_MF

◆ CHIP_NUM_57800_VF

◆ CHIP_NUM_57810

◆ CHIP_NUM_57810_MF

◆ CHIP_NUM_57810_VF

◆ CHIP_NUM_57811

◆ CHIP_NUM_57811_MF

◆ CHIP_NUM_57811_VF

◆ CHIP_NUM_57840_2_20

◆ CHIP_NUM_57840_4_10

◆ CHIP_NUM_57840_MF

◆ CHIP_NUM_57840_OBS

◆ CHIP_NUM_57840_OBS_MF

◆ CHIP_NUM_57840_VF

◆ CHIP_PORT_MODE

◆ CHIP_PORT_MODE_NONE

◆ CHIP_REV

| #define CHIP_REV | ( | sc | ) | ((sc)->devinfo.chip_id & CHIP_REV_MASK) |

◆ CHIP_REV_Ax

| #define CHIP_REV_Ax (0x0 << CHIP_REV_SHIFT) |

◆ CHIP_REV_Bx

| #define CHIP_REV_Bx (0x1 << CHIP_REV_SHIFT) |

◆ CHIP_REV_Cx

| #define CHIP_REV_Cx (0x2 << CHIP_REV_SHIFT) |

◆ CHIP_REV_IS_ASIC

| #define CHIP_REV_IS_ASIC | ( | sc | ) | (!CHIP_REV_IS_SLOW(sc)) |

◆ CHIP_REV_IS_EMUL

| #define CHIP_REV_IS_EMUL | ( | sc | ) | (CHIP_REV_IS_SLOW(sc) && !(CHIP_REV(sc) & 0x00001000)) |

◆ CHIP_REV_IS_FPGA

| #define CHIP_REV_IS_FPGA | ( | sc | ) | (CHIP_REV_IS_SLOW(sc) && (CHIP_REV(sc) & 0x00001000)) |

◆ CHIP_REV_IS_SLOW

◆ CHIP_REV_MASK

| #define CHIP_REV_MASK (0xF << CHIP_REV_SHIFT) |

◆ CHIP_REV_SHIFT

◆ CHIP_TQ_NONE

◆ CHIP_TQ_REINIT

◆ CHIP_TQ_START

◆ CHIP_TQ_STOP

◆ CID_TO_FP

| #define CID_TO_FP | ( | cid, | |

| sc | |||

| ) | ((cid) % BXE_NUM_NON_CNIC_QUEUES(sc)) |

◆ CMNG_FNS_MINMAX

◆ CMNG_FNS_NONE

◆ CNIC_CID_MAX

| #define CNIC_CID_MAX (CNIC_ISCSI_CID_MAX + CNIC_FCOE_CID_MAX) |

◆ CNIC_ENABLED

◆ CNIC_FCOE_CID_MAX

◆ CNIC_ILT_LINES

| #define CNIC_ILT_LINES DIV_ROUND_UP(CNIC_CID_MAX, ILT_PAGE_CIDS) |

◆ CNIC_ISCSI_CID_MAX

◆ CNIC_LOADED

◆ CNIC_SUPPORT

◆ CONFIGURE_NIC_MODE

| #define CONFIGURE_NIC_MODE | ( | sc | ) | (!CHIP_IS_E1x(sc) && !CNIC_ENABLED(sc)) |

◆ CQE_BD_REL

| #define CQE_BD_REL |

◆ CQE_CMD

| #define CQE_CMD | ( | x | ) | (le32toh(x) >> COMMON_RAMROD_ETH_RX_CQE_CMD_ID_SHIFT) |

◆ CQE_TYPE

| #define CQE_TYPE | ( | cqe_fp_flags | ) | ((cqe_fp_flags) & ETH_FAST_PATH_RX_CQE_TYPE) |

◆ CQE_TYPE_FAST

| #define CQE_TYPE_FAST | ( | cqe_type | ) | ((cqe_type) == RX_ETH_CQE_TYPE_ETH_FASTPATH) |

◆ CQE_TYPE_SLOW

| #define CQE_TYPE_SLOW | ( | cqe_type | ) | ((cqe_type) == RX_ETH_CQE_TYPE_ETH_RAMROD) |

◆ CQE_TYPE_START

| #define CQE_TYPE_START | ( | cqe_type | ) | ((cqe_type) == RX_ETH_CQE_TYPE_ETH_START_AGG) |

◆ CQE_TYPE_STOP

| #define CQE_TYPE_STOP | ( | cqe_type | ) | ((cqe_type) == RX_ETH_CQE_TYPE_ETH_STOP_AGG) |

◆ DBASSERT

| #define DBASSERT | ( | sc, | |

| exp, | |||

| msg | |||

| ) |

◆ DBG_ALL

◆ DBG_ASSERT

◆ DBG_INTR

◆ DBG_IOCTL

◆ DBG_LOAD

◆ DBG_LRO

◆ DBG_MBUF

◆ DBG_PHY

◆ DBG_REGS

◆ DBG_RX

◆ DBG_SP

◆ DBG_STATS

◆ DBG_TX

◆ DEF_MIN_RATE

◆ DEF_SB_ID

| #define DEF_SB_ID HC_SP_SB_ID |

◆ DEF_SB_IGU_ID

◆ DIV_ROUND_UP

◆ DMAE_C_DST

◆ DMAE_C_SRC

◆ DMAE_CMD_C_DST_GRC

| #define DMAE_CMD_C_DST_GRC (DMAE_COMP_GRC << DMAE_CMD_C_DST_SHIFT) |

◆ DMAE_CMD_C_DST_PCI

| #define DMAE_CMD_C_DST_PCI (DMAE_COMP_PCI << DMAE_CMD_C_DST_SHIFT) |

◆ DMAE_CMD_DST_GRC

| #define DMAE_CMD_DST_GRC (DMAE_DST_GRC << DMAE_CMD_DST_SHIFT) |

◆ DMAE_CMD_DST_PCI

| #define DMAE_CMD_DST_PCI (DMAE_DST_PCI << DMAE_CMD_DST_SHIFT) |

◆ DMAE_CMD_ENDIANITY_B_DW_SWAP

| #define DMAE_CMD_ENDIANITY_B_DW_SWAP (3 << DMAE_CMD_ENDIANITY_SHIFT) |

◆ DMAE_CMD_ENDIANITY_B_SWAP

| #define DMAE_CMD_ENDIANITY_B_SWAP (1 << DMAE_CMD_ENDIANITY_SHIFT) |

◆ DMAE_CMD_ENDIANITY_DW_SWAP

| #define DMAE_CMD_ENDIANITY_DW_SWAP (2 << DMAE_CMD_ENDIANITY_SHIFT) |

◆ DMAE_CMD_ENDIANITY_NO_SWAP

| #define DMAE_CMD_ENDIANITY_NO_SWAP (0 << DMAE_CMD_ENDIANITY_SHIFT) |

◆ DMAE_CMD_PORT_0

◆ DMAE_CMD_PORT_1

| #define DMAE_CMD_PORT_1 DMAE_CMD_PORT |

◆ DMAE_CMD_SRC_GRC

| #define DMAE_CMD_SRC_GRC (DMAE_SRC_GRC << DMAE_CMD_SRC_SHIFT) |

◆ DMAE_CMD_SRC_PCI

| #define DMAE_CMD_SRC_PCI (DMAE_SRC_PCI << DMAE_CMD_SRC_SHIFT) |

◆ DMAE_COM_SET_ERR

◆ DMAE_COMP_GRC

◆ DMAE_COMP_PCI

◆ DMAE_COMP_REGULAR

◆ DMAE_COMP_VAL

| #define DMAE_COMP_VAL 0x60d0d0ae /* E2 and beyond, upper bit indicates error */ |

◆ DMAE_DST_GRC

◆ DMAE_DST_NONE

◆ DMAE_DST_PCI

◆ DMAE_DST_PF

◆ DMAE_DST_VF

◆ DMAE_LEN32_RD_MAX

◆ DMAE_LEN32_WR_MAX

| #define DMAE_LEN32_WR_MAX | ( | sc | ) | (CHIP_IS_E1(sc) ? 0x400 : 0x2000) |

◆ DMAE_NOT_RDY

◆ DMAE_PCI_ERR_FLAG

◆ DMAE_PCI_ERROR

◆ DMAE_READY

◆ DMAE_SRC_GRC

◆ DMAE_SRC_PCI

◆ DMAE_SRC_PF

◆ DMAE_SRC_VF

◆ DMAE_TIMEOUT

◆ DOORBELL

| #define DOORBELL | ( | sc, | |

| cid, | |||

| val | |||

| ) |

◆ DPM_TRIGGER_TYPE

◆ DROPLESS_FC_HEADROOM

◆ DUPLEX_UNKNOWN

◆ EQ_DESC

| #define EQ_DESC | ( | x | ) | ((x) & EQ_DESC_MASK) |

◆ EQ_DESC_CNT_PAGE

| #define EQ_DESC_CNT_PAGE (BCM_PAGE_SIZE / sizeof(union event_ring_elem)) |

◆ EQ_DESC_MASK

| #define EQ_DESC_MASK (NUM_EQ_DESC - 1) |

◆ EQ_DESC_MAX_PAGE

| #define EQ_DESC_MAX_PAGE (EQ_DESC_CNT_PAGE - 1) |

◆ ETH_HLEN

◆ ETH_MAX_JUMBO_PACKET_SIZE

◆ ETH_MAX_PACKET_SIZE

◆ ETH_MAX_TPA_HEADER_SIZE

◆ ETH_MIN_PACKET_SIZE

◆ ETH_OVERHEAD

◆ FAIR_MEM

◆ FCOE_IDX

| #define FCOE_IDX | ( | sc | ) | (BXE_NUM_NON_CNIC_QUEUES(sc) + FCOE_IDX_OFFSET) |

◆ FIRST_ABS_FUNC_IN_PORT

| #define FIRST_ABS_FUNC_IN_PORT | ( | sc | ) |

◆ FIRST_TX_COS_INDEX

◆ FIRST_TX_ONLY_COS_INDEX

◆ FOR_EACH_CNIC_QUEUE

| #define FOR_EACH_CNIC_QUEUE | ( | sc, | |

| var | |||

| ) |

◆ FOR_EACH_COS_IN_TX_QUEUE

| #define FOR_EACH_COS_IN_TX_QUEUE | ( | sc, | |

| var | |||

| ) | for ((var) = 0; (var) < (sc)->max_cos; (var)++) |

◆ FOR_EACH_ETH_QUEUE

| #define FOR_EACH_ETH_QUEUE | ( | sc, | |

| var | |||

| ) | for ((var) = 0; (var) < BXE_NUM_ETH_QUEUES(sc); (var)++) |

◆ FOR_EACH_NONDEFAULT_ETH_QUEUE

| #define FOR_EACH_NONDEFAULT_ETH_QUEUE | ( | sc, | |

| var | |||

| ) | for ((var) = 1; (var) < BXE_NUM_ETH_QUEUES(sc); (var)++) |

◆ FOR_EACH_NONDEFAULT_QUEUE

| #define FOR_EACH_NONDEFAULT_QUEUE | ( | sc, | |

| var | |||

| ) | for ((var) = 1; (var) < BXE_NUM_QUEUES(sc); (var)++) |

◆ FOR_EACH_QUEUE

| #define FOR_EACH_QUEUE | ( | sc, | |

| var | |||

| ) | for ((var) = 0; (var) < BXE_NUM_QUEUES(sc); (var)++) |

◆ FOREACH_ABS_FUNC_IN_PORT

| #define FOREACH_ABS_FUNC_IN_PORT | ( | sc, | |

| i | |||

| ) |

◆ FP_CL_ID

◆ FP_IDX

◆ FP_SB_MAX_E1x

◆ FP_SB_MAX_E2

| #define FP_SB_MAX_E2 HC_SB_MAX_SB_E2 |

◆ FUNC_FLG_LEADING

◆ FUNC_FLG_RSS

◆ FUNC_FLG_SPQ

◆ FUNC_FLG_STATS

◆ FUNC_FLG_TPA

◆ FUNC_ID

◆ FUNC_ILT_BASE

| #define FUNC_ILT_BASE | ( | func | ) | (func * ILT_PER_FUNC) |

◆ FW_BUF_SIZE

◆ FW_DROP_LEVEL

| #define FW_DROP_LEVEL | ( | sc | ) | (3 + MAX_SPQ_PENDING + MAX_AGG_QS(sc)) |

◆ FW_PREFETCH_CNT

◆ FWD_IDX

| #define FWD_IDX | ( | sc | ) | (BXE_NUM_NON_CNIC_QUEUES(sc) + FWD_IDX_OFFSET) |

◆ GET_FIELD

| #define GET_FIELD | ( | value, | |

| fname | |||

| ) | (((value) & (fname##_MASK)) >> (fname##_SHIFT)) |

◆ GET_FLAG

| #define GET_FLAG | ( | value, | |

| mask | |||

| ) | (((value) & (mask)) >> (mask##_SHIFT)) |

◆ GET_NUM_VFS_PER_PATH

◆ GET_NUM_VFS_PER_PF

◆ GPIO_2_FUNC

◆ GPIO_3_FUNC

◆ GPIO_4_FUNC

◆ GUNZIP_BUF

◆ GUNZIP_OUTLEN

◆ GUNZIP_PHYS

◆ HC_INDEX_ETH_FIRST_TX_CQ_CONS

| #define HC_INDEX_ETH_FIRST_TX_CQ_CONS HC_INDEX_ETH_TX_CQ_CONS_COS0 |

◆ HC_INDEX_ETH_RX_CQ_CONS

◆ HC_INDEX_ETH_TX_CQ_CONS_COS0

◆ HC_INDEX_ETH_TX_CQ_CONS_COS1

◆ HC_INDEX_ETH_TX_CQ_CONS_COS2

◆ HC_INDEX_OOO_TX_CQ_CONS

◆ HC_SEG_ACCESS_ATTN

◆ HC_SEG_ACCESS_DEF

◆ HC_SEG_ACCESS_NORM

◆ HC_SP_INDEX_EQ_CONS

◆ HC_SP_INDEX_ETH_DEF_CONS

◆ HC_SP_INDEX_ETH_FCOE_RX_CQ_CONS

◆ HC_SP_INDEX_ETH_FCOE_TX_CQ_CONS

◆ HC_SP_INDEX_ETH_ISCSI_CQ_CONS

◆ HC_SP_INDEX_ETH_ISCSI_RX_CQ_CONS

◆ HILO_U64

◆ HW_CID

| #define HW_CID | ( | sc, | |

| x | |||

| ) | ((SC_PORT(sc) << 23) | (SC_VN(sc) << BXE_SWCID_SHIFT) | (x)) |

◆ ilog2

◆ ILT_MAX_L2_LINES

◆ ILT_MAX_LINES

◆ ILT_NUM_PAGE_ENTRIES

◆ ILT_PAGE_CIDS

| #define ILT_PAGE_CIDS (CDU_ILT_PAGE_SZ / sizeof(union cdu_context)) |

◆ ILT_PER_FUNC

| #define ILT_PER_FUNC (ILT_NUM_PAGE_ENTRIES / 8) |

◆ INIT_CSEM_INT_TABLE_DATA

| #define INIT_CSEM_INT_TABLE_DATA | ( | sc | ) | (sc->csem_int_table_data) |

◆ INIT_CSEM_PRAM_DATA

◆ INIT_DATA

◆ INIT_DMAE_C

| #define INIT_DMAE_C | ( | sc | ) | ((SC_PORT(sc) * MAX_DMAE_C_PER_PORT) + SC_VN(sc)) |

◆ INIT_MODE_FLAGS

◆ INIT_OPS

◆ INIT_OPS_OFFSETS

◆ INIT_TSEM_INT_TABLE_DATA

| #define INIT_TSEM_INT_TABLE_DATA | ( | sc | ) | (sc->tsem_int_table_data) |

◆ INIT_TSEM_PRAM_DATA

◆ INIT_USEM_INT_TABLE_DATA

| #define INIT_USEM_INT_TABLE_DATA | ( | sc | ) | (sc->usem_int_table_data) |

◆ INIT_USEM_PRAM_DATA

◆ INIT_XSEM_INT_TABLE_DATA

| #define INIT_XSEM_INT_TABLE_DATA | ( | sc | ) | (sc->xsem_int_table_data) |

◆ INIT_XSEM_PRAM_DATA

◆ INT_BLOCK_HC

◆ INT_BLOCK_IGU

◆ INT_BLOCK_MODE_BW_COMP

◆ INT_BLOCK_MODE_NORMAL

◆ INTR_MODE_INTX

◆ INTR_MODE_MSI

◆ INTR_MODE_MSIX

◆ INVALID_VIF_ID

◆ IS_ETH_FP

| #define IS_ETH_FP | ( | fp | ) | ((fp)->index < BXE_NUM_ETH_QUEUES((fp)->sc)) |

◆ IS_FCOE_FP

◆ IS_FCOE_IDX

◆ IS_FWD_FP

◆ IS_FWD_IDX

◆ IS_MF

| #define IS_MF | ( | sc | ) |

◆ IS_MF_AFEX

| #define IS_MF_AFEX | ( | sc | ) |

◆ IS_MF_AFEX_MODE

| #define IS_MF_AFEX_MODE | ( | sc | ) | IS_MF_AFEX(sc) |

◆ IS_MF_SD

| #define IS_MF_SD | ( | sc | ) |

◆ IS_MF_SD_MODE

◆ IS_MF_SI

| #define IS_MF_SI | ( | sc | ) |

◆ IS_MF_SI_MODE

◆ IS_MULTI_VNIC

| #define IS_MULTI_VNIC | ( | sc | ) | ((sc)->devinfo.mf_info.multi_vnics_mode) |

◆ IS_OOO_FP

◆ IS_OOO_IDX

◆ IS_PF

◆ IS_SRIOV

◆ IS_VF

| #define IS_VF | ( | sc | ) |

◆ L2_ILT_LINES

| #define L2_ILT_LINES | ( | sc | ) | (DIV_ROUND_UP(BXE_L2_CID_COUNT(sc), ILT_PAGE_CIDS)) |

◆ LITTLE_ENDIAN

◆ LOAD_DIAG

◆ LOAD_LOOPBACK_EXT

◆ LOAD_NORMAL

◆ LOAD_OPEN

◆ MAX_AGG_QS

| #define MAX_AGG_QS | ( | sc | ) |

◆ MAX_BARS

◆ MAX_DMAE_C

◆ MAX_DMAE_C_PER_PORT

◆ MAX_DYNAMIC_ATTN_GRPS

◆ MAX_EQ_AVAIL

| #define MAX_EQ_AVAIL (EQ_DESC_MAX_PAGE * NUM_EQ_PAGES - 2) |

◆ MAX_FUNC_NUM

◆ MAX_IGU_ATTN_ACK_TO

◆ MAX_MSI_VECTOR

◆ MAX_RSS_CHAINS

◆ MAX_SP_DESC_CNT

| #define MAX_SP_DESC_CNT (SP_DESC_CNT - 1) |

◆ MAX_SPQ_PENDING

◆ MAX_VNIC_NUM

◆ MF_INFO_VALID_MAC

◆ MF_PROTO_SUPPORT_ETHERNET

◆ MF_PROTO_SUPPORT_FCOE

◆ MF_PROTO_SUPPORT_ISCSI

◆ MFCFG_ADDR

| #define MFCFG_ADDR | ( | sc, | |

| field | |||

| ) | (sc->devinfo.mf_cfg_base + offsetof(struct mf_cfg, field)) |

◆ MFCFG_RD

| #define MFCFG_RD | ( | sc, | |

| field | |||

| ) | REG_RD(sc, MFCFG_ADDR(sc, field)) |

◆ MFCFG_RD16

| #define MFCFG_RD16 | ( | sc, | |

| field | |||

| ) | REG_RD16(sc, MFCFG_ADDR(sc, field)) |

◆ MFCFG_WR

| #define MFCFG_WR | ( | sc, | |

| field, | |||

| val | |||

| ) | REG_WR(sc, MFCFG_ADDR(sc, field), val) |

◆ MIN_ABOVE_THRESH

◆ MIN_RES

◆ MIN_RX_AVAIL

| #define MIN_RX_AVAIL | ( | sc | ) | ((sc)->dropless_fc ? BD_TH_HI(sc) + 128 : 128) |

◆ MIN_RX_SIZE_NONTPA

| #define MIN_RX_SIZE_NONTPA | ( | sc | ) | (max(MIN_RX_SIZE_NONTPA_HW, MIN_RX_AVAIL(sc))) |

◆ MIN_RX_SIZE_NONTPA_HW

| #define MIN_RX_SIZE_NONTPA_HW ETH_MIN_RX_CQES_WITHOUT_TPA |

◆ MIN_RX_SIZE_TPA

| #define MIN_RX_SIZE_TPA | ( | sc | ) | (max(MIN_RX_SIZE_TPA_HW(sc), MIN_RX_AVAIL(sc))) |

◆ MIN_RX_SIZE_TPA_HW

| #define MIN_RX_SIZE_TPA_HW | ( | sc | ) |

◆ MULTI_MASK

◆ NEXT_EQ_IDX

| #define NEXT_EQ_IDX | ( | x | ) |

◆ NIV_ALLOWED_PRIORITIES

| #define NIV_ALLOWED_PRIORITIES | ( | sc | ) | ((sc)->devinfo.mf_info.niv_allowed_priorities) |

◆ NIV_DEFAULT_COS

| #define NIV_DEFAULT_COS | ( | sc | ) | ((sc)->devinfo.mf_info.niv_default_cos) |

◆ NIV_DEFAULT_VLAN

| #define NIV_DEFAULT_VLAN | ( | sc | ) | ((sc)->devinfo.mf_info.default_vlan) |

◆ NUM_BD_PG_REQ

| #define NUM_BD_PG_REQ | ( | sc | ) | ((NUM_BD_REQ(sc) + RX_BD_USABLE_PER_PAGE - 1) / RX_BD_USABLE_PER_PAGE) |

◆ NUM_BD_REQ

◆ NUM_EQ_DESC

| #define NUM_EQ_DESC (EQ_DESC_CNT_PAGE * NUM_EQ_PAGES) |

◆ NUM_EQ_PAGES

◆ NUM_RCQ_PG_REQ

| #define NUM_RCQ_PG_REQ | ( | sc | ) | ((NUM_RCQ_REQ(sc) + RCQ_USABLE_PER_PAGE - 1) / RCQ_USABLE_PER_PAGE) |

◆ NUM_RCQ_REQ

◆ NUM_SGE_PG_REQ

| #define NUM_SGE_PG_REQ | ( | sc | ) | ((NUM_SGE_REQ(sc) + RX_SGE_USABLE_PER_PAGE - 1) / RX_SGE_USABLE_PER_PAGE) |

◆ NUM_SGE_REQ

| #define NUM_SGE_REQ | ( | sc | ) | (MAX_AGG_QS(sc) + (BRB_SIZE(sc) - MAX_AGG_QS(sc)) / 2) |

◆ NVRAM_1MB_SIZE

◆ NVRAM_PAGE_SIZE

◆ NVRAM_TIMEOUT_COUNT

◆ ONCHIP_ADDR1

| #define ONCHIP_ADDR1 | ( | x | ) | ((uint32_t)(((uint64_t)x >> 12) & 0xFFFFFFFF)) |

◆ ONCHIP_ADDR2

| #define ONCHIP_ADDR2 | ( | x | ) | ((uint32_t)((1 << 20) | ((uint64_t)x >> 44))) |

◆ OOO_IDX

| #define OOO_IDX | ( | sc | ) | (BXE_NUM_NON_CNIC_QUEUES(sc) + OOO_IDX_OFFSET) |

◆ OVLAN

◆ PAGES_PER_SGE

| #define PAGES_PER_SGE (1 << PAGES_PER_SGE_SHIFT) |

◆ PAGES_PER_SGE_SHIFT

◆ PATH_ID

◆ PCI_ANY_ID

◆ PCI_PM_D0

◆ PCI_PM_D3hot

◆ PERIODIC_GO

◆ PERIODIC_STOP

◆ PFS_PER_PORT

| #define PFS_PER_PORT | ( | sc | ) | ((CHIP_PORT_MODE(sc) == CHIP_4_PORT_MODE) ? 2 : 4) |

◆ PMF_DMAE_C

| #define PMF_DMAE_C | ( | sc | ) | ((SC_PORT(sc) * MAX_DMAE_C_PER_PORT) + E1HVN_MAX) |

◆ PORT_AUI

◆ PORT_BNC

◆ PORT_DA

◆ PORT_FIBRE

◆ PORT_ID

◆ PORT_MII

◆ PORT_NONE

◆ PORT_OTHER

◆ PORT_TP

◆ QLOGIC_VENDORID

◆ QM_ARB_BYTES

◆ QM_CID_ROUND

◆ QM_ILT_PAGE_SZ

| #define QM_ILT_PAGE_SZ (4096 << QM_ILT_PAGE_SZ_HW) /* 4K */ |

◆ QM_ILT_PAGE_SZ_HW

◆ RCQ

◆ RCQ_IDX

| #define RCQ_IDX | ( | x | ) | ((x) & RCQ_USABLE_PER_PAGE) |

◆ RCQ_MAX

◆ RCQ_NEXT

| #define RCQ_NEXT | ( | x | ) |

◆ RCQ_NEXT_PAGE_DESC_CNT

◆ RCQ_NUM_PAGES

| #define RCQ_NUM_PAGES (RX_BD_NUM_PAGES * CQE_BD_REL) /* power of 2 */ |

◆ RCQ_PAGE

| #define RCQ_PAGE | ( | x | ) | (((x) & ~RCQ_USABLE_PER_PAGE) >> 7) |

◆ RCQ_TH_HI

| #define RCQ_TH_HI | ( | sc | ) | (RCQ_TH_LO(sc) + DROPLESS_FC_HEADROOM) |

◆ RCQ_TH_LO

| #define RCQ_TH_LO | ( | sc | ) |

◆ RCQ_TOTAL

| #define RCQ_TOTAL (RCQ_TOTAL_PER_PAGE * RCQ_NUM_PAGES) |

◆ RCQ_TOTAL_PER_PAGE

| #define RCQ_TOTAL_PER_PAGE (BCM_PAGE_SIZE / sizeof(union eth_rx_cqe)) |

◆ RCQ_USABLE

| #define RCQ_USABLE (RCQ_USABLE_PER_PAGE * RCQ_NUM_PAGES) |

◆ RCQ_USABLE_PER_PAGE

| #define RCQ_USABLE_PER_PAGE (RCQ_TOTAL_PER_PAGE - RCQ_NEXT_PAGE_DESC_CNT) |

◆ REG_RD

◆ REG_RD16

| #define REG_RD16 | ( | sc, | |

| offset | |||

| ) |

◆ REG_RD32

| #define REG_RD32 | ( | sc, | |

| offset | |||

| ) |

◆ REG_RD8

| #define REG_RD8 | ( | sc, | |

| offset | |||

| ) |

◆ REG_RD_DMAE

| #define REG_RD_DMAE | ( | sc, | |

| offset, | |||

| valp, | |||

| len32 | |||

| ) |

◆ REG_RD_DMAE_LEN

| #define REG_RD_DMAE_LEN | ( | sc, | |

| offset, | |||

| valp, | |||

| len32 | |||

| ) | REG_RD_DMAE(sc, offset, valp, len32) |

◆ REG_RD_IND

| #define REG_RD_IND | ( | sc, | |

| offset | |||

| ) | bxe_reg_rd_ind(sc, offset) |

◆ REG_WR

◆ REG_WR16

| #define REG_WR16 | ( | sc, | |

| offset, | |||

| val | |||

| ) |

◆ REG_WR32

| #define REG_WR32 | ( | sc, | |

| offset, | |||

| val | |||

| ) |

◆ REG_WR8

| #define REG_WR8 | ( | sc, | |

| offset, | |||

| val | |||

| ) |

◆ REG_WR_DMAE

| #define REG_WR_DMAE | ( | sc, | |

| offset, | |||

| valp, | |||

| len32 | |||

| ) |

◆ REG_WR_DMAE_LEN

| #define REG_WR_DMAE_LEN | ( | sc, | |

| offset, | |||

| valp, | |||

| len32 | |||

| ) | REG_WR_DMAE(sc, offset, valp, len32) |

◆ REG_WR_IND

| #define REG_WR_IND | ( | sc, | |

| offset, | |||

| val | |||

| ) | bxe_reg_wr_ind(sc, offset, val) |

◆ roundup

◆ RS_PERIODIC_TIMEOUT_USEC

◆ RX_BD

◆ RX_BD_IDX

| #define RX_BD_IDX | ( | x | ) | ((x) & RX_BD_PER_PAGE_MASK) |

◆ RX_BD_MAX

| #define RX_BD_MAX (RX_BD_TOTAL - 1) |

◆ RX_BD_NEXT

| #define RX_BD_NEXT | ( | x | ) |

◆ RX_BD_NEXT_PAGE_DESC_CNT

◆ RX_BD_NUM_PAGES

◆ RX_BD_PAGE

| #define RX_BD_PAGE | ( | x | ) | (((x) & ~RX_BD_PER_PAGE_MASK) >> 9) |

◆ RX_BD_PER_PAGE_MASK

| #define RX_BD_PER_PAGE_MASK (RX_BD_TOTAL_PER_PAGE - 1) |

◆ RX_BD_TOTAL

| #define RX_BD_TOTAL (RX_BD_TOTAL_PER_PAGE * RX_BD_NUM_PAGES) |

◆ RX_BD_TOTAL_PER_PAGE

| #define RX_BD_TOTAL_PER_PAGE (BCM_PAGE_SIZE / sizeof(struct eth_rx_bd)) |

◆ RX_BD_USABLE

| #define RX_BD_USABLE (RX_BD_USABLE_PER_PAGE * RX_BD_NUM_PAGES) |

◆ RX_BD_USABLE_PER_PAGE

| #define RX_BD_USABLE_PER_PAGE (RX_BD_TOTAL_PER_PAGE - RX_BD_NEXT_PAGE_DESC_CNT) |

◆ RX_SGE

| #define RX_SGE | ( | x | ) | ((x) & RX_SGE_MAX) |

◆ RX_SGE_MASK_ELEM_MASK

| #define RX_SGE_MASK_ELEM_MASK ((uint64_t)RX_SGE_MASK_ELEM_SZ - 1) |

◆ RX_SGE_MASK_ELEM_ONE_MASK

◆ RX_SGE_MASK_ELEM_SHIFT

◆ RX_SGE_MASK_ELEM_SZ

◆ RX_SGE_MASK_LEN

| #define RX_SGE_MASK_LEN ((RX_SGE_NUM_PAGES * RX_SGE_TOTAL_PER_PAGE) / RX_SGE_MASK_ELEM_SZ) |

◆ RX_SGE_MASK_LEN_MASK

| #define RX_SGE_MASK_LEN_MASK (RX_SGE_MASK_LEN - 1) |

◆ RX_SGE_MAX

| #define RX_SGE_MAX (RX_SGE_TOTAL - 1) |

◆ RX_SGE_NEXT

| #define RX_SGE_NEXT | ( | x | ) |

◆ RX_SGE_NEXT_MASK_ELEM

| #define RX_SGE_NEXT_MASK_ELEM | ( | el | ) | (((el) + 1) & RX_SGE_MASK_LEN_MASK) |

◆ RX_SGE_NEXT_PAGE_DESC_CNT

◆ RX_SGE_NUM_PAGES

◆ RX_SGE_ONES_MASK

| #define RX_SGE_ONES_MASK | ( | idx | ) | (((uint64_t)0x1 << (((idx) & RX_SGE_MASK_ELEM_MASK) + 1)) - 1) |

◆ RX_SGE_PER_PAGE_MASK

| #define RX_SGE_PER_PAGE_MASK (RX_SGE_TOTAL_PER_PAGE - 1) |

◆ RX_SGE_TOTAL

| #define RX_SGE_TOTAL (RX_SGE_TOTAL_PER_PAGE * RX_SGE_NUM_PAGES) |

◆ RX_SGE_TOTAL_PER_PAGE

| #define RX_SGE_TOTAL_PER_PAGE (BCM_PAGE_SIZE / sizeof(struct eth_rx_sge)) |

◆ RX_SGE_USABLE

| #define RX_SGE_USABLE (RX_SGE_USABLE_PER_PAGE * RX_SGE_NUM_PAGES) |

◆ RX_SGE_USABLE_PER_PAGE

| #define RX_SGE_USABLE_PER_PAGE (RX_SGE_TOTAL_PER_PAGE - RX_SGE_NEXT_PAGE_DESC_CNT) |

◆ SC_ABS_FUNC

◆ SC_FUNC

◆ SC_FW_MB_IDX