|

| enum | HAL_STATUS {

HAL_OK = 0

, HAL_ENXIO = 1

, HAL_ENOMEM = 2

, HAL_EIO = 3

,

HAL_EEMAGIC = 4

, HAL_EEVERSION = 5

, HAL_EELOCKED = 6

, HAL_EEBADSUM = 7

,

HAL_EEREAD = 8

, HAL_EEBADMAC = 9

, HAL_EESIZE = 10

, HAL_EEWRITE = 11

,

HAL_EINVAL = 12

, HAL_ENOTSUPP = 13

, HAL_ESELFTEST = 14

, HAL_EINPROGRESS = 15

,

HAL_EEBADREG = 16

, HAL_EEBADCC = 17

, HAL_INV_PMODE = 18

} |

| |

| enum | HAL_BOOL { AH_FALSE = 0

, AH_TRUE = 1

} |

| |

| enum | HAL_CAPABILITY_TYPE {

HAL_CAP_REG_DMN = 0

, HAL_CAP_CIPHER = 1

, HAL_CAP_TKIP_MIC = 2

, HAL_CAP_TKIP_SPLIT = 3

,

HAL_CAP_PHYCOUNTERS = 4

, HAL_CAP_DIVERSITY = 5

, HAL_CAP_KEYCACHE_SIZE = 6

, HAL_CAP_NUM_TXQUEUES = 7

,

HAL_CAP_VEOL = 9

, HAL_CAP_PSPOLL = 10

, HAL_CAP_DIAG = 11

, HAL_CAP_COMPRESSION = 12

,

HAL_CAP_BURST = 13

, HAL_CAP_FASTFRAME = 14

, HAL_CAP_TXPOW = 15

, HAL_CAP_TPC = 16

,

HAL_CAP_PHYDIAG = 17

, HAL_CAP_BSSIDMASK = 18

, HAL_CAP_MCAST_KEYSRCH = 19

, HAL_CAP_TSF_ADJUST = 20

,

HAL_CAP_WME_TKIPMIC = 22

, HAL_CAP_RFSILENT = 25

, HAL_CAP_TPC_ACK = 26

, HAL_CAP_TPC_CTS = 27

,

HAL_CAP_11D = 28

, HAL_CAP_PCIE_PS = 29

, HAL_CAP_HT = 30

, HAL_CAP_GTXTO = 31

,

HAL_CAP_FAST_CC = 32

, HAL_CAP_TX_CHAINMASK = 33

, HAL_CAP_RX_CHAINMASK = 34

, HAL_CAP_NUM_GPIO_PINS = 36

,

HAL_CAP_CST = 38

, HAL_CAP_RIFS_RX = 39

, HAL_CAP_RIFS_TX = 40

, HAL_CAP_FORCE_PPM = 41

,

HAL_CAP_RTS_AGGR_LIMIT = 42

, HAL_CAP_4ADDR_AGGR = 43

, HAL_CAP_DFS_DMN = 44

, HAL_CAP_EXT_CHAN_DFS = 45

,

HAL_CAP_COMBINED_RADAR_RSSI = 46

, HAL_CAP_AUTO_SLEEP = 48

, HAL_CAP_MBSSID_AGGR_SUPPORT = 49

, HAL_CAP_SPLIT_4KB_TRANS = 50

,

HAL_CAP_REG_FLAG = 51

, HAL_CAP_BB_RIFS_HANG = 52

, HAL_CAP_RIFS_RX_ENABLED = 53

, HAL_CAP_BB_DFS_HANG = 54

,

HAL_CAP_RX_STBC = 58

, HAL_CAP_TX_STBC = 59

, HAL_CAP_BT_COEX = 60

, HAL_CAP_DYNAMIC_SMPS = 61

,

HAL_CAP_DS = 67

, HAL_CAP_BB_RX_CLEAR_STUCK_HANG = 68

, HAL_CAP_MAC_HANG = 69

, HAL_CAP_MFP = 70

,

HAL_CAP_TS = 72

, HAL_CAP_ENHANCED_DMA_SUPPORT = 75

, HAL_CAP_NUM_TXMAPS = 76

, HAL_CAP_TXDESCLEN = 77

,

HAL_CAP_TXSTATUSLEN = 78

, HAL_CAP_RXSTATUSLEN = 79

, HAL_CAP_RXFIFODEPTH = 80

, HAL_CAP_RXBUFSIZE = 81

,

HAL_CAP_NUM_MR_RETRIES = 82

, HAL_CAP_OL_PWRCTRL = 84

, HAL_CAP_SPECTRAL_SCAN = 90

, HAL_CAP_BB_PANIC_WATCHDOG = 92

,

HAL_CAP_HT20_SGI = 96

, HAL_CAP_LDPC = 99

, HAL_CAP_RXTSTAMP_PREC = 100

, HAL_CAP_ANT_DIV_COMB = 105

,

HAL_CAP_PHYRESTART_CLR_WAR = 106

, HAL_CAP_ENTERPRISE_MODE = 107

, HAL_CAP_LDPCWAR = 108

, HAL_CAP_CHANNEL_SWITCH_TIME_USEC = 109

,

HAL_CAP_ENABLE_APM = 110

, HAL_CAP_PCIE_LCR_EXTSYNC_EN = 111

, HAL_CAP_PCIE_LCR_OFFSET = 112

, HAL_CAP_ENHANCED_DFS_SUPPORT = 117

,

HAL_CAP_MCI = 118

, HAL_CAP_SMARTANTENNA = 119

, HAL_CAP_TRAFFIC_FAST_RECOVER = 120

, HAL_CAP_TX_DIVERSITY = 121

,

HAL_CAP_CRDC = 122

, HAL_CAP_INTMIT = 229

, HAL_CAP_RXORN_FATAL = 230

, HAL_CAP_BB_HANG = 235

,

HAL_CAP_INTRMASK = 237

, HAL_CAP_BSSIDMATCH = 238

, HAL_CAP_STREAMS = 239

, HAL_CAP_RXDESC_SELFLINK = 242

,

HAL_CAP_BB_READ_WAR = 244

, HAL_CAP_SERIALISE_WAR = 245

, HAL_CAP_ENFORCE_TXOP = 246

, HAL_CAP_RX_LNA_MIXING = 247

,

HAL_CAP_DO_MYBEACON = 248

, HAL_CAP_TOA_LOCATIONING = 249

, HAL_CAP_TXTSTAMP_PREC = 250

} |

| |

| enum | HAL_LED_STATE {

HAL_LED_INIT = 0

, HAL_LED_SCAN = 1

, HAL_LED_AUTH = 2

, HAL_LED_ASSOC = 3

,

HAL_LED_RUN = 4

} |

| |

| enum | HAL_TX_QUEUE {

HAL_TX_QUEUE_INACTIVE = 0

, HAL_TX_QUEUE_DATA = 1

, HAL_TX_QUEUE_BEACON = 2

, HAL_TX_QUEUE_CAB = 3

,

HAL_TX_QUEUE_UAPSD = 4

, HAL_TX_QUEUE_PSPOLL = 5

, HAL_TX_QUEUE_CFEND = 6

, HAL_TX_QUEUE_PAPRD = 7

} |

| |

| enum | HAL_RX_QUEUE { HAL_RX_QUEUE_HP = 0

, HAL_RX_QUEUE_LP = 1

} |

| |

| enum | HAL_TX_QUEUE_SUBTYPE {

HAL_WME_AC_BK = 0

, HAL_WME_AC_BE = 1

, HAL_WME_AC_VI = 2

, HAL_WME_AC_VO = 3

,

HAL_WME_UPSD = 4

} |

| |

| enum | HAL_TX_QUEUE_FLAGS {

HAL_TXQ_TXOKINT_ENABLE = 0x0001

, HAL_TXQ_TXERRINT_ENABLE = 0x0001

, HAL_TXQ_TXDESCINT_ENABLE = 0x0002

, HAL_TXQ_TXEOLINT_ENABLE = 0x0004

,

HAL_TXQ_TXURNINT_ENABLE = 0x0008

, HAL_TXQ_COMPRESSION_ENABLE = 0x0010

, HAL_TXQ_RDYTIME_EXP_POLICY_ENABLE = 0x0020

, HAL_TXQ_DBA_GATED = 0x0040

,

HAL_TXQ_CBR_DIS_QEMPTY = 0x0080

, HAL_TXQ_CBR_DIS_BEMPTY = 0x0100

, HAL_TXQ_FRAG_BURST_BACKOFF_ENABLE = 0x00800000

, HAL_TXQ_BACKOFF_DISABLE = 0x00010000

,

HAL_TXQ_ARB_LOCKOUT_INTRA = 0x00020000

, HAL_TXQ_ARB_LOCKOUT_GLOBAL = 0x00040000

, HAL_TXQ_IGNORE_VIRTCOL = 0x00080000

, HAL_TXQ_SEQNUM_INC_DIS = 0x00100000

} |

| |

| enum | HAL_PKT_TYPE {

HAL_PKT_TYPE_NORMAL = 0

, HAL_PKT_TYPE_ATIM = 1

, HAL_PKT_TYPE_PSPOLL = 2

, HAL_PKT_TYPE_BEACON = 3

,

HAL_PKT_TYPE_PROBE_RESP = 4

, HAL_PKT_TYPE_CHIRP = 5

, HAL_PKT_TYPE_GRP_POLL = 6

, HAL_PKT_TYPE_AMPDU = 7

} |

| |

| enum | HAL_RX_FILTER {

HAL_RX_FILTER_UCAST = 0x00000001

, HAL_RX_FILTER_MCAST = 0x00000002

, HAL_RX_FILTER_BCAST = 0x00000004

, HAL_RX_FILTER_CONTROL = 0x00000008

,

HAL_RX_FILTER_BEACON = 0x00000010

, HAL_RX_FILTER_PROM = 0x00000020

, HAL_RX_FILTER_PROBEREQ = 0x00000080

, HAL_RX_FILTER_PHYERR = 0x00000100

,

HAL_RX_FILTER_MYBEACON = 0x00000200

, HAL_RX_FILTER_COMPBAR = 0x00000400

, HAL_RX_FILTER_COMP_BA = 0x00000800

, HAL_RX_FILTER_PHYRADAR = 0x00002000

,

HAL_RX_FILTER_PSPOLL = 0x00004000

, HAL_RX_FILTER_MCAST_BCAST_ALL = 0x00008000

, HAL_RX_FILTER_BSSID = 0x40000000

} |

| |

| enum | HAL_POWER_MODE { HAL_PM_AWAKE = 0

, HAL_PM_FULL_SLEEP = 1

, HAL_PM_NETWORK_SLEEP = 2

, HAL_PM_UNDEFINED = 3

} |

| |

| enum | HAL_INT {

HAL_INT_RX = 0x00000001

, HAL_INT_RXDESC = 0x00000002

, HAL_INT_RXERR = 0x00000004

, HAL_INT_RXHP = 0x00000001

,

HAL_INT_RXLP = 0x00000002

, HAL_INT_RXNOFRM = 0x00000008

, HAL_INT_RXEOL = 0x00000010

, HAL_INT_RXORN = 0x00000020

,

HAL_INT_TX = 0x00000040

, HAL_INT_TXDESC = 0x00000080

, HAL_INT_TIM_TIMER = 0x00000100

, HAL_INT_MCI = 0x00000200

,

HAL_INT_BBPANIC = 0x00000400

, HAL_INT_TXURN = 0x00000800

, HAL_INT_MIB = 0x00001000

, HAL_INT_RXPHY = 0x00004000

,

HAL_INT_RXKCM = 0x00008000

, HAL_INT_SWBA = 0x00010000

, HAL_INT_BRSSI = 0x00020000

, HAL_INT_BMISS = 0x00040000

,

HAL_INT_BNR = 0x00100000

, HAL_INT_TIM = 0x00200000

, HAL_INT_DTIM = 0x00400000

, HAL_INT_DTIMSYNC = 0x00800000

,

HAL_INT_GPIO = 0x01000000

, HAL_INT_CABEND = 0x02000000

, HAL_INT_TSFOOR = 0x04000000

, HAL_INT_TBTT = 0x08000000

,

HAL_INT_GENTIMER = 0x08000000

, HAL_INT_CST = 0x10000000

, HAL_INT_GTT = 0x20000000

, HAL_INT_FATAL = 0x40000000

,

HAL_INT_BMISC

, HAL_INT_COMMON

} |

| |

| enum | HAL_MSIVEC { HAL_MSIVEC_MISC = 0

, HAL_MSIVEC_TX = 1

, HAL_MSIVEC_RXLP = 2

, HAL_MSIVEC_RXHP = 3

} |

| |

| enum | HAL_INT_TYPE { HAL_INT_LINE = 0

, HAL_INT_MSI = 1

} |

| |

| enum | HAL_INT_MITIGATION {

HAL_INT_RX_FIRSTPKT =0

, HAL_INT_RX_LASTPKT

, HAL_INT_TX_FIRSTPKT

, HAL_INT_TX_LASTPKT

,

HAL_INT_THRESHOLD

} |

| |

| enum | HAL_GPIO_MUX_TYPE {

HAL_GPIO_OUTPUT_MUX_AS_OUTPUT = 0

, HAL_GPIO_OUTPUT_MUX_PCIE_ATTENTION_LED = 1

, HAL_GPIO_OUTPUT_MUX_PCIE_POWER_LED = 2

, HAL_GPIO_OUTPUT_MUX_MAC_NETWORK_LED = 3

,

HAL_GPIO_OUTPUT_MUX_MAC_POWER_LED = 4

, HAL_GPIO_OUTPUT_MUX_AS_WLAN_ACTIVE = 5

, HAL_GPIO_OUTPUT_MUX_AS_TX_FRAME = 6

, HAL_GPIO_OUTPUT_MUX_AS_MCI_WLAN_DATA

,

HAL_GPIO_OUTPUT_MUX_AS_MCI_WLAN_CLK

, HAL_GPIO_OUTPUT_MUX_AS_MCI_BT_DATA

, HAL_GPIO_OUTPUT_MUX_AS_MCI_BT_CLK

, HAL_GPIO_OUTPUT_MUX_AS_WL_IN_TX

,

HAL_GPIO_OUTPUT_MUX_AS_WL_IN_RX

, HAL_GPIO_OUTPUT_MUX_AS_BT_IN_TX

, HAL_GPIO_OUTPUT_MUX_AS_BT_IN_RX

, HAL_GPIO_OUTPUT_MUX_AS_RUCKUS_STROBE

,

HAL_GPIO_OUTPUT_MUX_AS_RUCKUS_DATA

, HAL_GPIO_OUTPUT_MUX_AS_SMARTANT_CTRL0

, HAL_GPIO_OUTPUT_MUX_AS_SMARTANT_CTRL1

, HAL_GPIO_OUTPUT_MUX_AS_SMARTANT_CTRL2

,

HAL_GPIO_OUTPUT_MUX_NUM_ENTRIES

} |

| |

| enum | HAL_GPIO_INTR_TYPE { HAL_GPIO_INTR_LOW = 0

, HAL_GPIO_INTR_HIGH = 1

, HAL_GPIO_INTR_DISABLE = 2

} |

| |

| enum | HAL_RFGAIN { HAL_RFGAIN_INACTIVE = 0

, HAL_RFGAIN_READ_REQUESTED = 1

, HAL_RFGAIN_NEED_CHANGE = 2

} |

| |

| enum | REG_EXT_BITMAP {

REG_EXT_FCC_MIDBAND = 0

, REG_EXT_JAPAN_MIDBAND = 1

, REG_EXT_FCC_DFS_HT40 = 2

, REG_EXT_JAPAN_NONDFS_HT40 = 3

,

REG_EXT_JAPAN_DFS_HT40 = 4

, REG_EXT_FCC_CH_144 = 5

} |

| |

| enum | {

HAL_MODE_11A = 0x001

, HAL_MODE_TURBO = 0x002

, HAL_MODE_11B = 0x004

, HAL_MODE_PUREG = 0x008

,

HAL_MODE_11G = 0x008

, HAL_MODE_108G = 0x020

, HAL_MODE_108A = 0x040

, HAL_MODE_11A_HALF_RATE = 0x200

,

HAL_MODE_11A_QUARTER_RATE = 0x400

, HAL_MODE_11G_HALF_RATE = 0x800

, HAL_MODE_11G_QUARTER_RATE = 0x1000

, HAL_MODE_11NG_HT20 = 0x008000

,

HAL_MODE_11NA_HT20 = 0x010000

, HAL_MODE_11NG_HT40PLUS = 0x020000

, HAL_MODE_11NG_HT40MINUS = 0x040000

, HAL_MODE_11NA_HT40PLUS = 0x080000

,

HAL_MODE_11NA_HT40MINUS = 0x100000

, HAL_MODE_ALL = 0xffffff

} |

| |

| enum | HAL_CHAIN_TYPE { HAL_CHAINTYPE_TX = 1

, HAL_CHAINTYPE_RX = 2

} |

| |

| enum | HAL_HT_MACMODE { HAL_HT_MACMODE_20 = 0

, HAL_HT_MACMODE_2040 = 1

} |

| |

| enum | HAL_HT_PHYMODE { HAL_HT_PHYMODE_20 = 0

, HAL_HT_PHYMODE_2040 = 1

} |

| |

| enum | HAL_HT_EXTPROTSPACING { HAL_HT_EXTPROTSPACING_20 = 0

, HAL_HT_EXTPROTSPACING_25 = 1

} |

| |

| enum | HAL_HT_RXCLEAR { HAL_RX_CLEAR_CTL_LOW = 0x1

, HAL_RX_CLEAR_EXT_LOW = 0x2

} |

| |

| enum | HAL_FREQ_BAND { HAL_FREQ_BAND_5GHZ = 0

, HAL_FREQ_BAND_2GHZ = 1

} |

| |

| enum | HAL_ANT_SETTING { HAL_ANT_VARIABLE = 0

, HAL_ANT_FIXED_A = 1

, HAL_ANT_FIXED_B = 2

} |

| |

| enum | HAL_OPMODE { HAL_M_STA = 1

, HAL_M_IBSS = 0

, HAL_M_HOSTAP = 6

, HAL_M_MONITOR = 8

} |

| |

| enum | HAL_RESET_TYPE { HAL_RESET_NORMAL = 0

, HAL_RESET_BBPANIC = 1

, HAL_RESET_FORCE_COLD = 2

} |

| |

| enum | { HAL_RESET_POWER_ON

, HAL_RESET_WARM

, HAL_RESET_COLD

} |

| |

| enum | HAL_KEY_TYPE { HAL_KEY_TYPE_CLEAR

, HAL_KEY_TYPE_WEP

, HAL_KEY_TYPE_AES

, HAL_KEY_TYPE_TKIP

} |

| |

| enum | HAL_CIPHER {

HAL_CIPHER_WEP = 0

, HAL_CIPHER_AES_OCB = 1

, HAL_CIPHER_AES_CCM = 2

, HAL_CIPHER_CKIP = 3

,

HAL_CIPHER_TKIP = 4

, HAL_CIPHER_CLR = 5

, HAL_CIPHER_MIC = 127

} |

| |

| enum | { HAL_SLOT_TIME_6 = 6

, HAL_SLOT_TIME_9 = 9

, HAL_SLOT_TIME_20 = 20

} |

| |

| enum | HAL_ANI_CMD {

HAL_ANI_PRESENT = 0

, HAL_ANI_NOISE_IMMUNITY_LEVEL = 1

, HAL_ANI_OFDM_WEAK_SIGNAL_DETECTION = 2

, HAL_ANI_CCK_WEAK_SIGNAL_THR = 3

,

HAL_ANI_FIRSTEP_LEVEL = 4

, HAL_ANI_SPUR_IMMUNITY_LEVEL = 5

, HAL_ANI_MODE = 6

, HAL_ANI_PHYERR_RESET = 7

,

HAL_ANI_MRC_CCK = 8

, HAL_ANI_CCK_NOISE_IMMUNITY_LEVEL = 9

} |

| |

| enum | HAL_CAP_INTMIT_CMD {

HAL_CAP_INTMIT_PRESENT = 0

, HAL_CAP_INTMIT_ENABLE = 1

, HAL_CAP_INTMIT_NOISE_IMMUNITY_LEVEL = 2

, HAL_CAP_INTMIT_OFDM_WEAK_SIGNAL_LEVEL = 3

,

HAL_CAP_INTMIT_CCK_WEAK_SIGNAL_THR = 4

, HAL_CAP_INTMIT_FIRSTEP_LEVEL = 5

, HAL_CAP_INTMIT_SPUR_IMMUNITY_LEVEL = 6

} |

| |

| enum | HAL_DFS_DOMAIN { HAL_DFS_UNINIT_DOMAIN = 0

, HAL_DFS_FCC_DOMAIN = 1

, HAL_DFS_ETSI_DOMAIN = 2

, HAL_DFS_MKK4_DOMAIN = 3

} |

| |

| enum | HAL_MFP_OPT_T { HAL_MFP_QOSDATA = 0

, HAL_MFP_PASSTHRU

, HAL_MFP_HW_CRYPTO

} |

| |

| enum | HAL_ANT_DIV_COMB_LNA_CONF { HAL_ANT_DIV_COMB_LNA1_MINUS_LNA2 = 0

, HAL_ANT_DIV_COMB_LNA2 = 1

, HAL_ANT_DIV_COMB_LNA1 = 2

, HAL_ANT_DIV_COMB_LNA1_PLUS_LNA2 = 3

} |

| |

| enum | HAL_QUIET_FLAG { HAL_QUIET_DISABLE = 0x0

, HAL_QUIET_ENABLE = 0x1

, HAL_QUIET_ADD_CURRENT_TSF = 0x2

, HAL_QUIET_ADD_SWBA_RESP_TIME = 0x4

} |

| |

| enum | HAL_GEN_TIMER_DOMAIN { HAL_GEN_TIMER_TSF = 0

, HAL_GEN_TIMER_TSF2

, HAL_GEN_TIMER_TSF_ANY

} |

| |

| enum | SER_REG_MODE { SER_REG_MODE_OFF = 0

, SER_REG_MODE_ON = 1

, SER_REG_MODE_AUTO = 2

} |

| |

|

| const char *__ahdecl | ath_hal_probe (uint16_t vendorid, uint16_t devid) |

| |

| struct ath_hal *__ahdecl | ath_hal_attach (uint16_t devid, HAL_SOFTC, HAL_BUS_TAG, HAL_BUS_HANDLE, uint16_t *eepromdata, HAL_OPS_CONFIG *ah_config, HAL_STATUS *status) |

| |

| const char * | ath_hal_mac_name (struct ath_hal *) |

| |

| const char * | ath_hal_rf_name (struct ath_hal *) |

| |

| HAL_STATUS __ahdecl | ath_hal_getchannels (struct ath_hal *, struct ieee80211_channel *chans, u_int maxchans, int *nchans, u_int modeSelect, HAL_CTRY_CODE cc, HAL_REG_DOMAIN regDmn, HAL_BOOL enableExtendedChannels) |

| |

| HAL_STATUS __ahdecl | ath_hal_init_channels (struct ath_hal *, struct ieee80211_channel *chans, u_int maxchans, int *nchans, u_int modeSelect, HAL_CTRY_CODE cc, HAL_REG_DOMAIN rd, HAL_BOOL enableExtendedChannels) |

| |

| HAL_STATUS __ahdecl | ath_hal_set_channels (struct ath_hal *, struct ieee80211_channel *chans, int nchans, HAL_CTRY_CODE cc, HAL_REG_DOMAIN regDmn) |

| |

| int __ahdecl | ath_hal_get_mimo_chan_noise (struct ath_hal *ah, const struct ieee80211_channel *chan, int16_t *nf_ctl, int16_t *nf_ext) |

| |

| void __ahdecl | ath_hal_process_noisefloor (struct ath_hal *ah) |

| |

| u_int __ahdecl | ath_hal_getwirelessmodes (struct ath_hal *) |

| |

| int | ath_hal_get_curmode (struct ath_hal *ah, const struct ieee80211_channel *chan) |

| |

| uint32_t __ahdecl | ath_hal_pkt_txtime (struct ath_hal *ah, const HAL_RATE_TABLE *rates, uint32_t frameLen, uint16_t rateix, HAL_BOOL isht40, HAL_BOOL shortPreamble, HAL_BOOL includeSifs) |

| |

| uint32_t __ahdecl | ath_computedur_ht (uint32_t frameLen, uint16_t rate, int streams, HAL_BOOL isht40, HAL_BOOL isShortGI) |

| |

| uint16_t __ahdecl | ath_hal_computetxtime (struct ath_hal *, const HAL_RATE_TABLE *rates, uint32_t frameLen, uint16_t rateix, HAL_BOOL shortPreamble, HAL_BOOL includeSifs) |

| |

| void __ahdecl | ath_hal_adjusttsf (struct ath_hal *ah, int32_t tsfdelta) |

| |

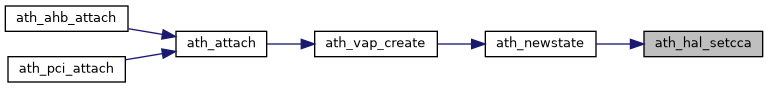

| void __ahdecl | ath_hal_setcca (struct ath_hal *ah, int ena) |

| |

| int __ahdecl | ath_hal_getcca (struct ath_hal *ah) |

| |

| void __ahdecl | ath_hal_set_dfs_cac_tx_quiet (struct ath_hal *ah, HAL_BOOL ena) |

| |

| HAL_BOOL __ahdecl | ath_hal_EepromDataRead (struct ath_hal *ah, u_int off, uint16_t *data) |

| |

| static u_int32_t | ath_hal_get_mfp_qos (struct ath_hal *ah) |

| |

| u_int | ath_hal_mac_clks (struct ath_hal *ah, u_int usecs) |

| |

| u_int | ath_hal_mac_usec (struct ath_hal *ah, u_int clks) |

| |

| uint64_t | ath_hal_mac_psec (struct ath_hal *ah, u_int clks) |

| |