#include <sys/cdefs.h>#include "bxe.h"#include "bxe_elink.h"#include "ecore_mfw_req.h"#include "ecore_fw_defs.h"#include "ecore_hsi.h"#include "ecore_reg.h"

Go to the source code of this file.

Typedefs | |

| typedef elink_status_t(* | read_sfp_module_eeprom_func_p) (struct elink_phy *phy, struct elink_params *params, uint8_t dev_addr, uint16_t addr, uint8_t byte_cnt, uint8_t *o_buf, uint8_t) |

Functions | |

| __FBSDID ("$FreeBSD$") | |

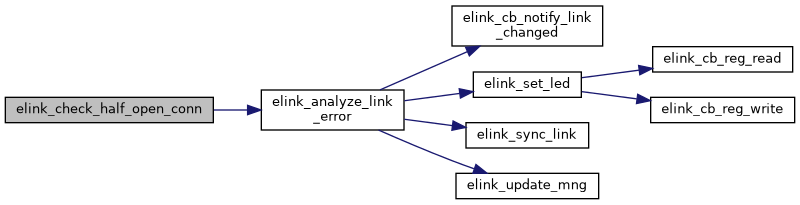

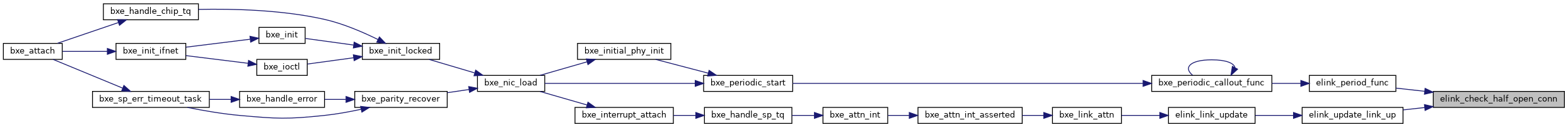

| static elink_status_t | elink_check_half_open_conn (struct elink_params *params, struct elink_vars *vars, uint8_t notify) |

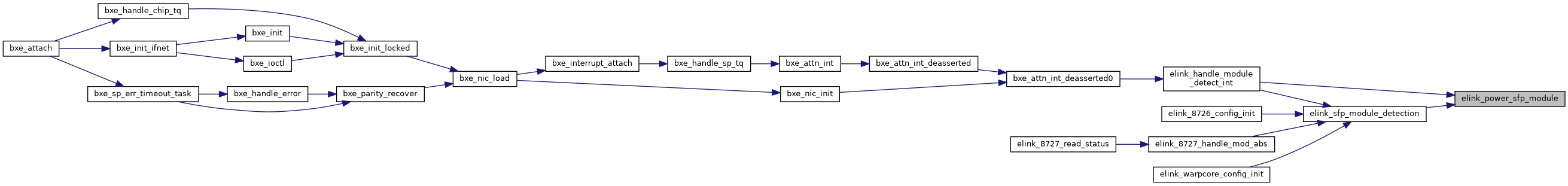

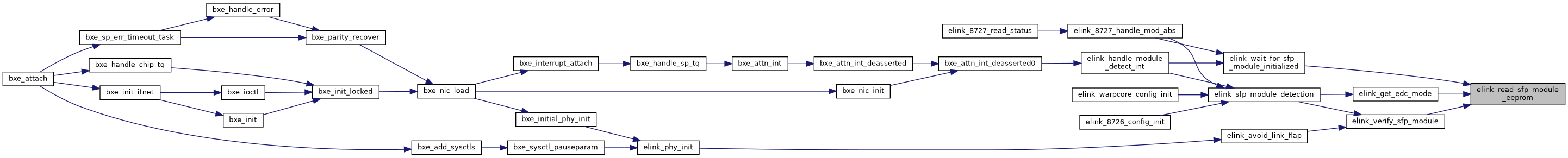

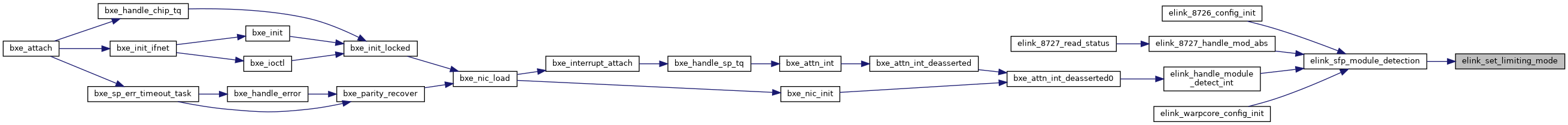

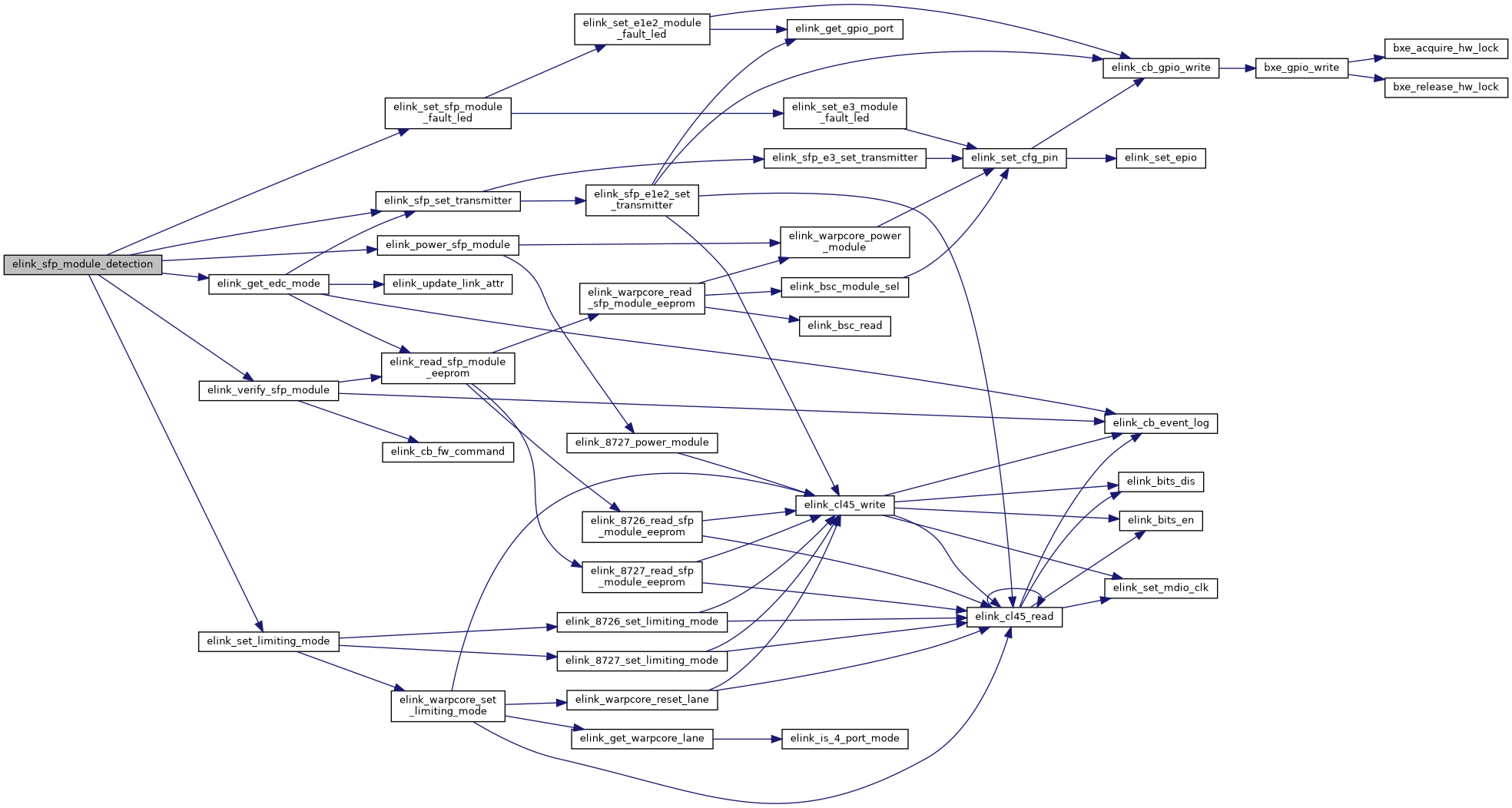

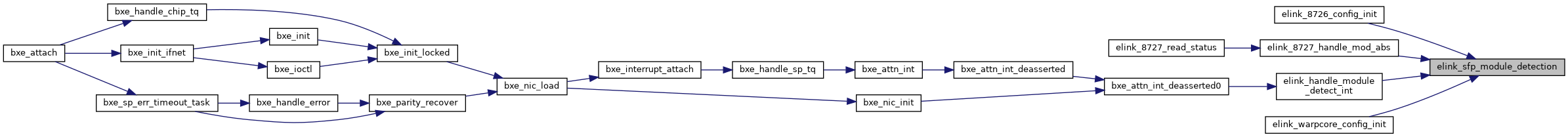

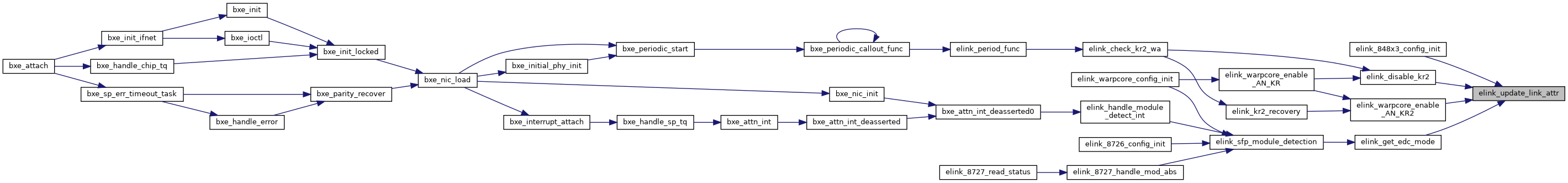

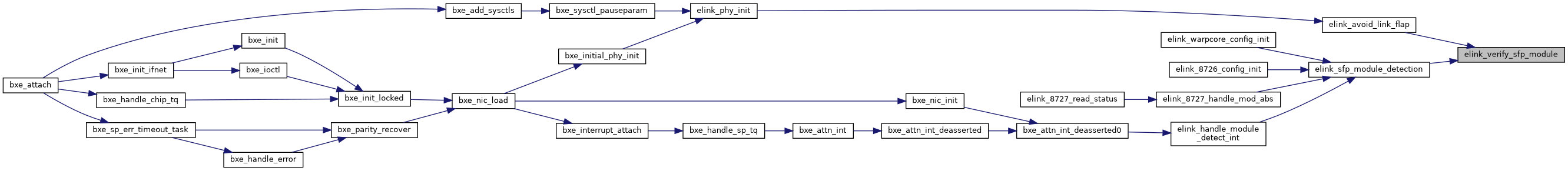

| static elink_status_t | elink_sfp_module_detection (struct elink_phy *phy, struct elink_params *params) |

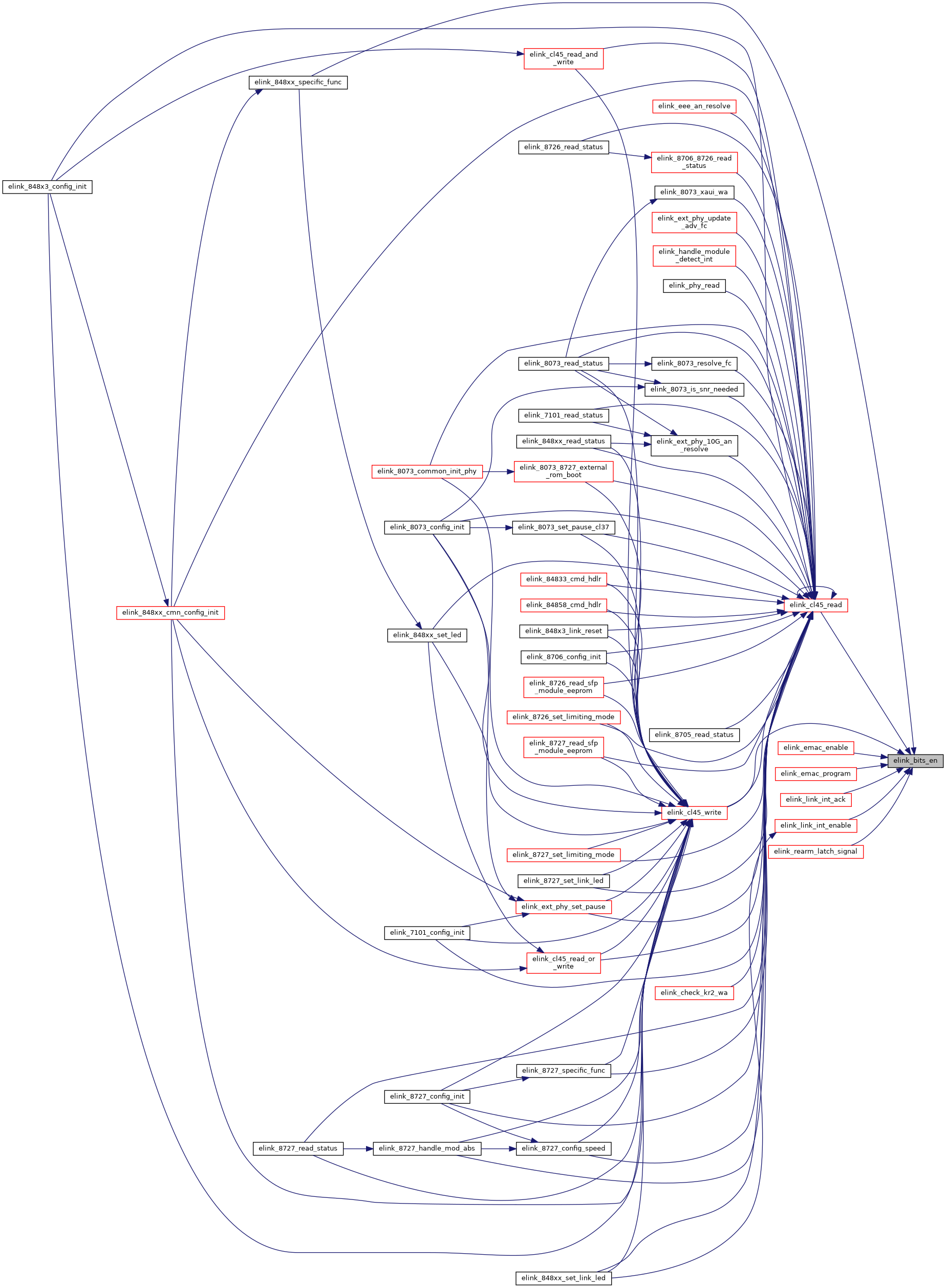

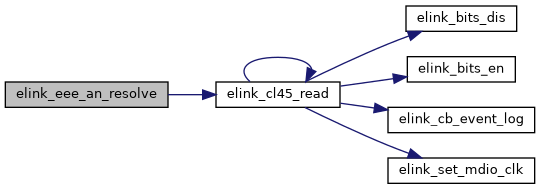

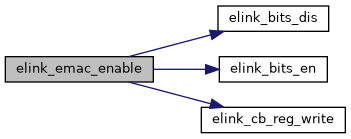

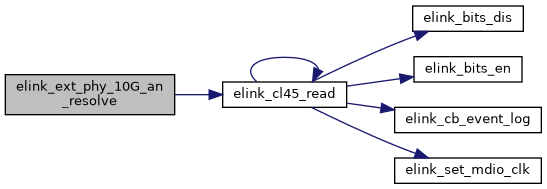

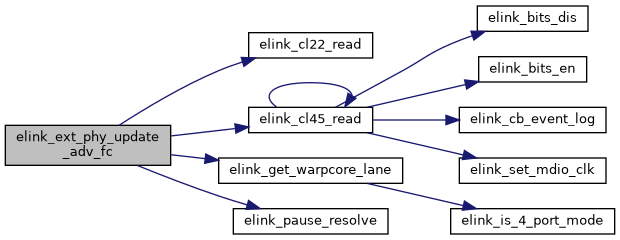

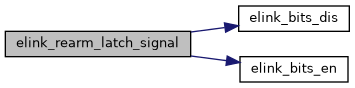

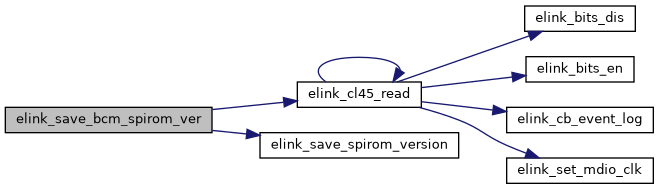

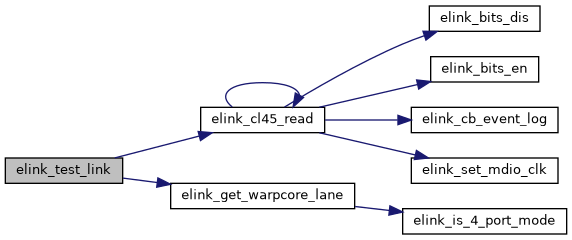

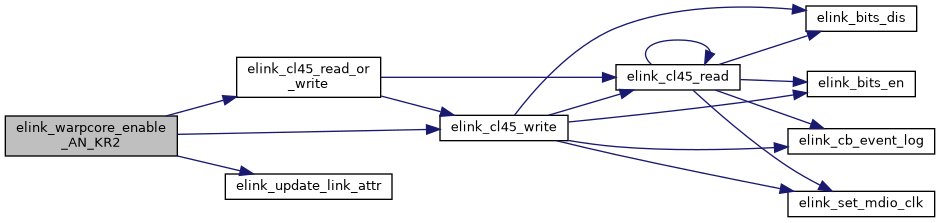

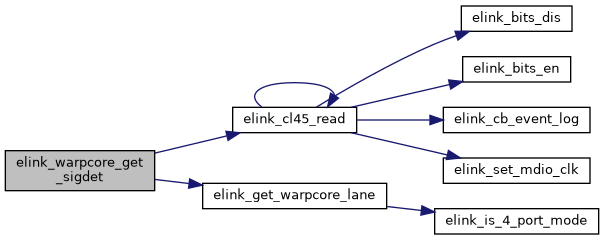

| static uint32_t | elink_bits_en (struct bxe_softc *sc, uint32_t reg, uint32_t bits) |

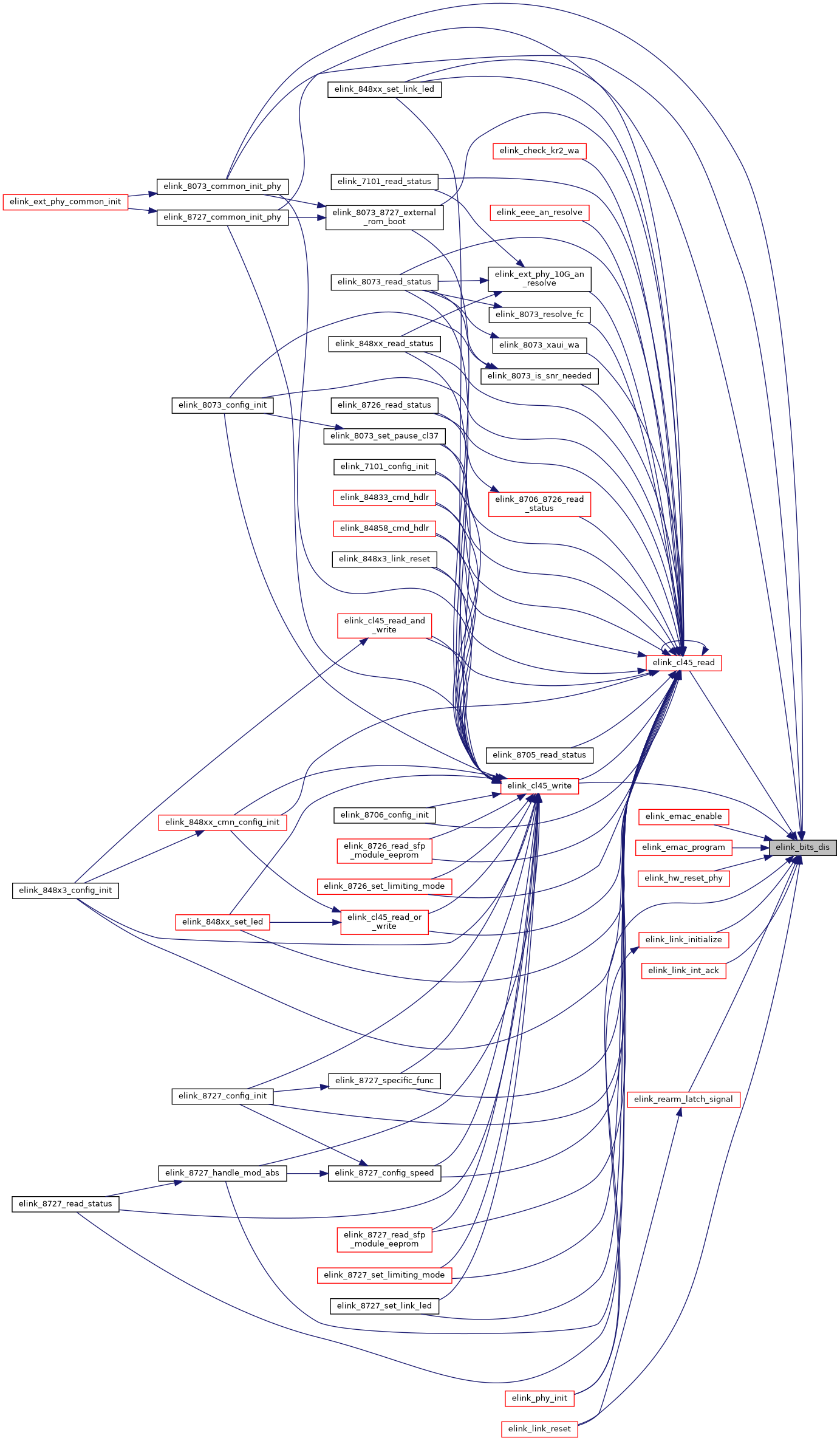

| static uint32_t | elink_bits_dis (struct bxe_softc *sc, uint32_t reg, uint32_t bits) |

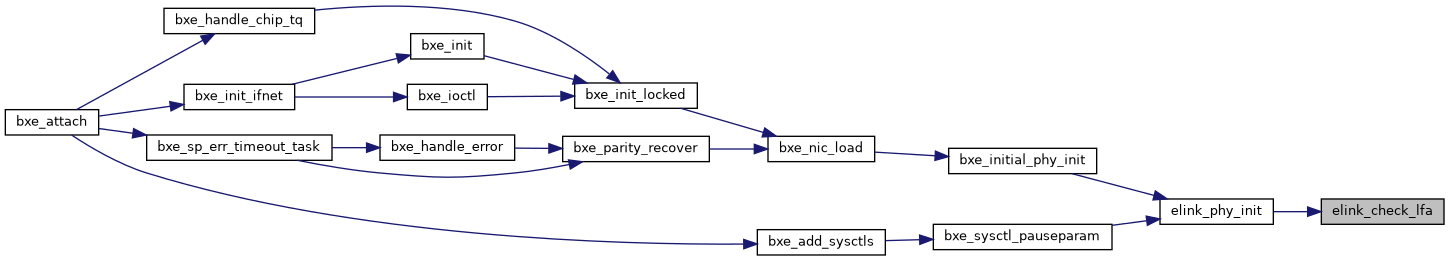

| static int | elink_check_lfa (struct elink_params *params) |

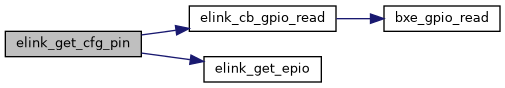

| static void | elink_get_epio (struct bxe_softc *sc, uint32_t epio_pin, uint32_t *en) |

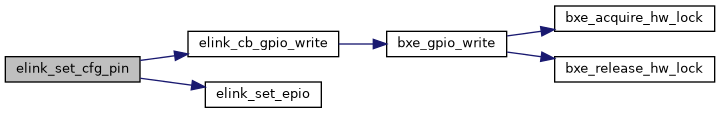

| static void | elink_set_epio (struct bxe_softc *sc, uint32_t epio_pin, uint32_t en) |

| static void | elink_set_cfg_pin (struct bxe_softc *sc, uint32_t pin_cfg, uint32_t val) |

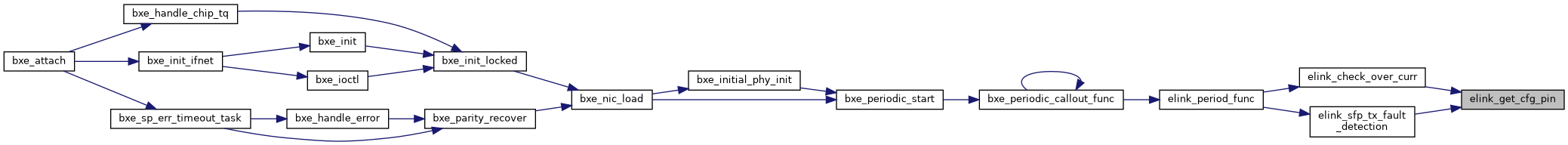

| static uint32_t | elink_get_cfg_pin (struct bxe_softc *sc, uint32_t pin_cfg, uint32_t *val) |

| static void | elink_ets_e2e3a0_disabled (struct elink_params *params) |

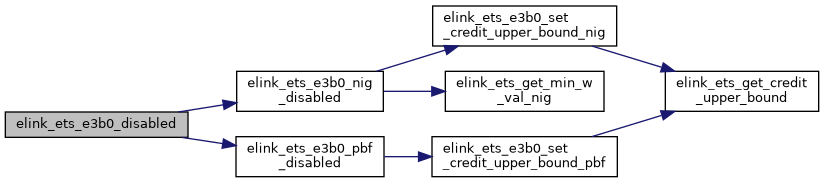

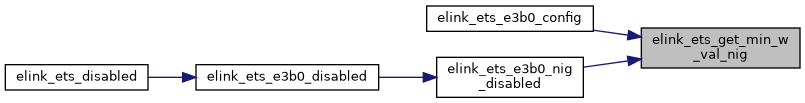

| static uint32_t | elink_ets_get_min_w_val_nig (const struct elink_vars *vars) |

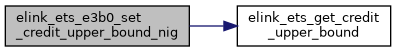

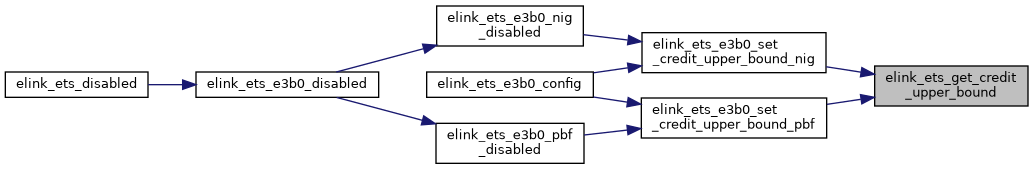

| static uint32_t | elink_ets_get_credit_upper_bound (const uint32_t min_w_val) |

| static void | elink_ets_e3b0_set_credit_upper_bound_nig (const struct elink_params *params, const uint32_t min_w_val) |

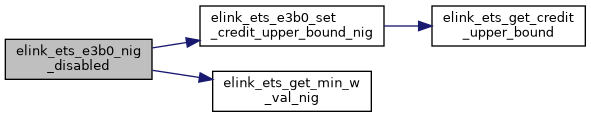

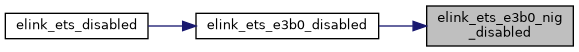

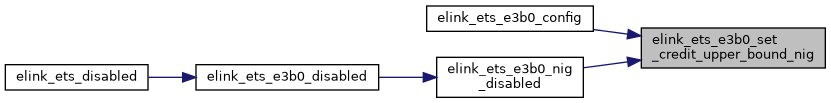

| static void | elink_ets_e3b0_nig_disabled (const struct elink_params *params, const struct elink_vars *vars) |

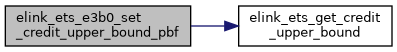

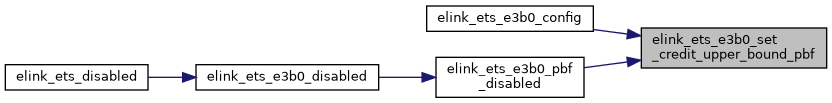

| static void | elink_ets_e3b0_set_credit_upper_bound_pbf (const struct elink_params *params, const uint32_t min_w_val) |

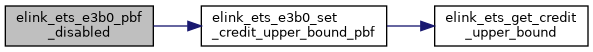

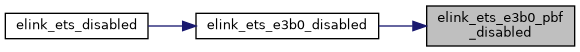

| static void | elink_ets_e3b0_pbf_disabled (const struct elink_params *params) |

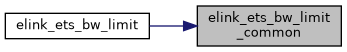

| static elink_status_t | elink_ets_e3b0_disabled (const struct elink_params *params, const struct elink_vars *vars) |

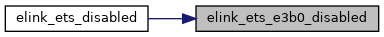

| elink_status_t | elink_ets_disabled (struct elink_params *params, struct elink_vars *vars) |

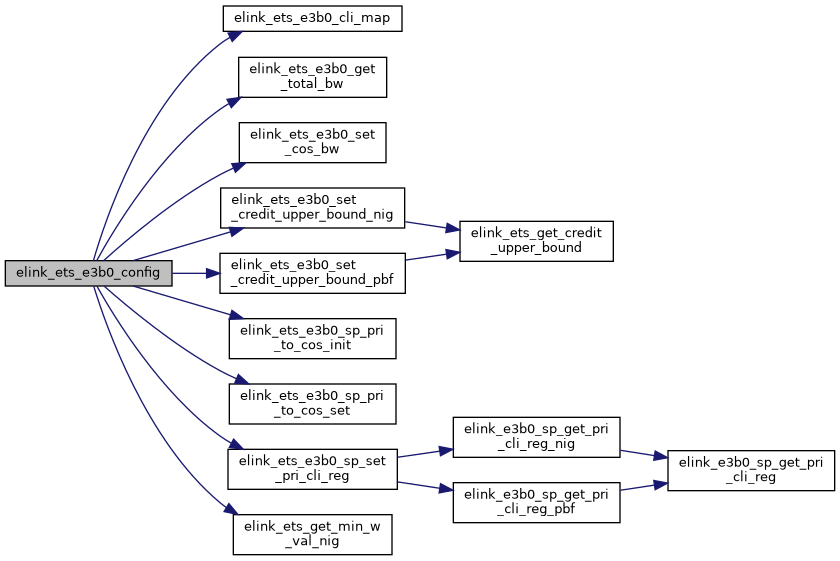

| static elink_status_t | elink_ets_e3b0_cli_map (const struct elink_params *params, const struct elink_ets_params *ets_params, const uint8_t cos_sp_bitmap, const uint8_t cos_bw_bitmap) |

| static elink_status_t | elink_ets_e3b0_set_cos_bw (struct bxe_softc *sc, const uint8_t cos_entry, const uint32_t min_w_val_nig, const uint32_t min_w_val_pbf, const uint16_t total_bw, const uint8_t bw, const uint8_t port) |

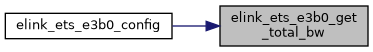

| static elink_status_t | elink_ets_e3b0_get_total_bw (const struct elink_params *params, struct elink_ets_params *ets_params, uint16_t *total_bw) |

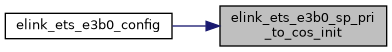

| static void | elink_ets_e3b0_sp_pri_to_cos_init (uint8_t *sp_pri_to_cos) |

| static elink_status_t | elink_ets_e3b0_sp_pri_to_cos_set (const struct elink_params *params, uint8_t *sp_pri_to_cos, const uint8_t pri, const uint8_t cos_entry) |

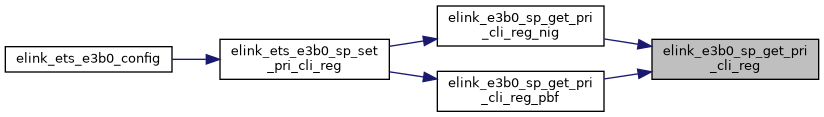

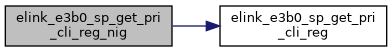

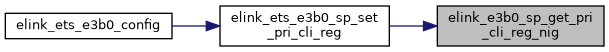

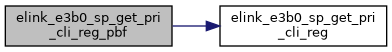

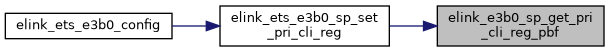

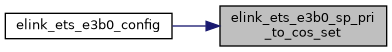

| static uint64_t | elink_e3b0_sp_get_pri_cli_reg (const uint8_t cos, const uint8_t cos_offset, const uint8_t pri_set, const uint8_t pri_offset, const uint8_t entry_size) |

| static uint64_t | elink_e3b0_sp_get_pri_cli_reg_nig (const uint8_t cos, const uint8_t pri_set) |

| static uint64_t | elink_e3b0_sp_get_pri_cli_reg_pbf (const uint8_t cos, const uint8_t pri_set) |

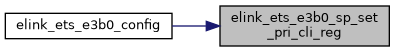

| static elink_status_t | elink_ets_e3b0_sp_set_pri_cli_reg (const struct elink_params *params, uint8_t *sp_pri_to_cos) |

| elink_status_t | elink_ets_e3b0_config (const struct elink_params *params, const struct elink_vars *vars, struct elink_ets_params *ets_params) |

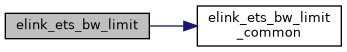

| static void | elink_ets_bw_limit_common (const struct elink_params *params) |

| void | elink_ets_bw_limit (const struct elink_params *params, const uint32_t cos0_bw, const uint32_t cos1_bw) |

| elink_status_t | elink_ets_strict (const struct elink_params *params, const uint8_t strict_cos) |

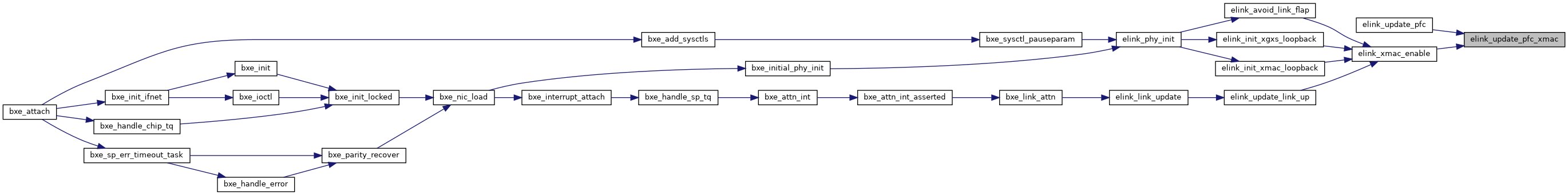

| static void | elink_update_pfc_xmac (struct elink_params *params, struct elink_vars *vars, uint8_t is_lb) |

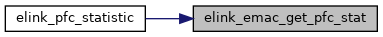

| static void | elink_emac_get_pfc_stat (struct elink_params *params, uint32_t pfc_frames_sent[2], uint32_t pfc_frames_received[2]) |

| void | elink_pfc_statistic (struct elink_params *params, struct elink_vars *vars, uint32_t pfc_frames_sent[2], uint32_t pfc_frames_received[2]) |

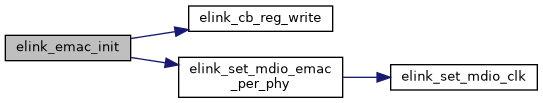

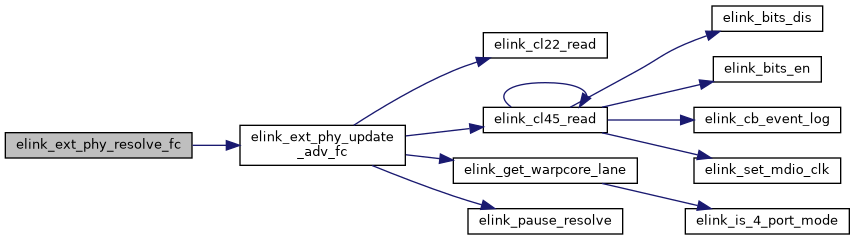

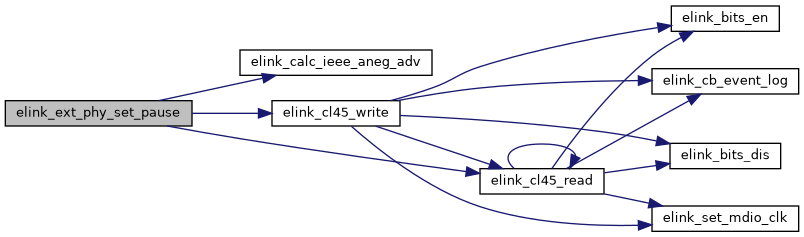

| static void | elink_set_mdio_clk (struct bxe_softc *sc, uint32_t chip_id, uint32_t emac_base) |

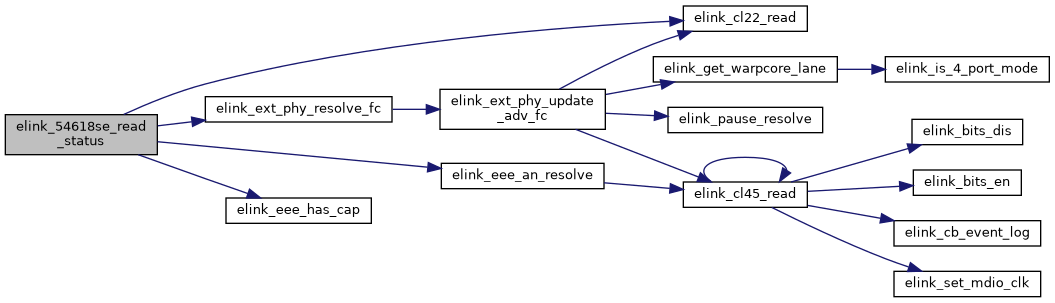

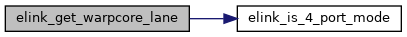

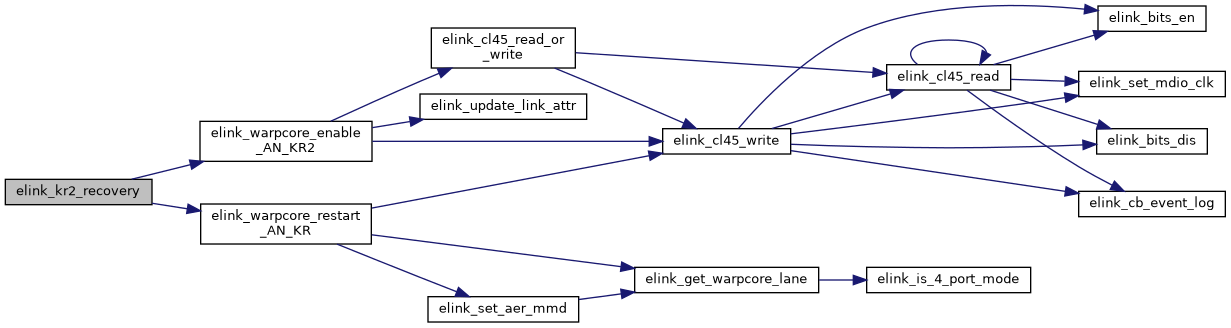

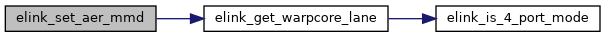

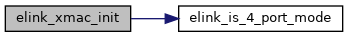

| static uint8_t | elink_is_4_port_mode (struct bxe_softc *sc) |

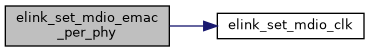

| static void | elink_set_mdio_emac_per_phy (struct bxe_softc *sc, struct elink_params *params) |

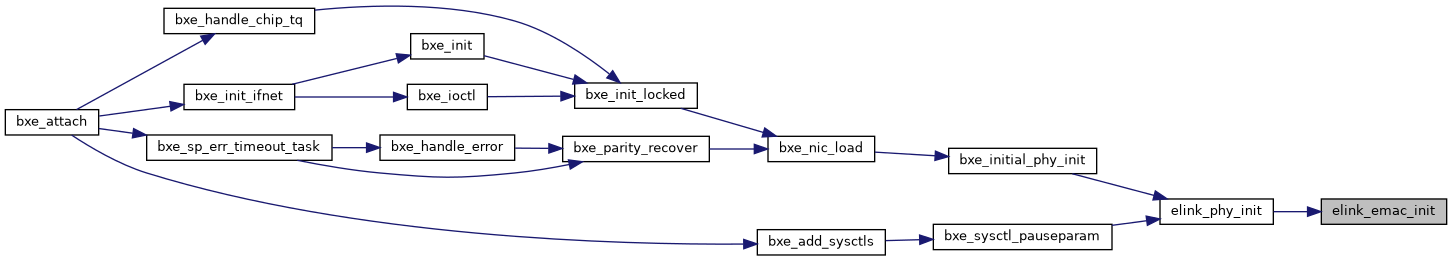

| static void | elink_emac_init (struct elink_params *params, struct elink_vars *vars) |

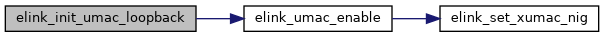

| static void | elink_set_xumac_nig (struct elink_params *params, uint16_t tx_pause_en, uint8_t enable) |

| static void | elink_set_umac_rxtx (struct elink_params *params, uint8_t en) |

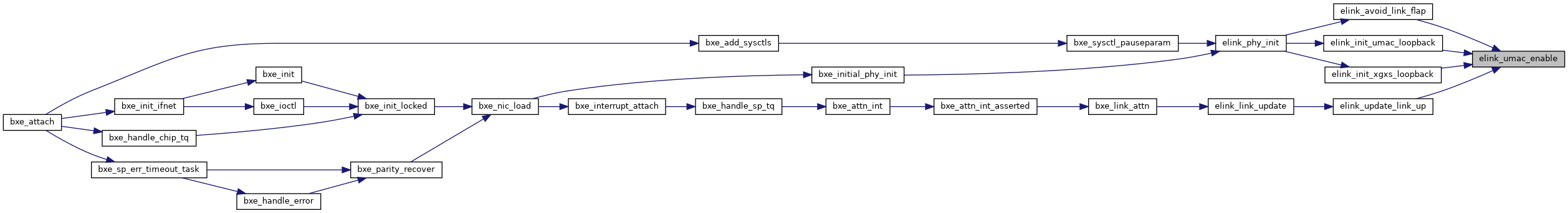

| static void | elink_umac_enable (struct elink_params *params, struct elink_vars *vars, uint8_t lb) |

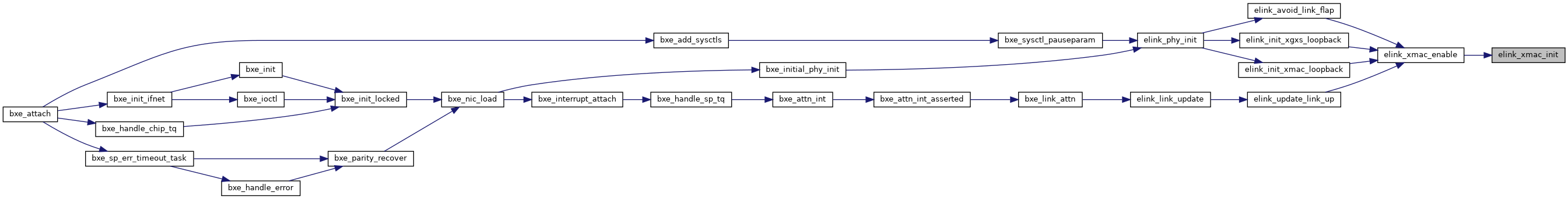

| static void | elink_xmac_init (struct elink_params *params, uint32_t max_speed) |

| static void | elink_set_xmac_rxtx (struct elink_params *params, uint8_t en) |

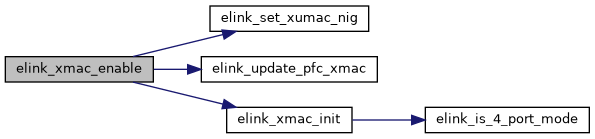

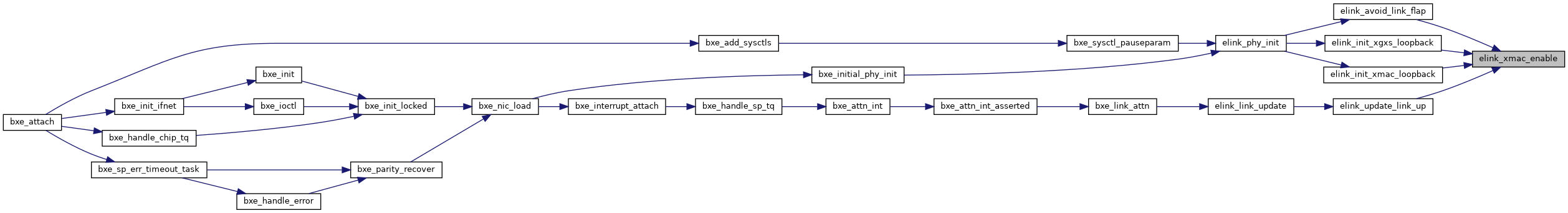

| static elink_status_t | elink_xmac_enable (struct elink_params *params, struct elink_vars *vars, uint8_t lb) |

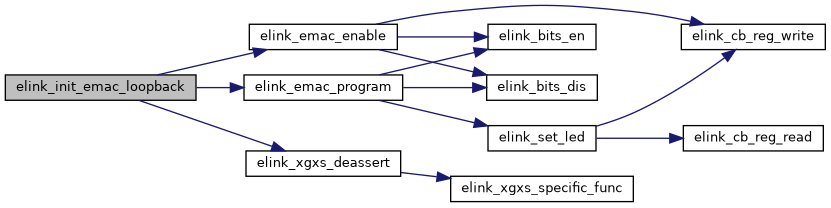

| static elink_status_t | elink_emac_enable (struct elink_params *params, struct elink_vars *vars, uint8_t lb) |

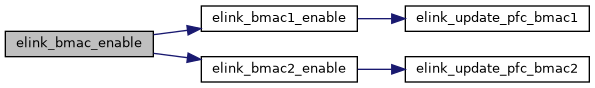

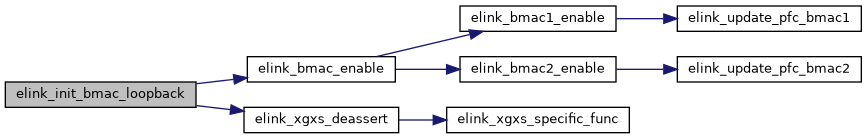

| static void | elink_update_pfc_bmac1 (struct elink_params *params, struct elink_vars *vars) |

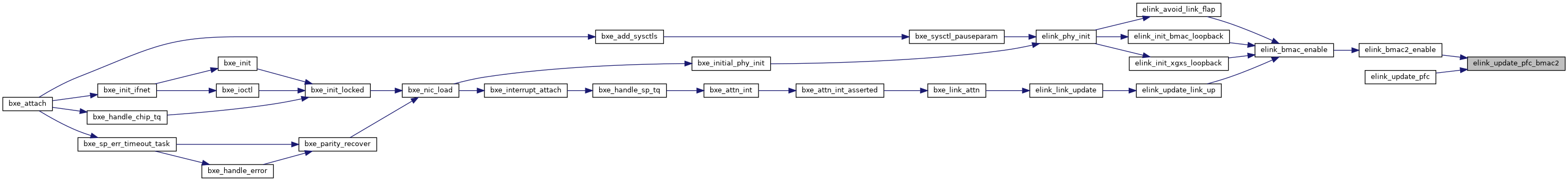

| static void | elink_update_pfc_bmac2 (struct elink_params *params, struct elink_vars *vars, uint8_t is_lb) |

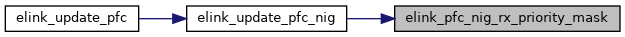

| static elink_status_t | elink_pfc_nig_rx_priority_mask (struct bxe_softc *sc, uint8_t cos_entry, uint32_t priority_mask, uint8_t port) |

| static void | elink_update_mng (struct elink_params *params, uint32_t link_status) |

| static void | elink_update_pfc_nig (struct elink_params *params, struct elink_vars *vars, struct elink_nig_brb_pfc_port_params *nig_params) |

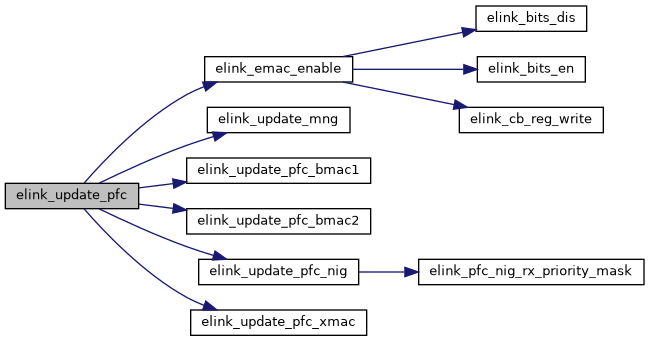

| elink_status_t | elink_update_pfc (struct elink_params *params, struct elink_vars *vars, struct elink_nig_brb_pfc_port_params *pfc_params) |

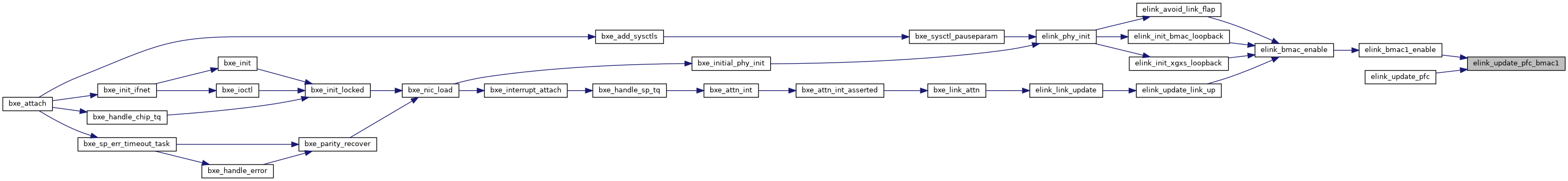

| static elink_status_t | elink_bmac1_enable (struct elink_params *params, struct elink_vars *vars, uint8_t is_lb) |

| static elink_status_t | elink_bmac2_enable (struct elink_params *params, struct elink_vars *vars, uint8_t is_lb) |

| static elink_status_t | elink_bmac_enable (struct elink_params *params, struct elink_vars *vars, uint8_t is_lb, uint8_t reset_bmac) |

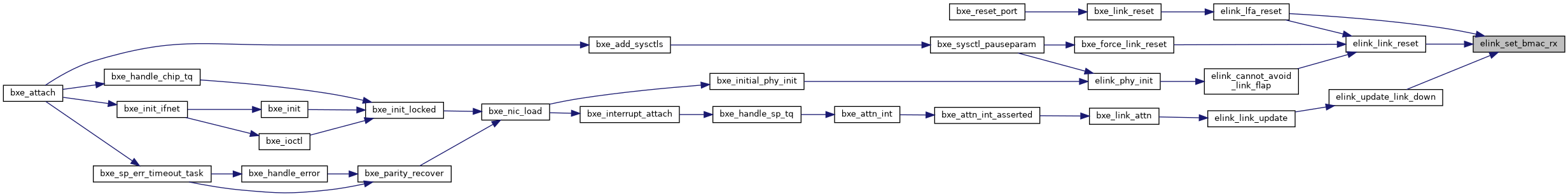

| static void | elink_set_bmac_rx (struct bxe_softc *sc, uint32_t chip_id, uint8_t port, uint8_t en) |

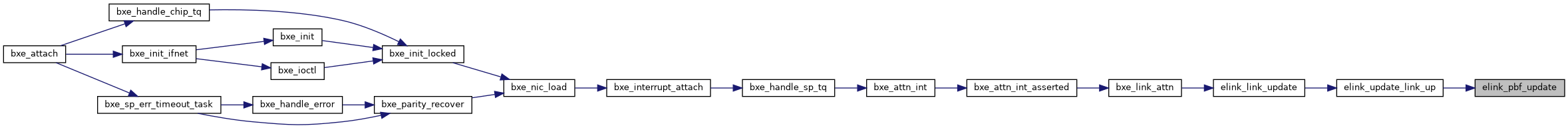

| static elink_status_t | elink_pbf_update (struct elink_params *params, uint32_t flow_ctrl, uint32_t line_speed) |

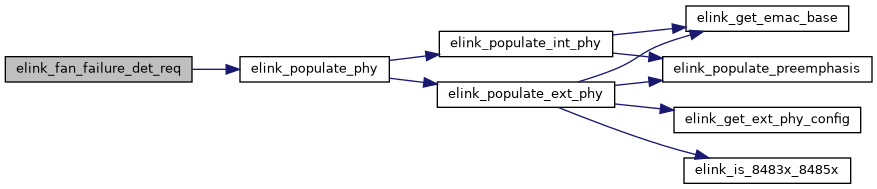

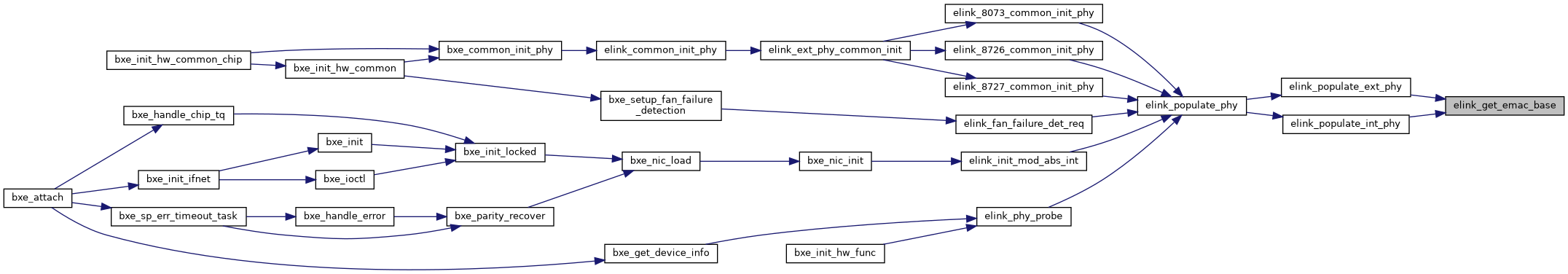

| static uint32_t | elink_get_emac_base (struct bxe_softc *sc, uint32_t mdc_mdio_access, uint8_t port) |

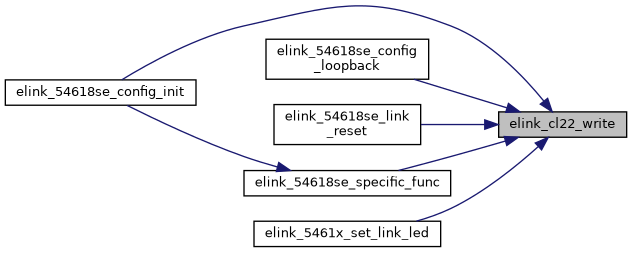

| static elink_status_t | elink_cl22_write (struct bxe_softc *sc, struct elink_phy *phy, uint16_t reg, uint16_t val) |

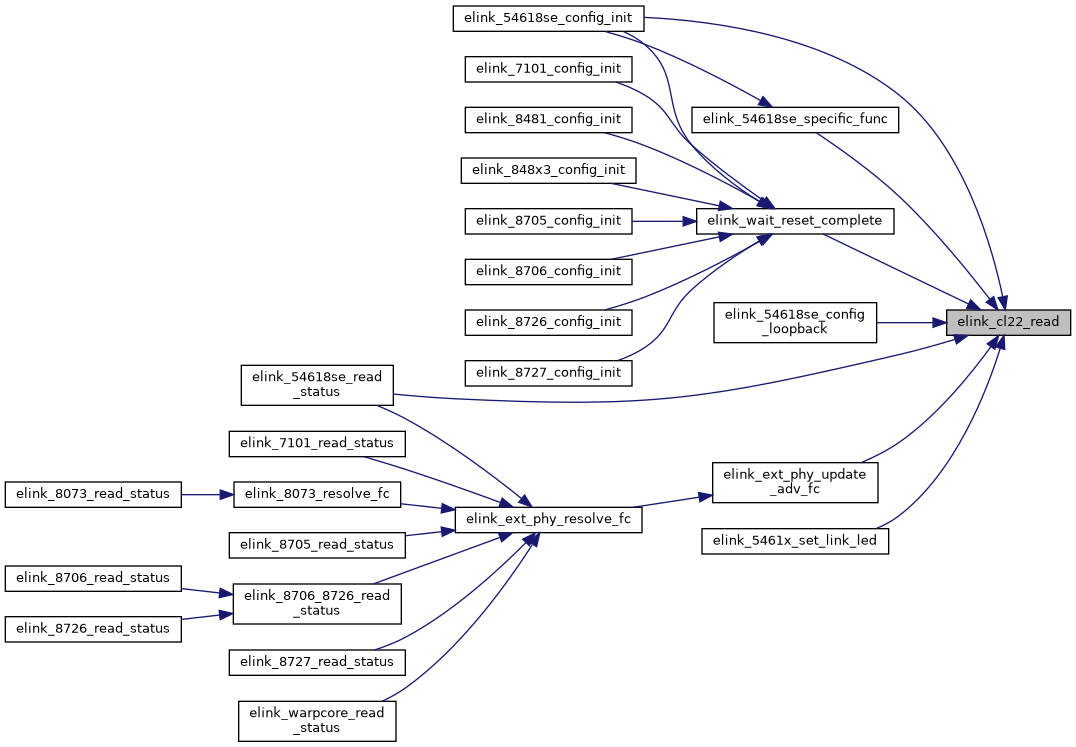

| static elink_status_t | elink_cl22_read (struct bxe_softc *sc, struct elink_phy *phy, uint16_t reg, uint16_t *ret_val) |

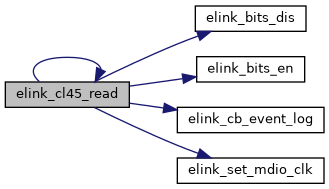

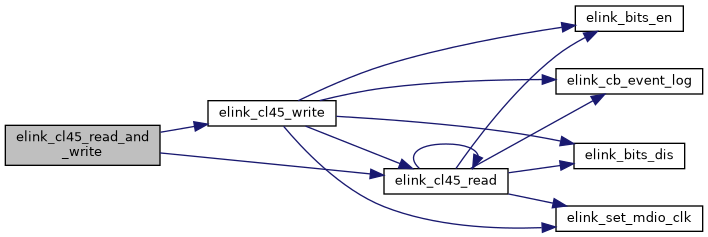

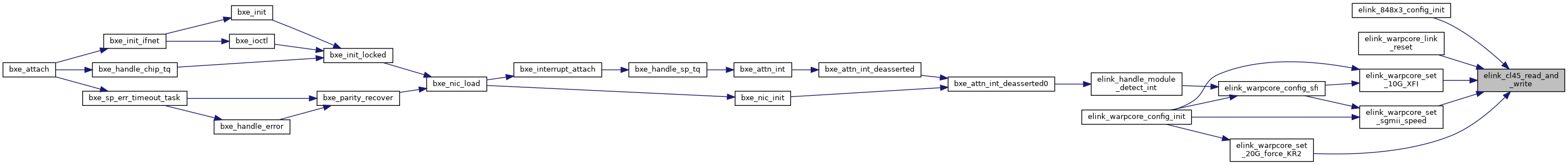

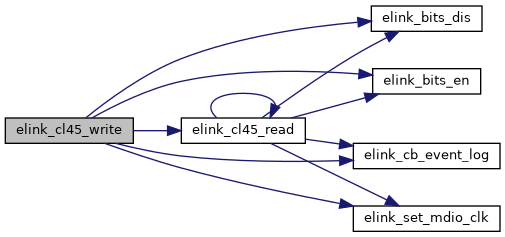

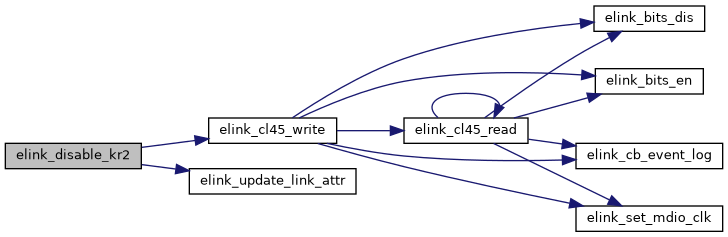

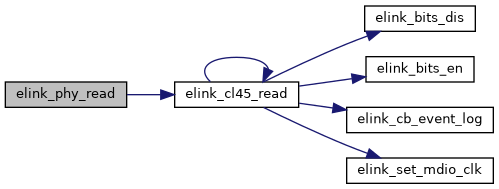

| static elink_status_t | elink_cl45_read (struct bxe_softc *sc, struct elink_phy *phy, uint8_t devad, uint16_t reg, uint16_t *ret_val) |

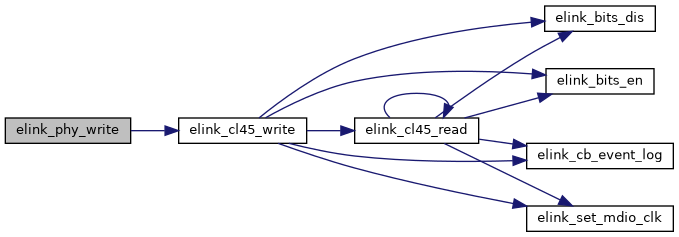

| static elink_status_t | elink_cl45_write (struct bxe_softc *sc, struct elink_phy *phy, uint8_t devad, uint16_t reg, uint16_t val) |

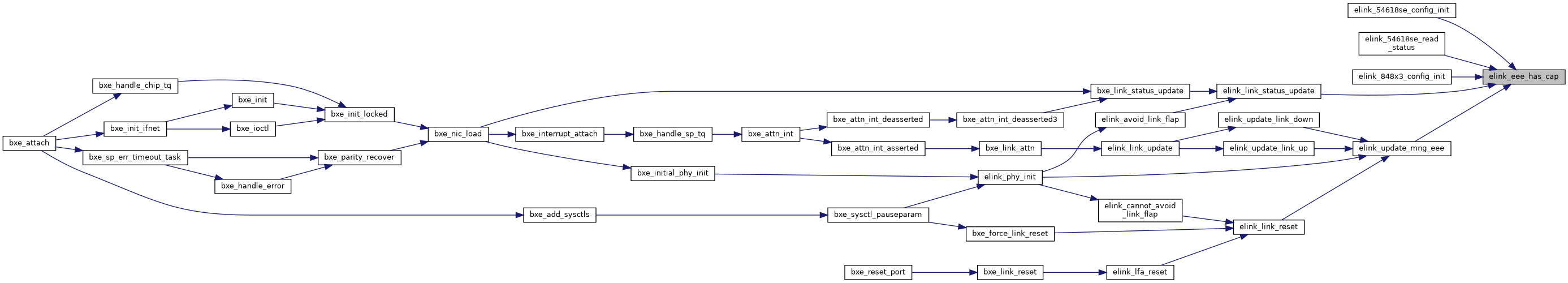

| static uint8_t | elink_eee_has_cap (struct elink_params *params) |

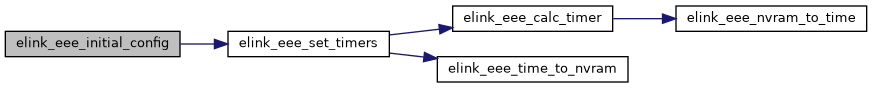

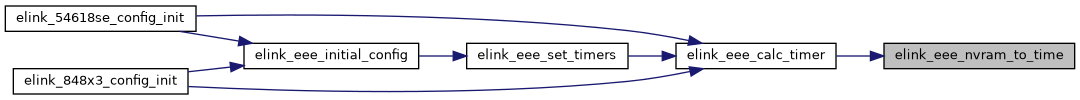

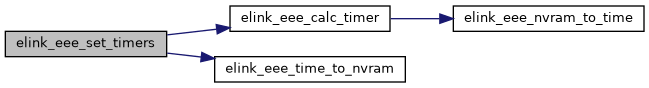

| static elink_status_t | elink_eee_nvram_to_time (uint32_t nvram_mode, uint32_t *idle_timer) |

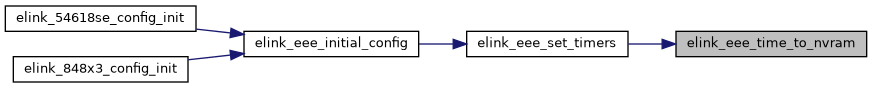

| static elink_status_t | elink_eee_time_to_nvram (uint32_t idle_timer, uint32_t *nvram_mode) |

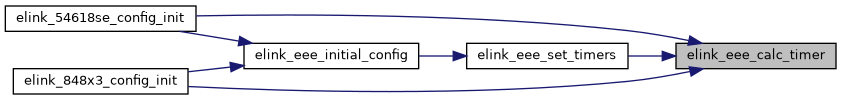

| static uint32_t | elink_eee_calc_timer (struct elink_params *params) |

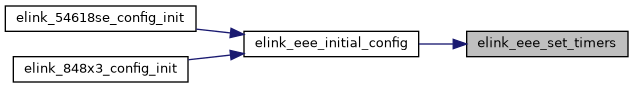

| static elink_status_t | elink_eee_set_timers (struct elink_params *params, struct elink_vars *vars) |

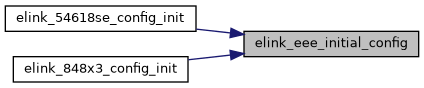

| static elink_status_t | elink_eee_initial_config (struct elink_params *params, struct elink_vars *vars, uint8_t mode) |

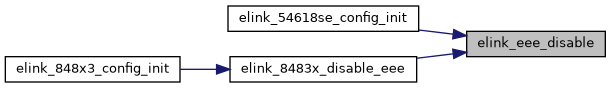

| static elink_status_t | elink_eee_disable (struct elink_phy *phy, struct elink_params *params, struct elink_vars *vars) |

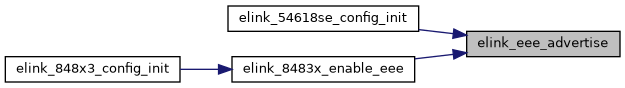

| static elink_status_t | elink_eee_advertise (struct elink_phy *phy, struct elink_params *params, struct elink_vars *vars, uint8_t modes) |

| static void | elink_update_mng_eee (struct elink_params *params, uint32_t eee_status) |

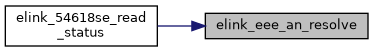

| static void | elink_eee_an_resolve (struct elink_phy *phy, struct elink_params *params, struct elink_vars *vars) |

| static void | elink_bsc_module_sel (struct elink_params *params) |

| static elink_status_t | elink_bsc_read (struct bxe_softc *sc, uint8_t sl_devid, uint16_t sl_addr, uint8_t lc_addr, uint8_t xfer_cnt, uint32_t *data_array) |

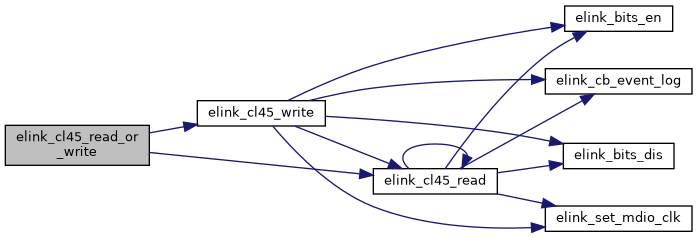

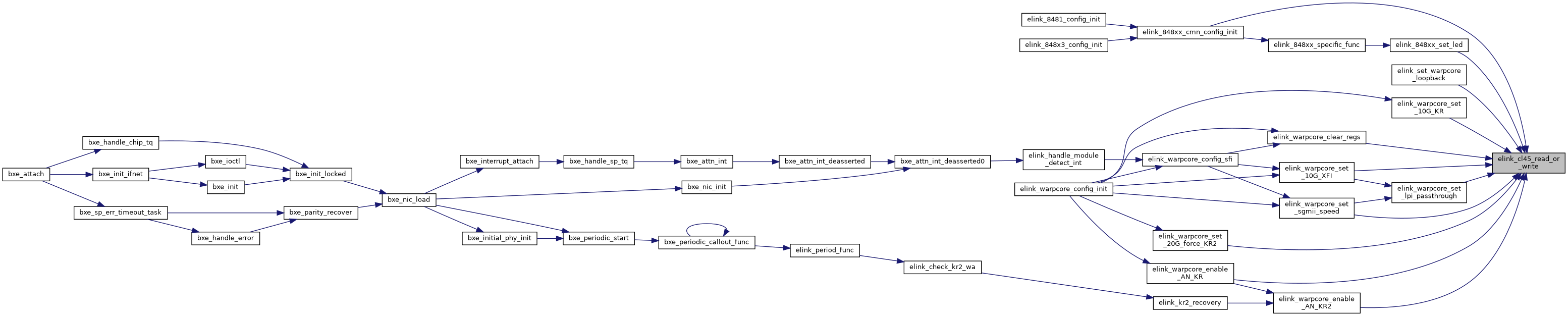

| static void | elink_cl45_read_or_write (struct bxe_softc *sc, struct elink_phy *phy, uint8_t devad, uint16_t reg, uint16_t or_val) |

| static void | elink_cl45_read_and_write (struct bxe_softc *sc, struct elink_phy *phy, uint8_t devad, uint16_t reg, uint16_t and_val) |

| elink_status_t | elink_phy_read (struct elink_params *params, uint8_t phy_addr, uint8_t devad, uint16_t reg, uint16_t *ret_val) |

| elink_status_t | elink_phy_write (struct elink_params *params, uint8_t phy_addr, uint8_t devad, uint16_t reg, uint16_t val) |

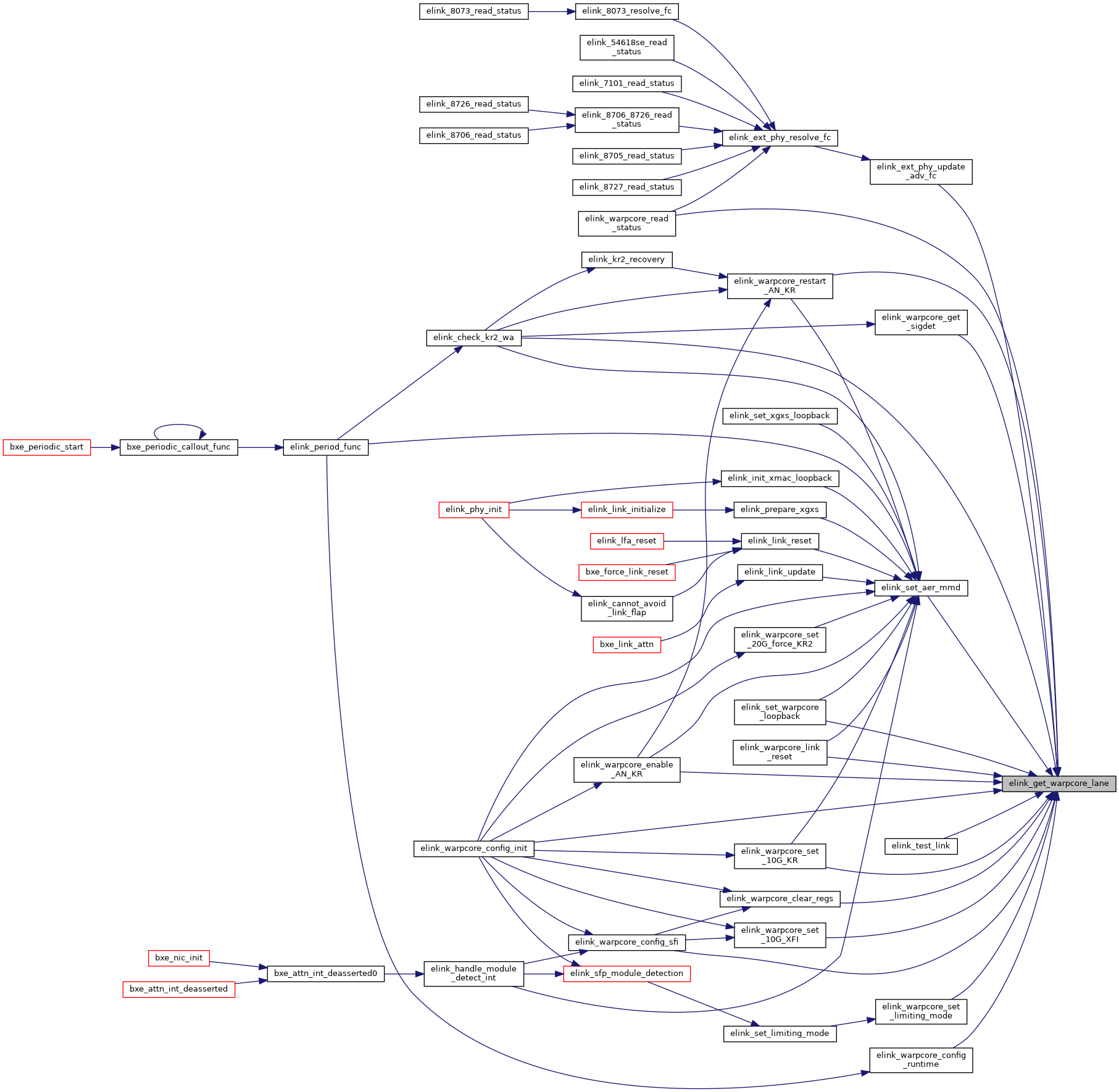

| static uint8_t | elink_get_warpcore_lane (struct elink_phy *phy, struct elink_params *params) |

| static void | elink_set_aer_mmd (struct elink_params *params, struct elink_phy *phy) |

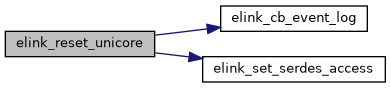

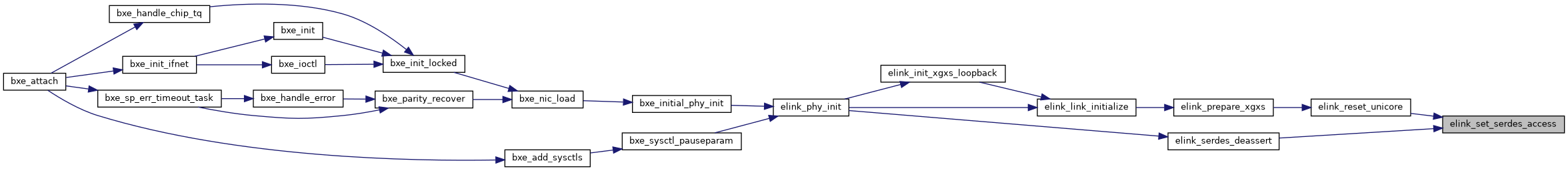

| static void | elink_set_serdes_access (struct bxe_softc *sc, uint8_t port) |

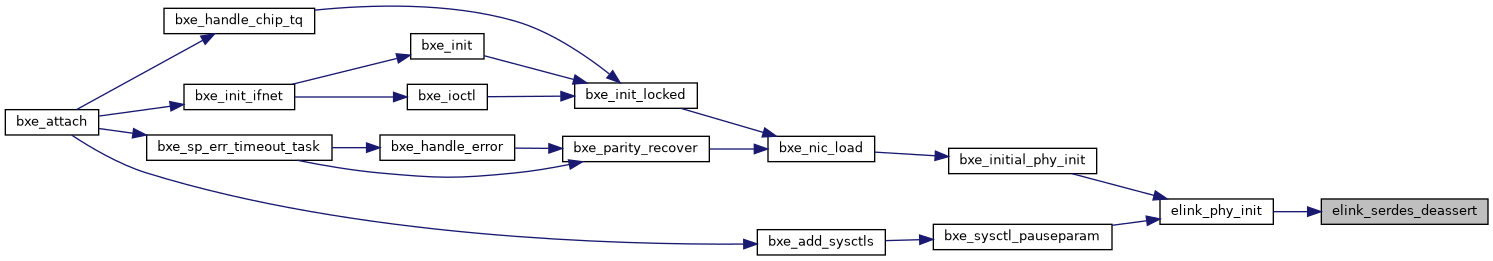

| static void | elink_serdes_deassert (struct bxe_softc *sc, uint8_t port) |

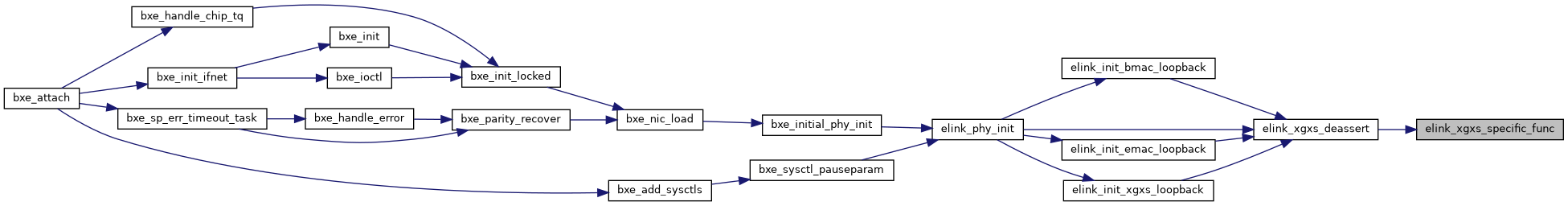

| static void | elink_xgxs_specific_func (struct elink_phy *phy, struct elink_params *params, uint32_t action) |

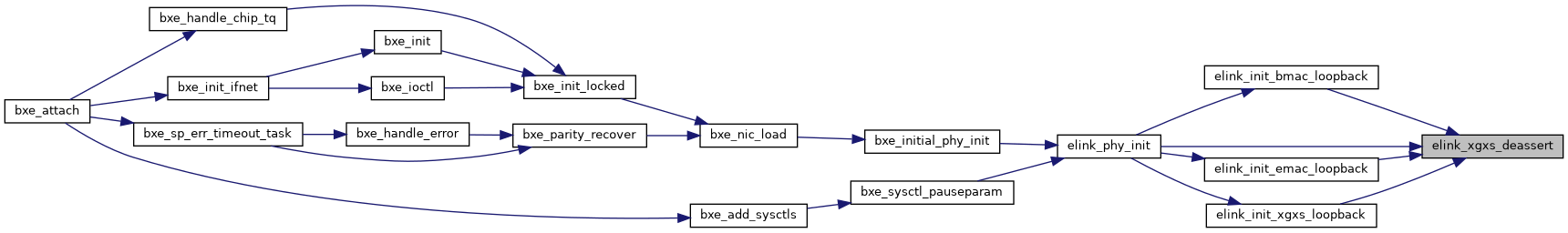

| static void | elink_xgxs_deassert (struct elink_params *params) |

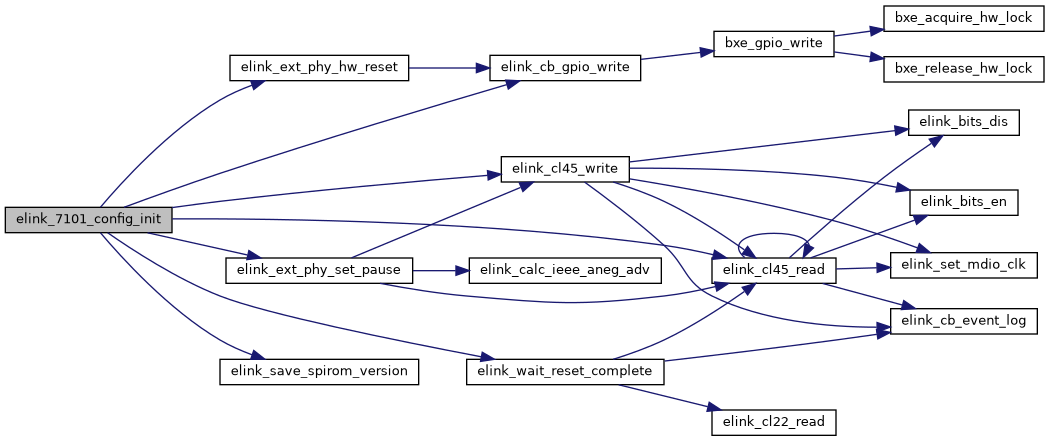

| static void | elink_calc_ieee_aneg_adv (struct elink_phy *phy, struct elink_params *params, uint16_t *ieee_fc) |

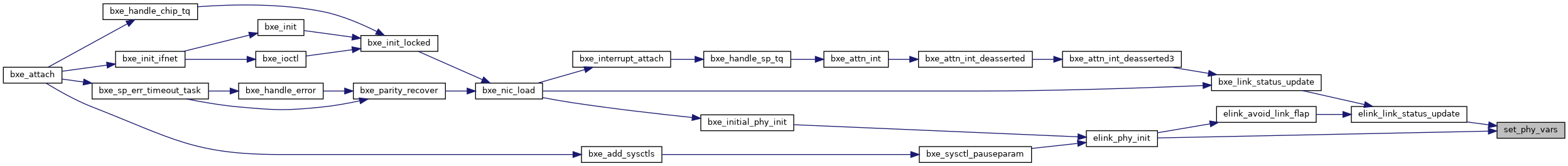

| static void | set_phy_vars (struct elink_params *params, struct elink_vars *vars) |

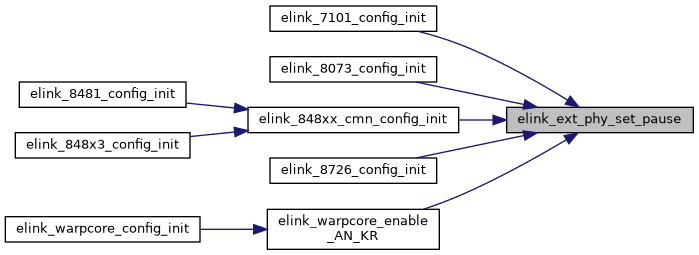

| static void | elink_ext_phy_set_pause (struct elink_params *params, struct elink_phy *phy, struct elink_vars *vars) |

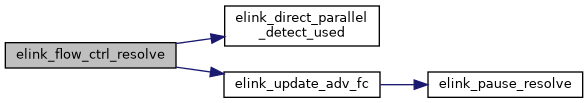

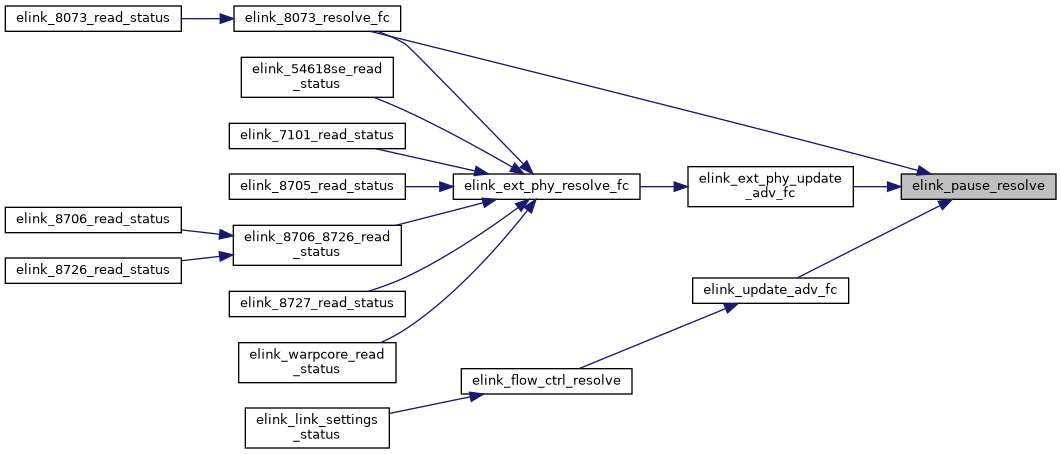

| static void | elink_pause_resolve (struct elink_phy *phy, struct elink_params *params, struct elink_vars *vars, uint32_t pause_result) |

| static void | elink_ext_phy_update_adv_fc (struct elink_phy *phy, struct elink_params *params, struct elink_vars *vars) |

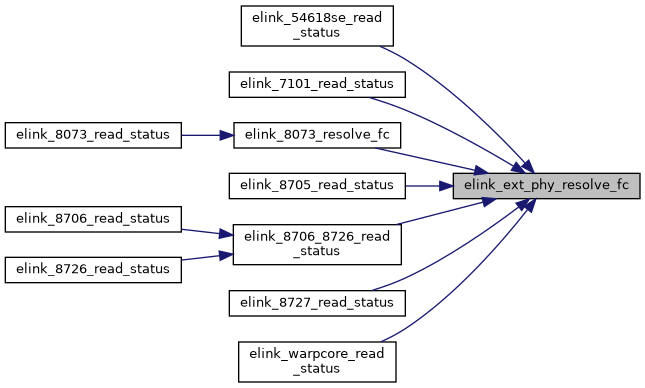

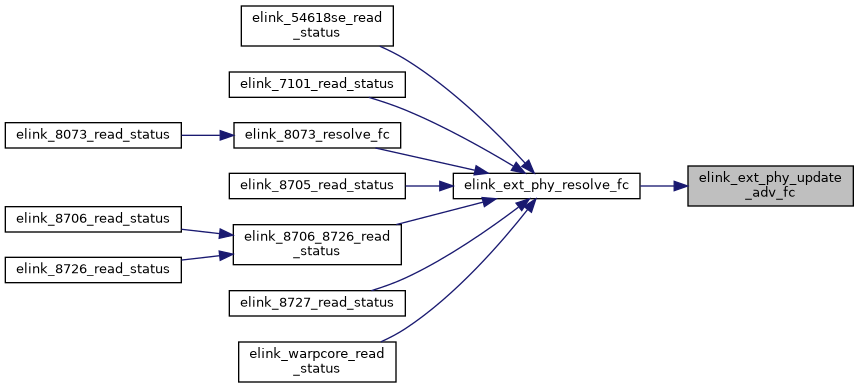

| static uint8_t | elink_ext_phy_resolve_fc (struct elink_phy *phy, struct elink_params *params, struct elink_vars *vars) |

| static void | elink_update_link_attr (struct elink_params *params, uint32_t link_attr) |

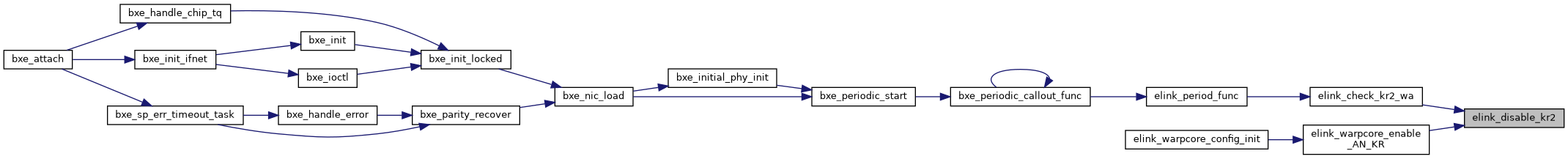

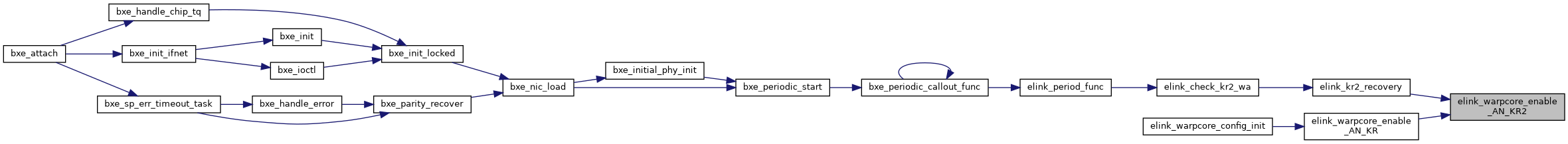

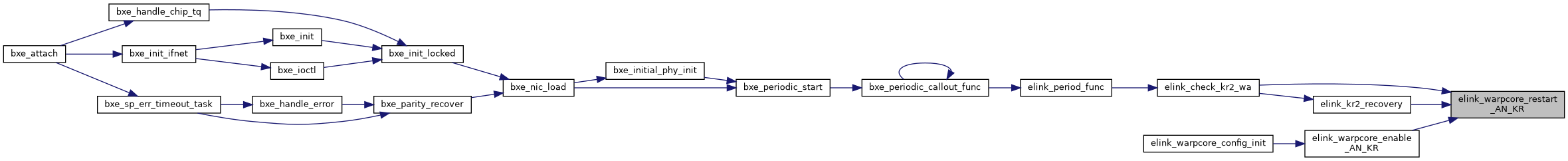

| static void | elink_warpcore_enable_AN_KR2 (struct elink_phy *phy, struct elink_params *params, struct elink_vars *vars) |

| static void | elink_disable_kr2 (struct elink_params *params, struct elink_vars *vars, struct elink_phy *phy) |

| static void | elink_warpcore_set_lpi_passthrough (struct elink_phy *phy, struct elink_params *params) |

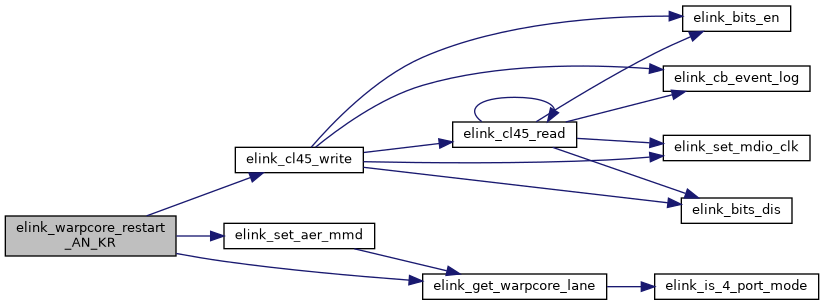

| static void | elink_warpcore_restart_AN_KR (struct elink_phy *phy, struct elink_params *params) |

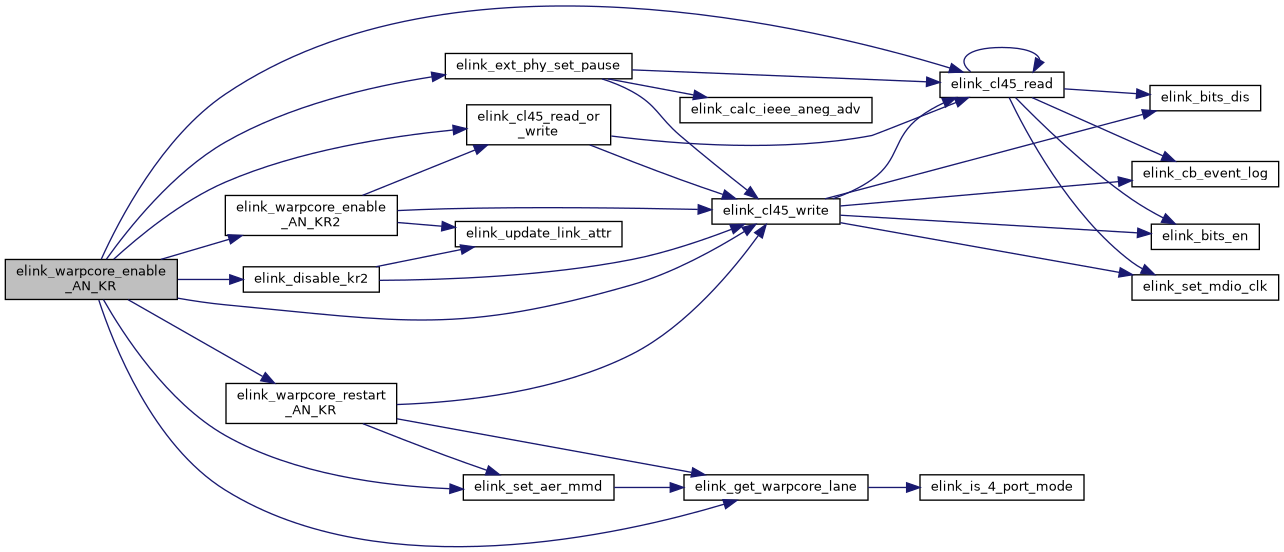

| static void | elink_warpcore_enable_AN_KR (struct elink_phy *phy, struct elink_params *params, struct elink_vars *vars) |

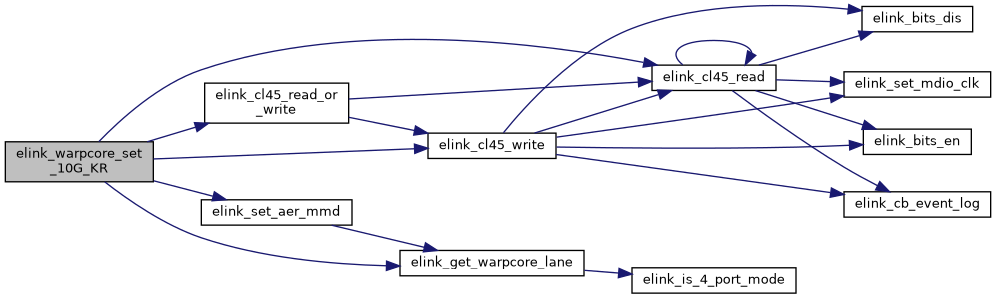

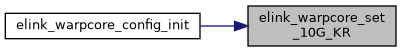

| static void | elink_warpcore_set_10G_KR (struct elink_phy *phy, struct elink_params *params, struct elink_vars *vars) |

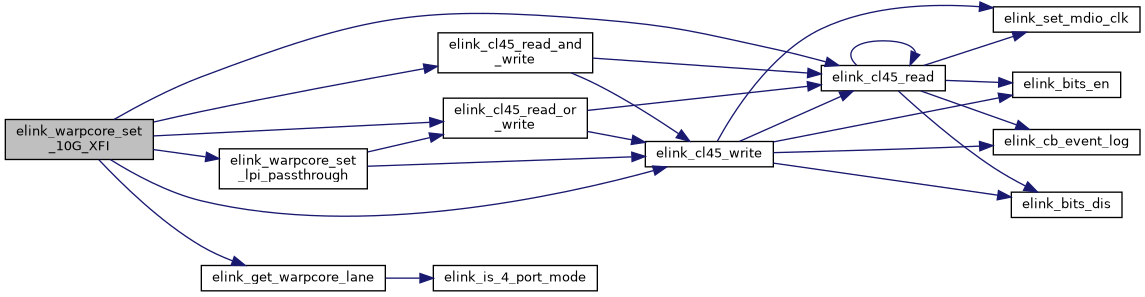

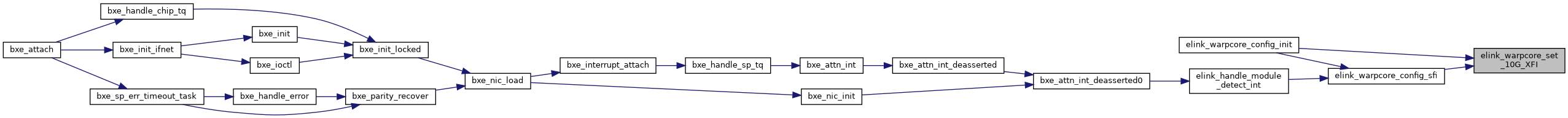

| static void | elink_warpcore_set_10G_XFI (struct elink_phy *phy, struct elink_params *params, uint8_t is_xfi) |

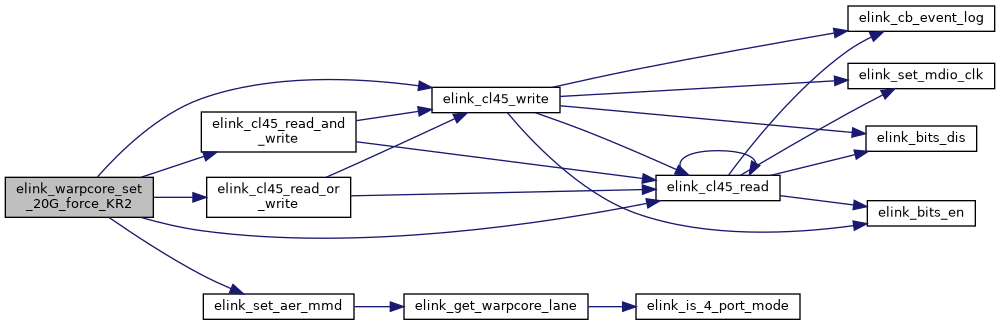

| static void | elink_warpcore_set_20G_force_KR2 (struct elink_phy *phy, struct elink_params *params) |

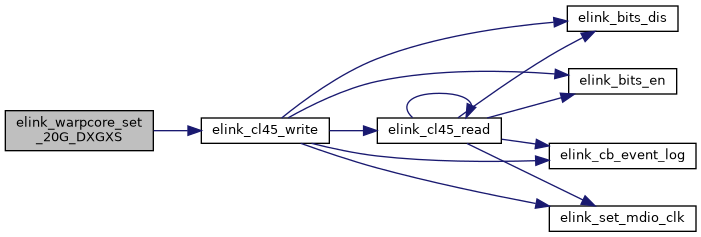

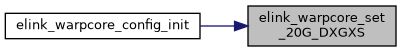

| static void | elink_warpcore_set_20G_DXGXS (struct bxe_softc *sc, struct elink_phy *phy, uint16_t lane) |

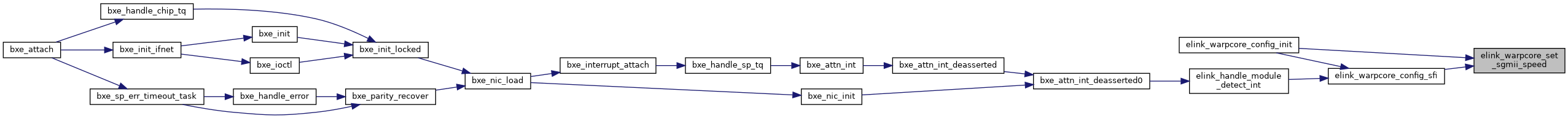

| static void | elink_warpcore_set_sgmii_speed (struct elink_phy *phy, struct elink_params *params, uint8_t fiber_mode, uint8_t always_autoneg) |

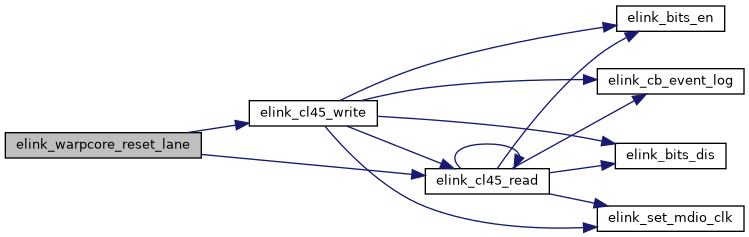

| static void | elink_warpcore_reset_lane (struct bxe_softc *sc, struct elink_phy *phy, uint8_t reset) |

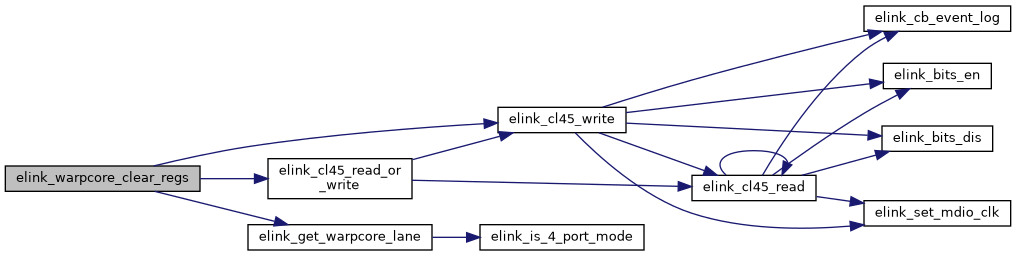

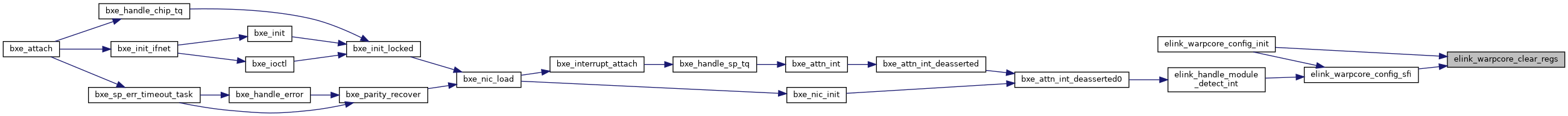

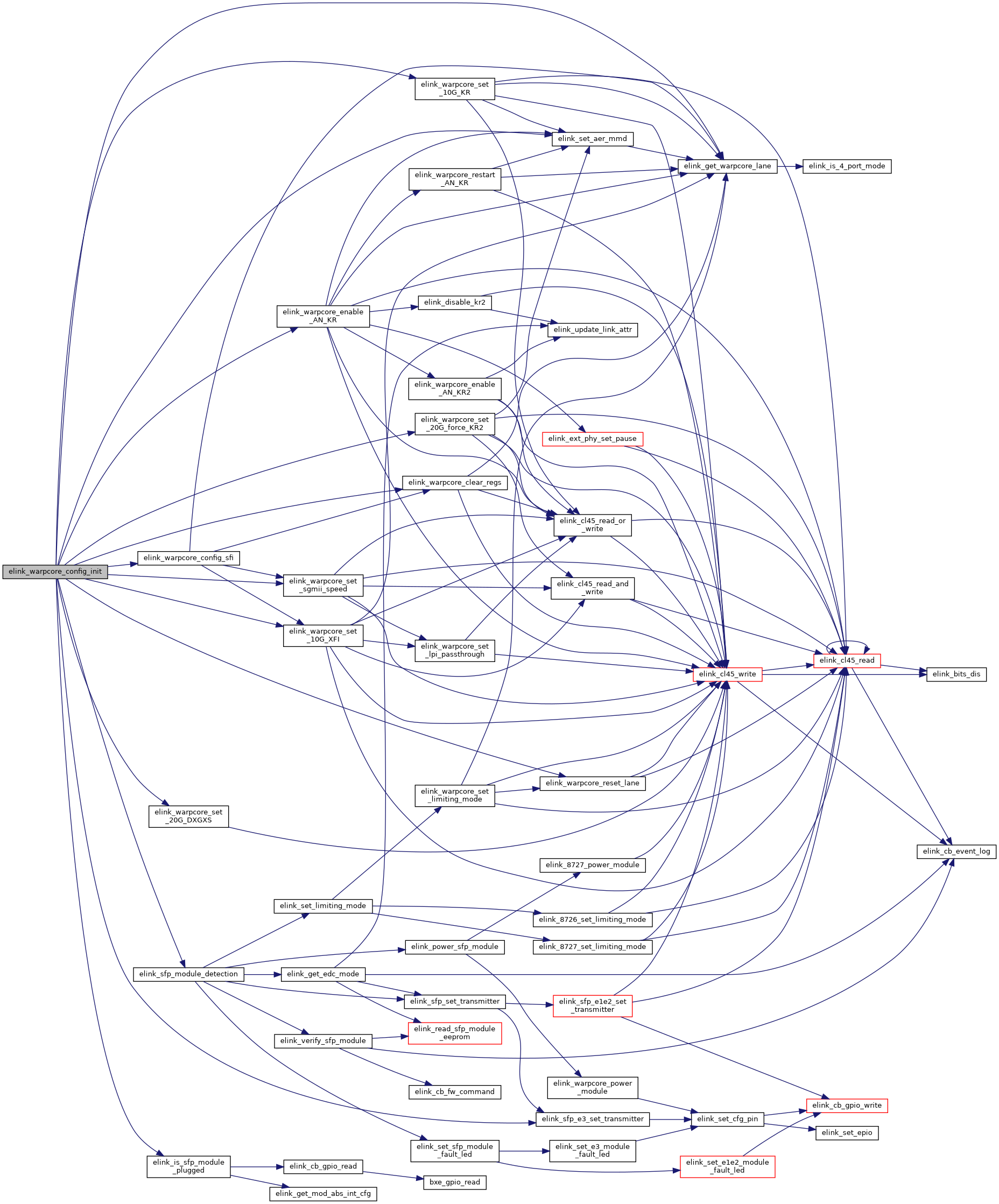

| static void | elink_warpcore_clear_regs (struct elink_phy *phy, struct elink_params *params, uint16_t lane) |

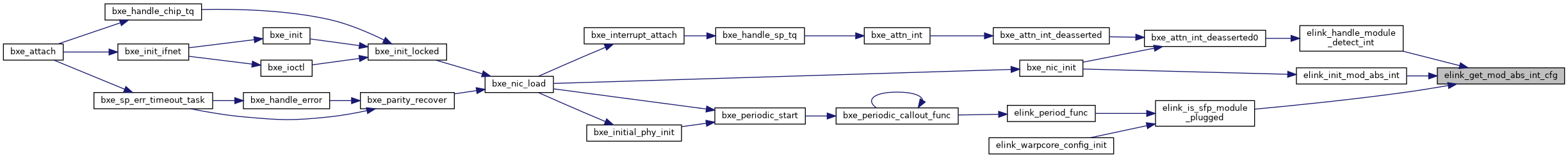

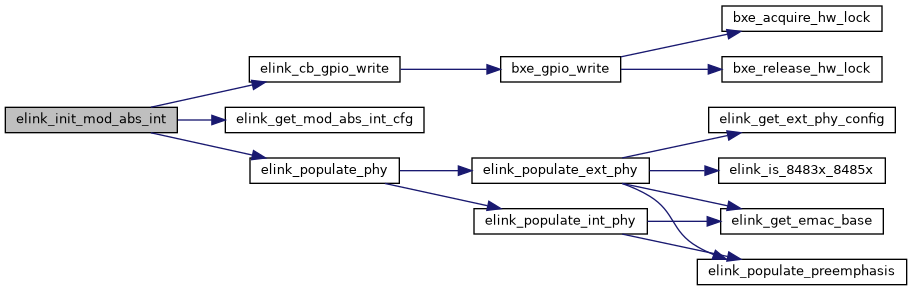

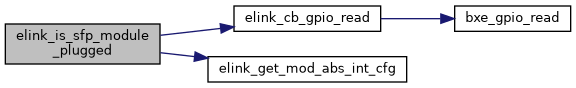

| static elink_status_t | elink_get_mod_abs_int_cfg (struct bxe_softc *sc, uint32_t chip_id, uint32_t shmem_base, uint8_t port, uint8_t *gpio_num, uint8_t *gpio_port) |

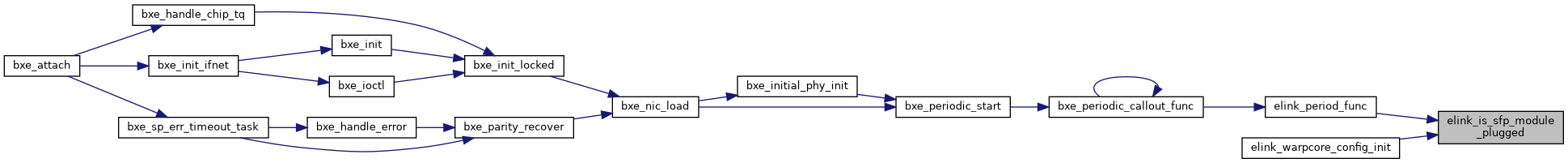

| static int | elink_is_sfp_module_plugged (struct elink_phy *phy, struct elink_params *params) |

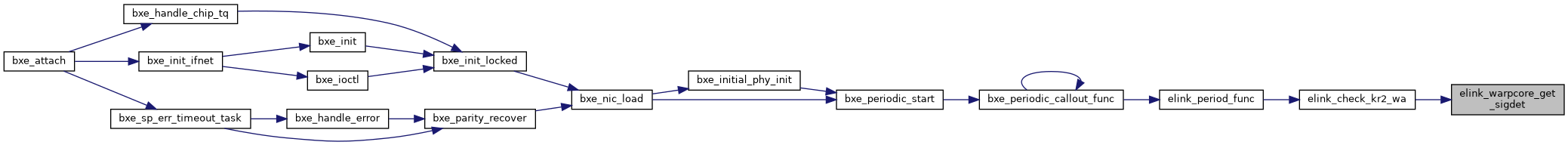

| static int | elink_warpcore_get_sigdet (struct elink_phy *phy, struct elink_params *params) |

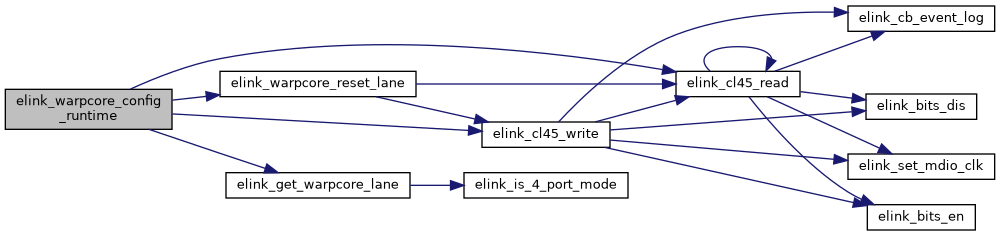

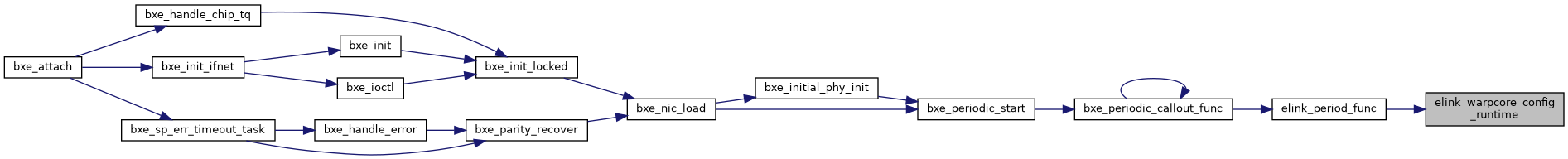

| static void | elink_warpcore_config_runtime (struct elink_phy *phy, struct elink_params *params, struct elink_vars *vars) |

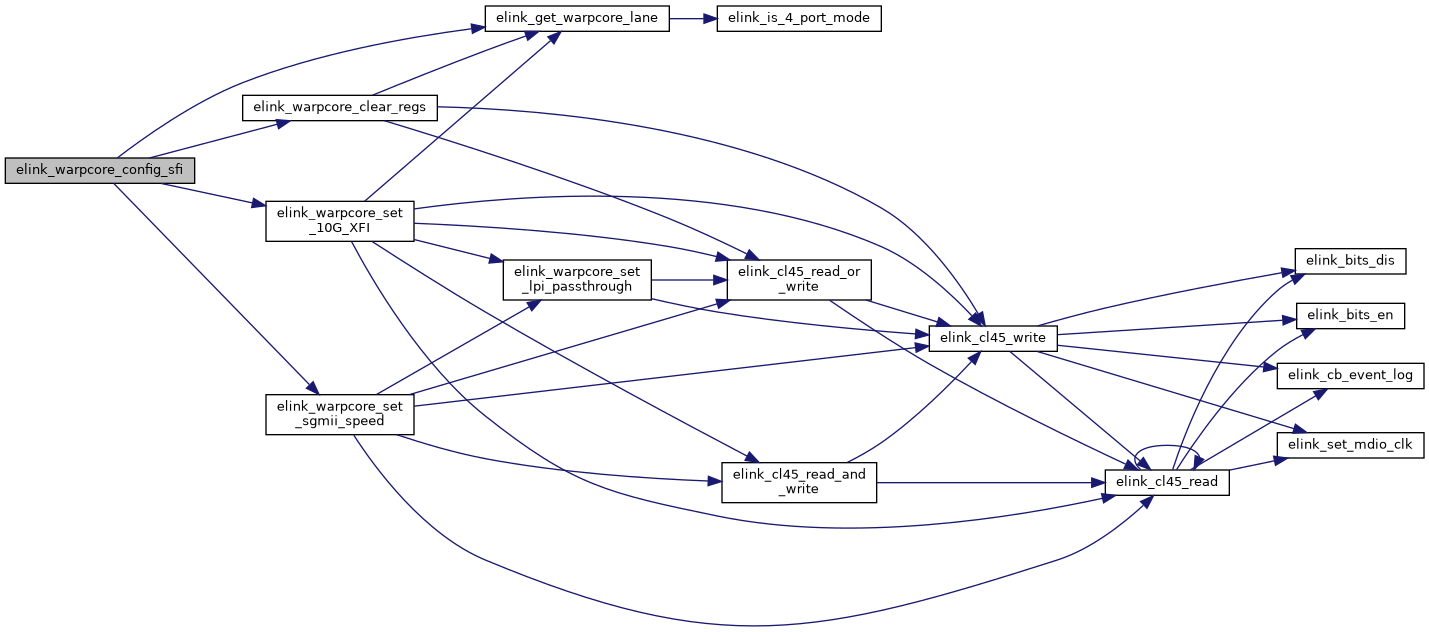

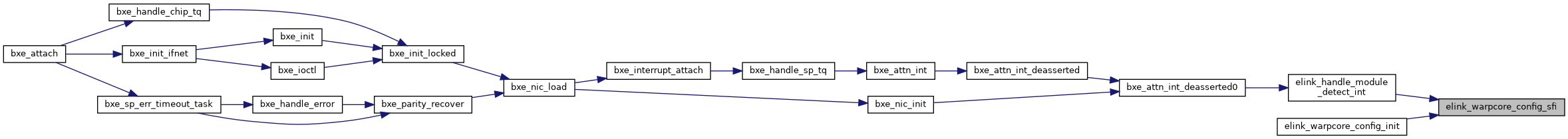

| static void | elink_warpcore_config_sfi (struct elink_phy *phy, struct elink_params *params) |

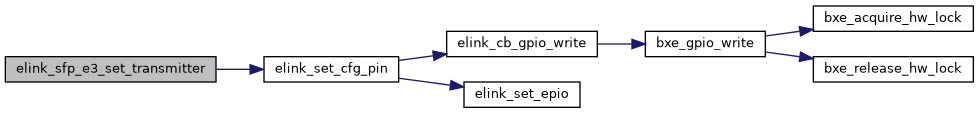

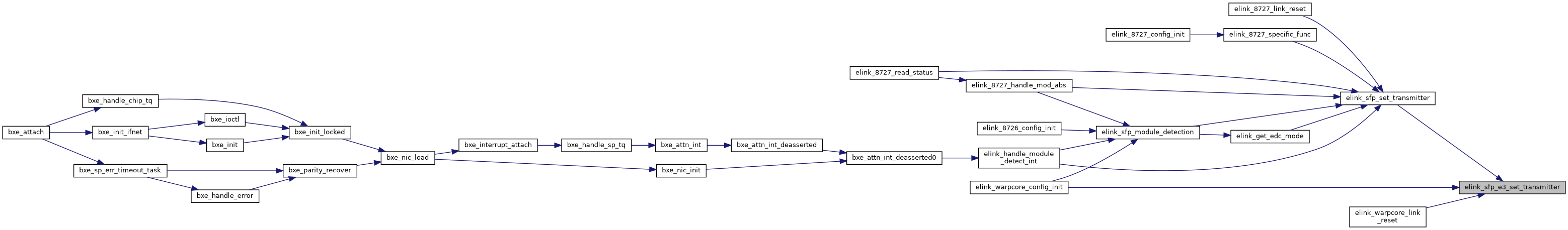

| static void | elink_sfp_e3_set_transmitter (struct elink_params *params, struct elink_phy *phy, uint8_t tx_en) |

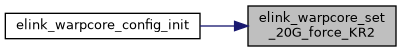

| static void | elink_warpcore_config_init (struct elink_phy *phy, struct elink_params *params, struct elink_vars *vars) |

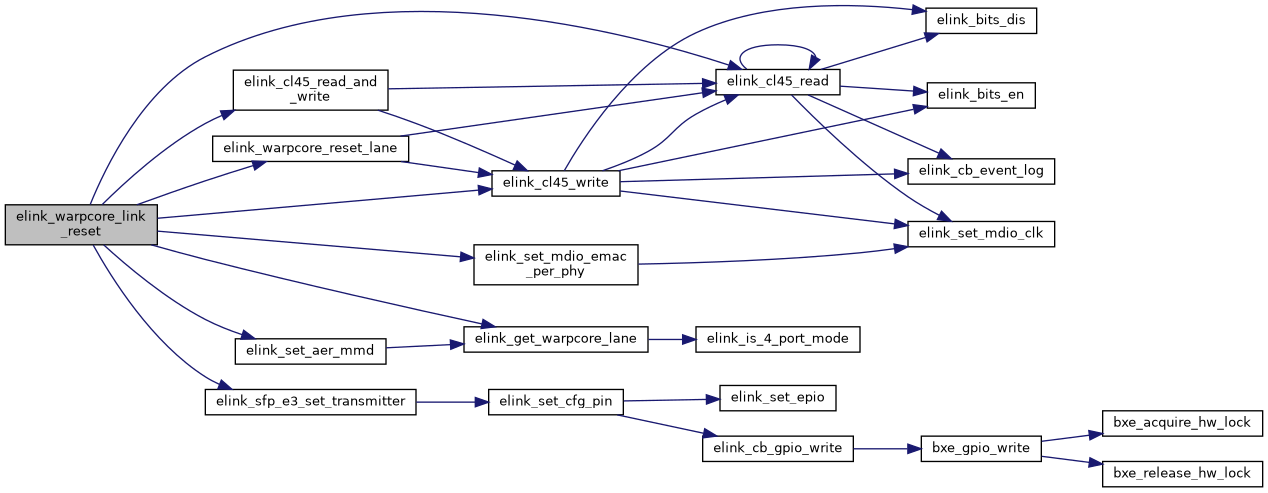

| static void | elink_warpcore_link_reset (struct elink_phy *phy, struct elink_params *params) |

| static void | elink_set_warpcore_loopback (struct elink_phy *phy, struct elink_params *params) |

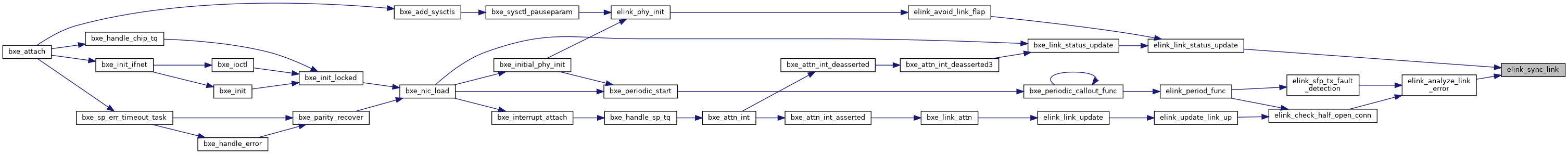

| static void | elink_sync_link (struct elink_params *params, struct elink_vars *vars) |

| void | elink_link_status_update (struct elink_params *params, struct elink_vars *vars) |

| static void | elink_set_master_ln (struct elink_params *params, struct elink_phy *phy) |

| static elink_status_t | elink_reset_unicore (struct elink_params *params, struct elink_phy *phy, uint8_t set_serdes) |

| static void | elink_set_swap_lanes (struct elink_params *params, struct elink_phy *phy) |

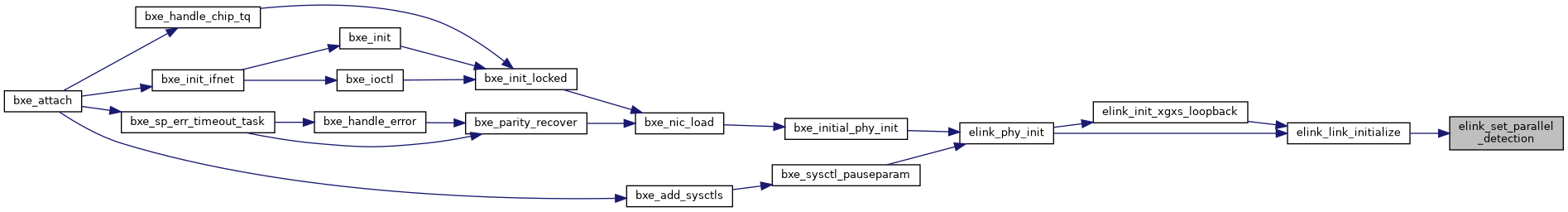

| static void | elink_set_parallel_detection (struct elink_phy *phy, struct elink_params *params) |

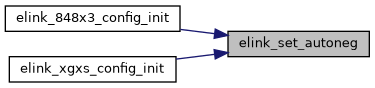

| static void | elink_set_autoneg (struct elink_phy *phy, struct elink_params *params, struct elink_vars *vars, uint8_t enable_cl73) |

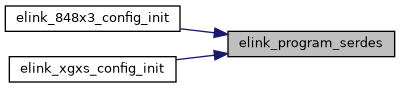

| static void | elink_program_serdes (struct elink_phy *phy, struct elink_params *params, struct elink_vars *vars) |

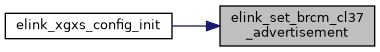

| static void | elink_set_brcm_cl37_advertisement (struct elink_phy *phy, struct elink_params *params) |

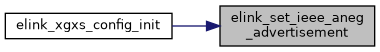

| static void | elink_set_ieee_aneg_advertisement (struct elink_phy *phy, struct elink_params *params, uint16_t ieee_fc) |

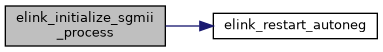

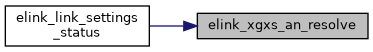

| static void | elink_restart_autoneg (struct elink_phy *phy, struct elink_params *params, uint8_t enable_cl73) |

| static void | elink_initialize_sgmii_process (struct elink_phy *phy, struct elink_params *params, struct elink_vars *vars) |

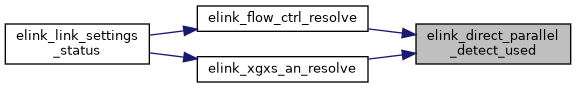

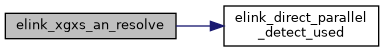

| static elink_status_t | elink_direct_parallel_detect_used (struct elink_phy *phy, struct elink_params *params) |

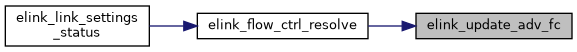

| static void | elink_update_adv_fc (struct elink_phy *phy, struct elink_params *params, struct elink_vars *vars, uint32_t gp_status) |

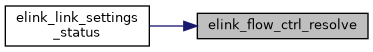

| static void | elink_flow_ctrl_resolve (struct elink_phy *phy, struct elink_params *params, struct elink_vars *vars, uint32_t gp_status) |

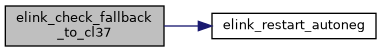

| static void | elink_check_fallback_to_cl37 (struct elink_phy *phy, struct elink_params *params) |

| static void | elink_xgxs_an_resolve (struct elink_phy *phy, struct elink_params *params, struct elink_vars *vars, uint32_t gp_status) |

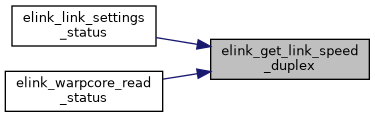

| static elink_status_t | elink_get_link_speed_duplex (struct elink_phy *phy, struct elink_params *params, struct elink_vars *vars, uint16_t is_link_up, uint16_t speed_mask, uint16_t is_duplex) |

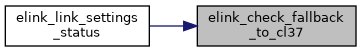

| static elink_status_t | elink_link_settings_status (struct elink_phy *phy, struct elink_params *params, struct elink_vars *vars) |

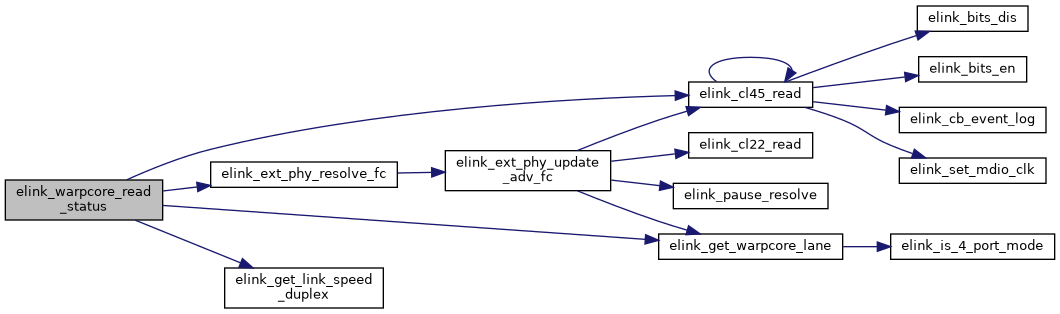

| static elink_status_t | elink_warpcore_read_status (struct elink_phy *phy, struct elink_params *params, struct elink_vars *vars) |

| static void | elink_set_gmii_tx_driver (struct elink_params *params) |

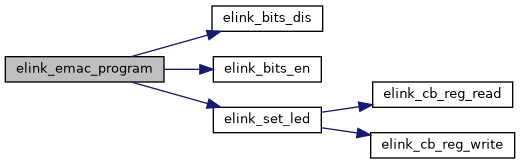

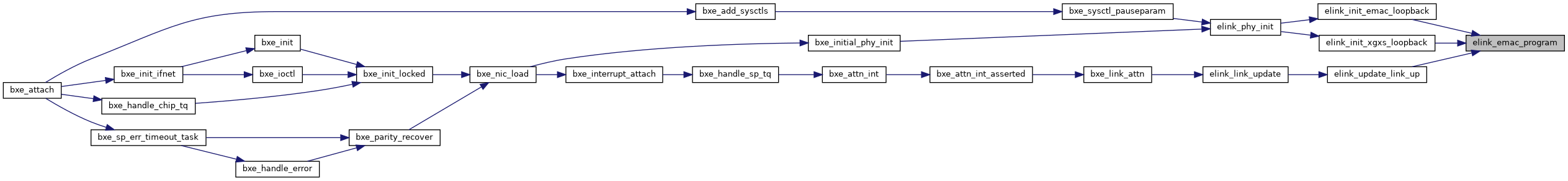

| static elink_status_t | elink_emac_program (struct elink_params *params, struct elink_vars *vars) |

| static void | elink_set_preemphasis (struct elink_phy *phy, struct elink_params *params) |

| static void | elink_xgxs_config_init (struct elink_phy *phy, struct elink_params *params, struct elink_vars *vars) |

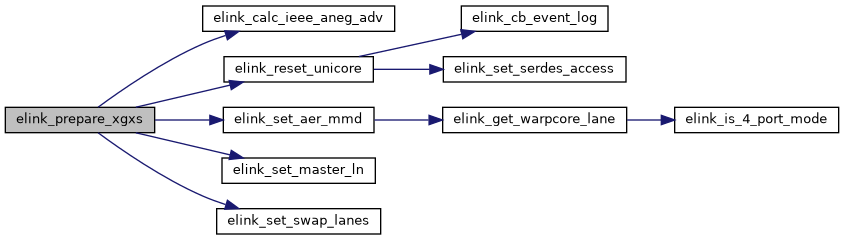

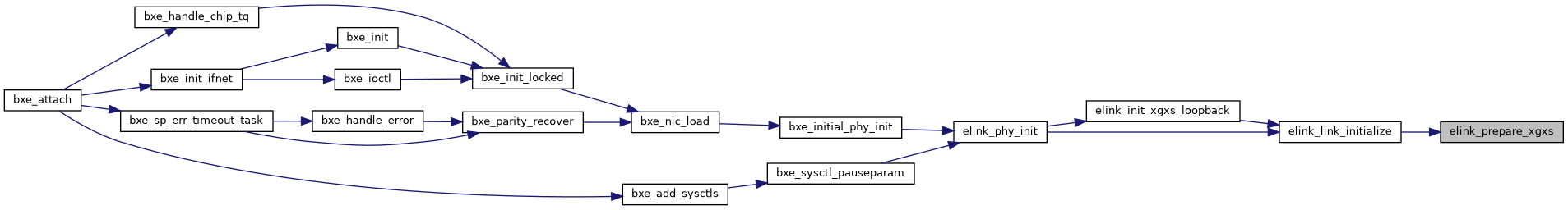

| static elink_status_t | elink_prepare_xgxs (struct elink_phy *phy, struct elink_params *params, struct elink_vars *vars) |

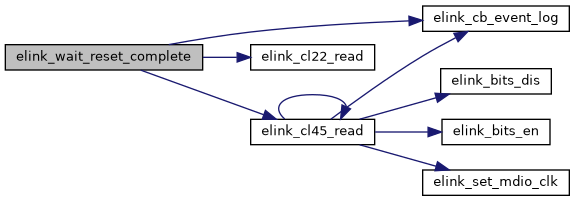

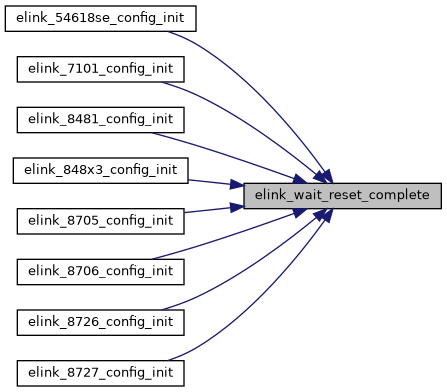

| static uint16_t | elink_wait_reset_complete (struct bxe_softc *sc, struct elink_phy *phy, struct elink_params *params) |

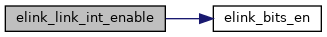

| static void | elink_link_int_enable (struct elink_params *params) |

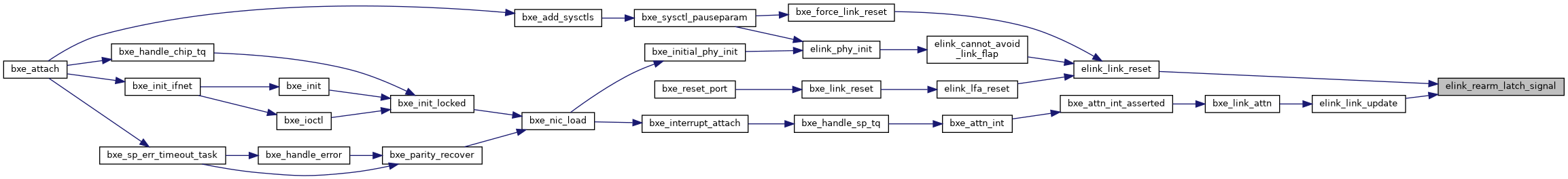

| static void | elink_rearm_latch_signal (struct bxe_softc *sc, uint8_t port, uint8_t exp_mi_int) |

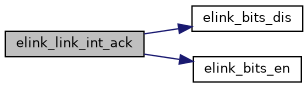

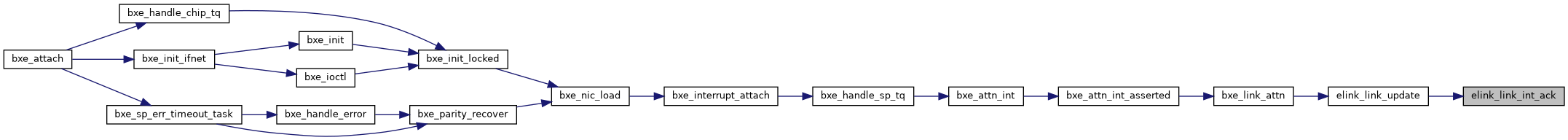

| static void | elink_link_int_ack (struct elink_params *params, struct elink_vars *vars, uint8_t is_10g_plus) |

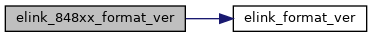

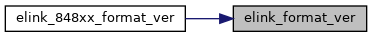

| static elink_status_t | elink_format_ver (uint32_t num, uint8_t *str, uint16_t *len) |

| static elink_status_t | elink_null_format_ver (uint32_t spirom_ver, uint8_t *str, uint16_t *len) |

| elink_status_t | elink_get_ext_phy_fw_version (struct elink_params *params, uint8_t *version, uint16_t len) |

| static void | elink_set_xgxs_loopback (struct elink_phy *phy, struct elink_params *params) |

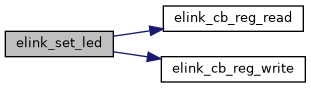

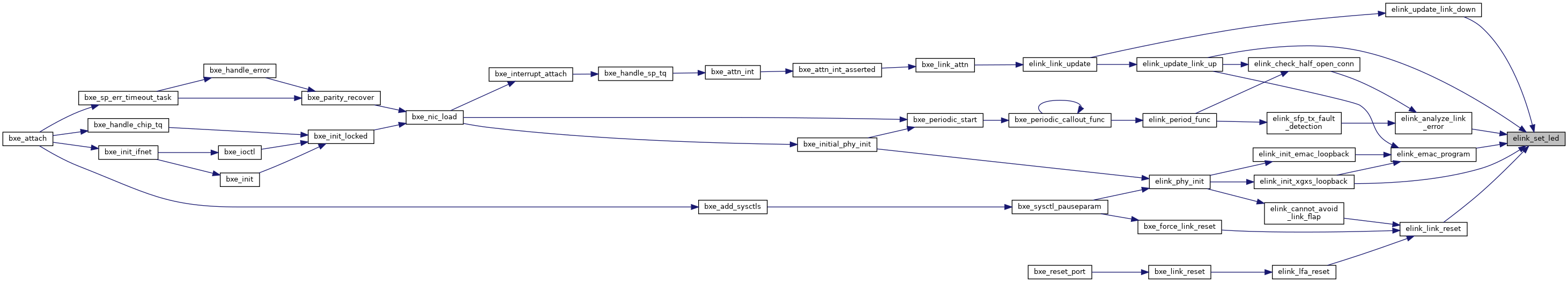

| elink_status_t | elink_set_led (struct elink_params *params, struct elink_vars *vars, uint8_t mode, uint32_t speed) |

| elink_status_t | elink_test_link (struct elink_params *params, struct elink_vars *vars, uint8_t is_serdes) |

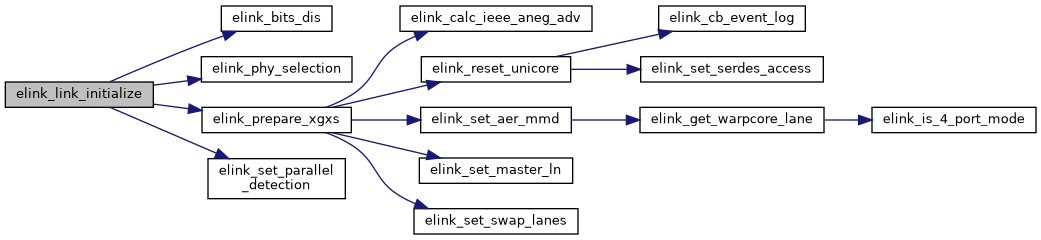

| static elink_status_t | elink_link_initialize (struct elink_params *params, struct elink_vars *vars) |

| static void | elink_int_link_reset (struct elink_phy *phy, struct elink_params *params) |

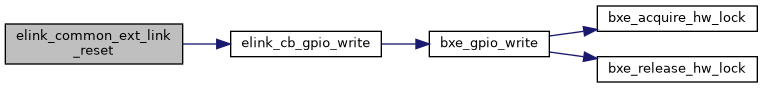

| static void | elink_common_ext_link_reset (struct elink_phy *phy, struct elink_params *params) |

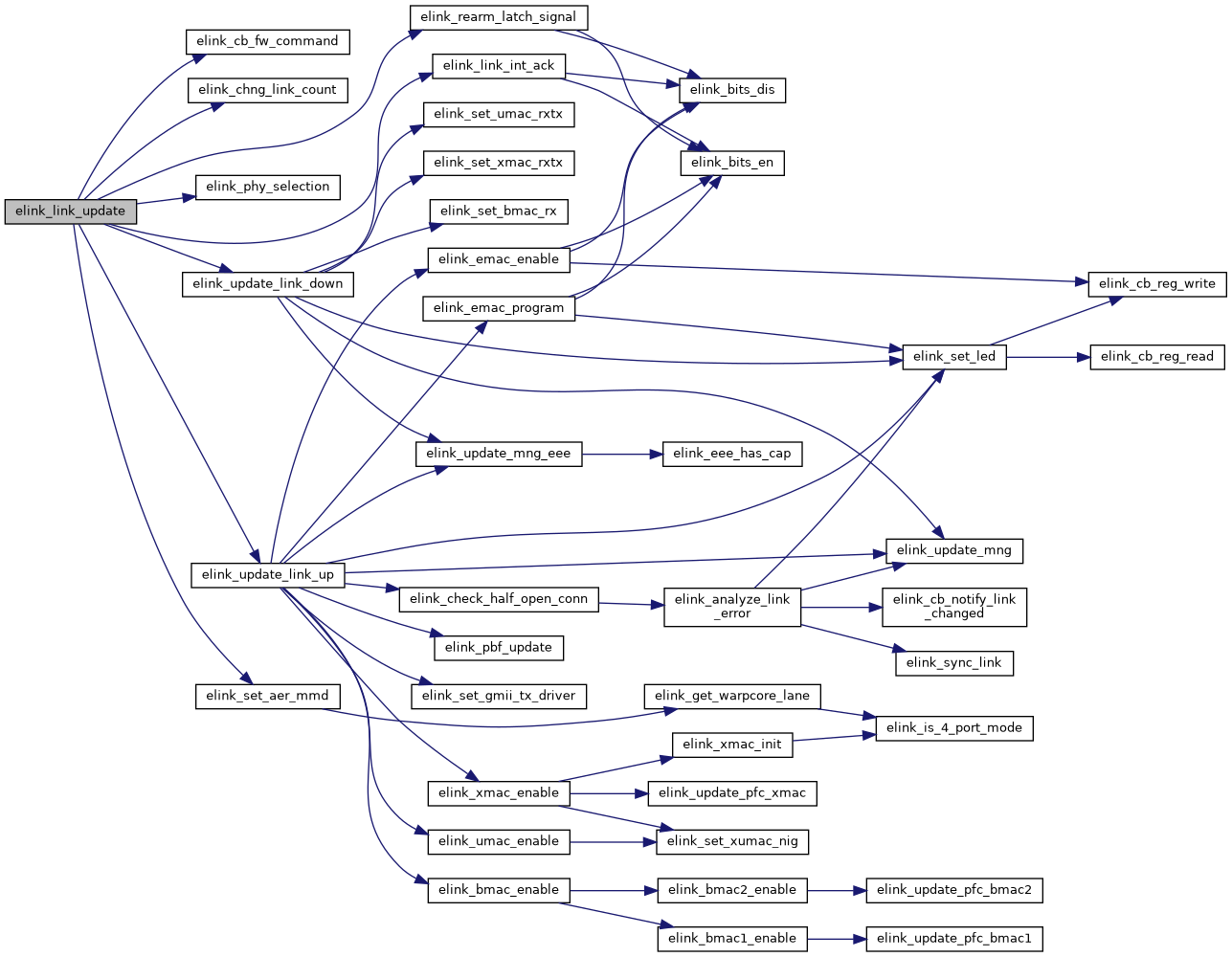

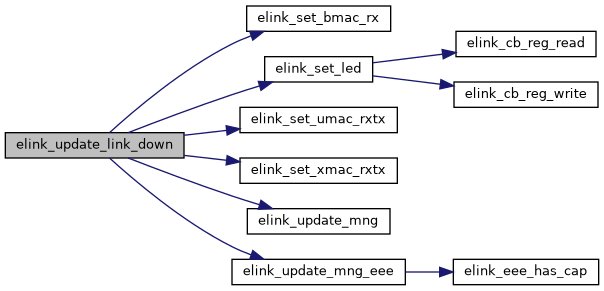

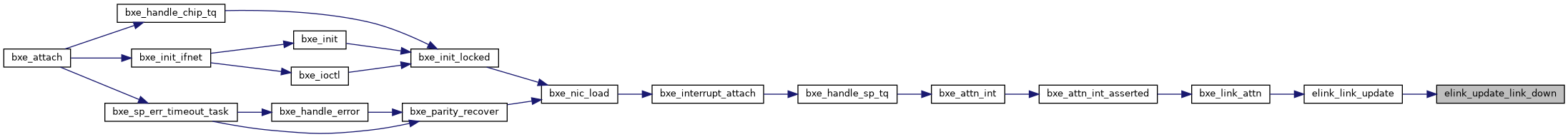

| static elink_status_t | elink_update_link_down (struct elink_params *params, struct elink_vars *vars) |

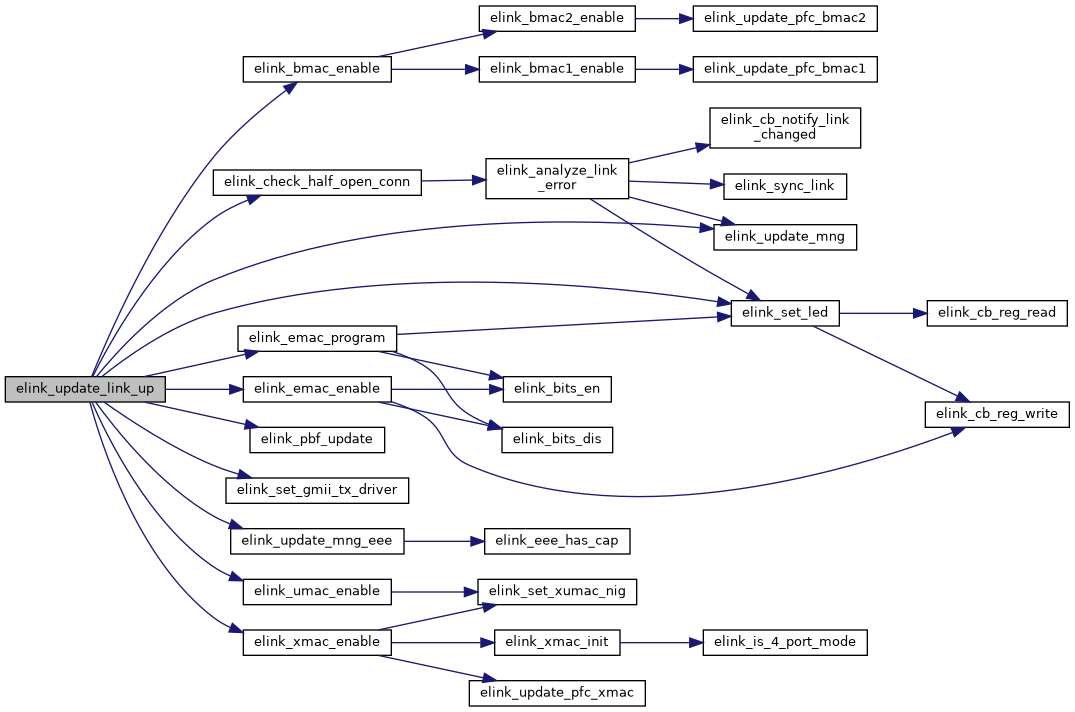

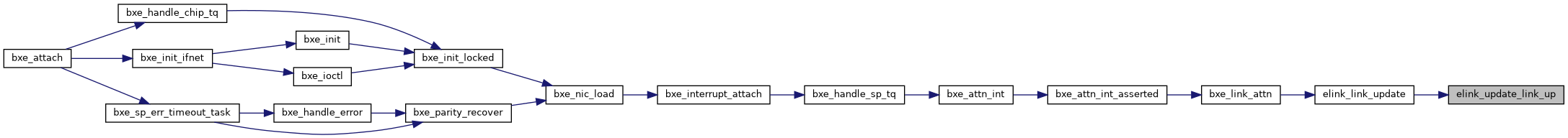

| static elink_status_t | elink_update_link_up (struct elink_params *params, struct elink_vars *vars, uint8_t link_10g) |

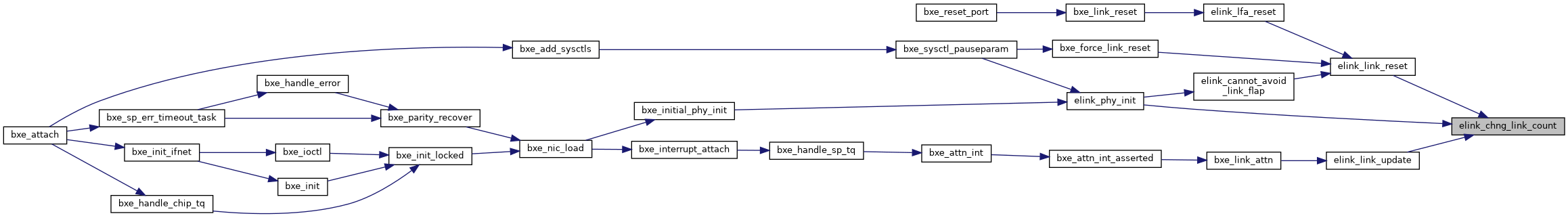

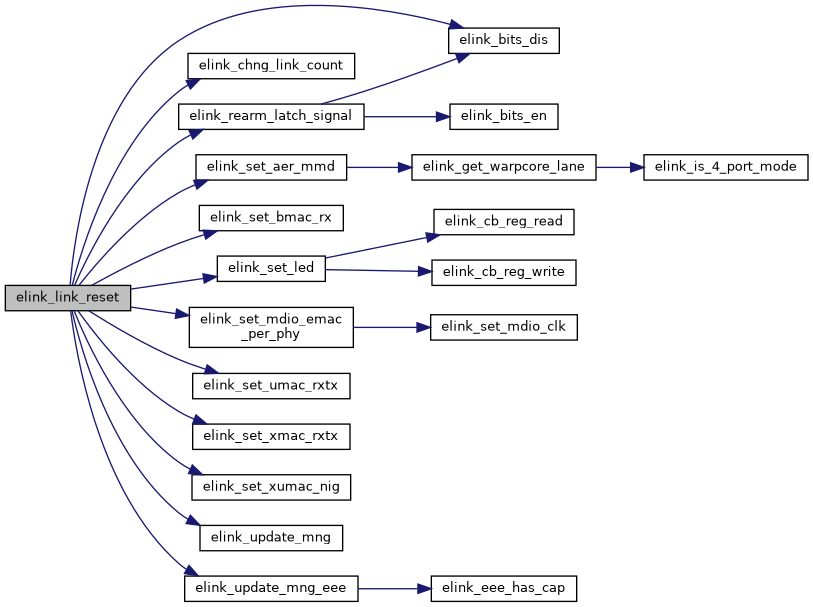

| static void | elink_chng_link_count (struct elink_params *params, uint8_t clear) |

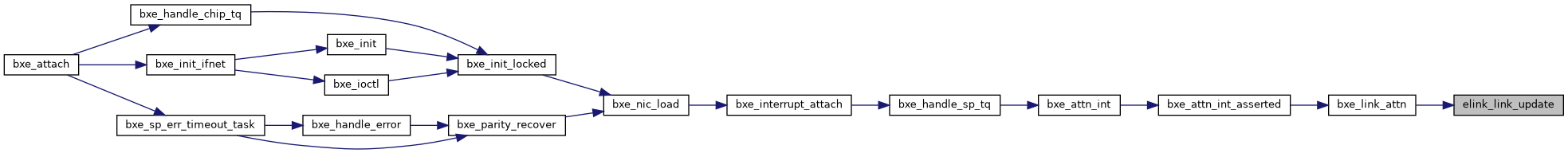

| elink_status_t | elink_link_update (struct elink_params *params, struct elink_vars *vars) |

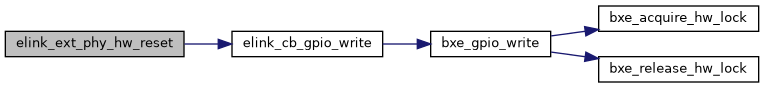

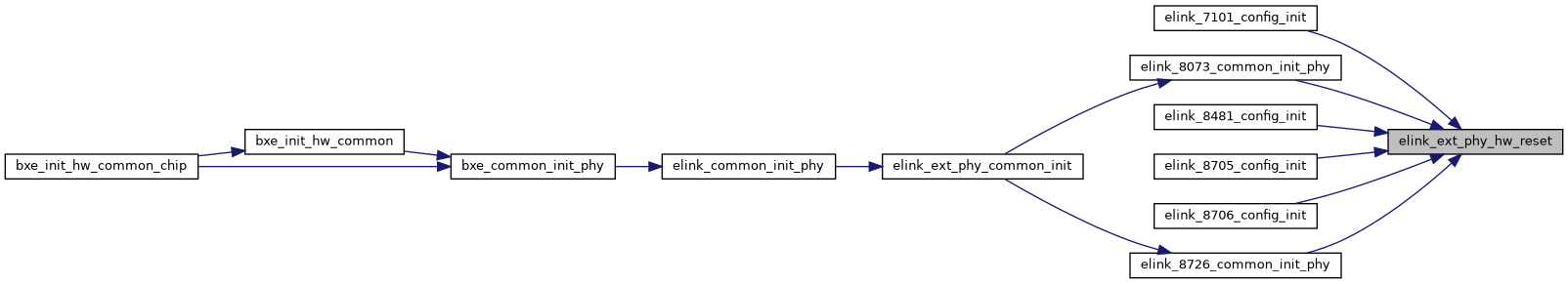

| void | elink_ext_phy_hw_reset (struct bxe_softc *sc, uint8_t port) |

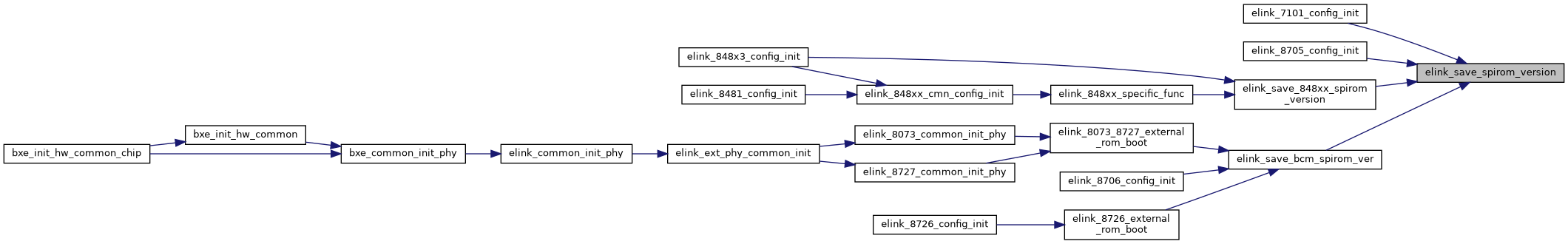

| static void | elink_save_spirom_version (struct bxe_softc *sc, uint8_t port, uint32_t spirom_ver, uint32_t ver_addr) |

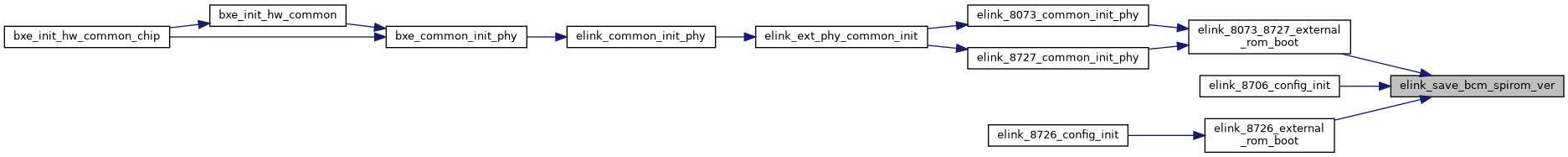

| static void | elink_save_bcm_spirom_ver (struct bxe_softc *sc, struct elink_phy *phy, uint8_t port) |

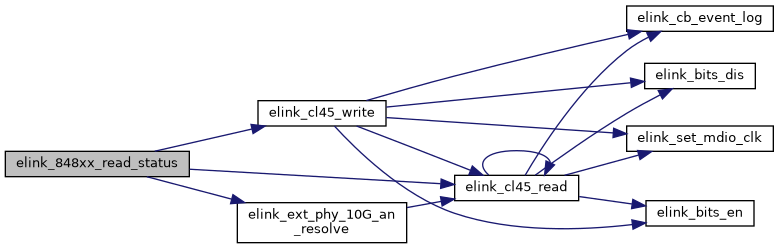

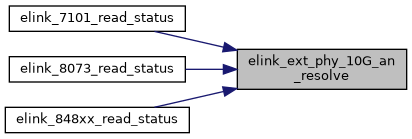

| static void | elink_ext_phy_10G_an_resolve (struct bxe_softc *sc, struct elink_phy *phy, struct elink_vars *vars) |

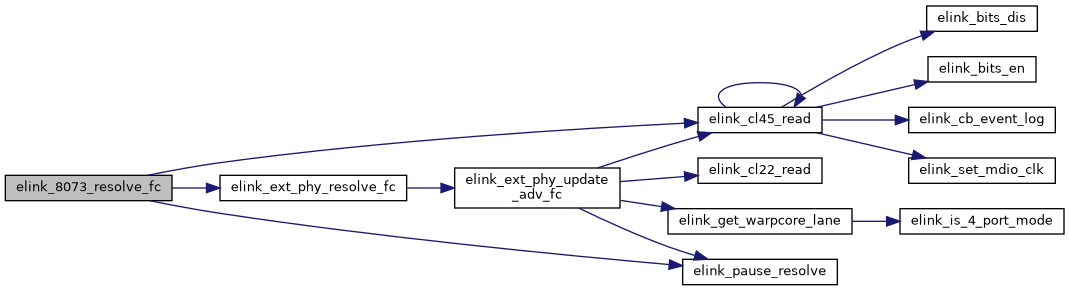

| static void | elink_8073_resolve_fc (struct elink_phy *phy, struct elink_params *params, struct elink_vars *vars) |

| static elink_status_t | elink_8073_8727_external_rom_boot (struct bxe_softc *sc, struct elink_phy *phy, uint8_t port) |

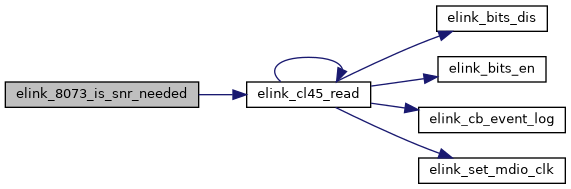

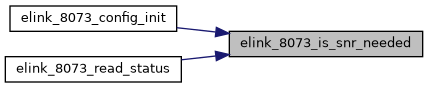

| static elink_status_t | elink_8073_is_snr_needed (struct bxe_softc *sc, struct elink_phy *phy) |

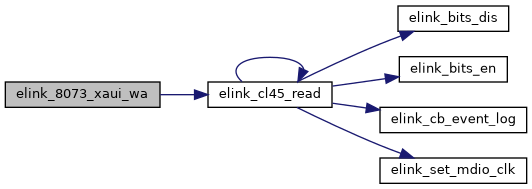

| static elink_status_t | elink_8073_xaui_wa (struct bxe_softc *sc, struct elink_phy *phy) |

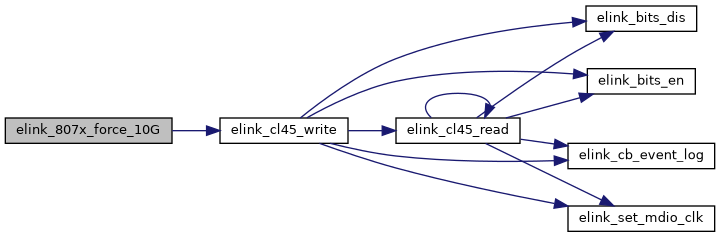

| static void | elink_807x_force_10G (struct bxe_softc *sc, struct elink_phy *phy) |

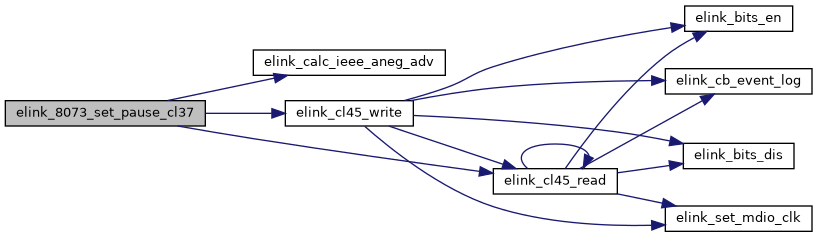

| static void | elink_8073_set_pause_cl37 (struct elink_params *params, struct elink_phy *phy, struct elink_vars *vars) |

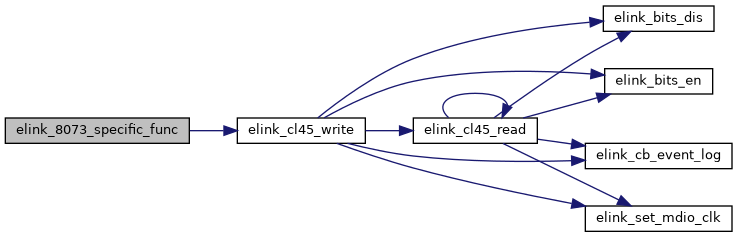

| static void | elink_8073_specific_func (struct elink_phy *phy, struct elink_params *params, uint32_t action) |

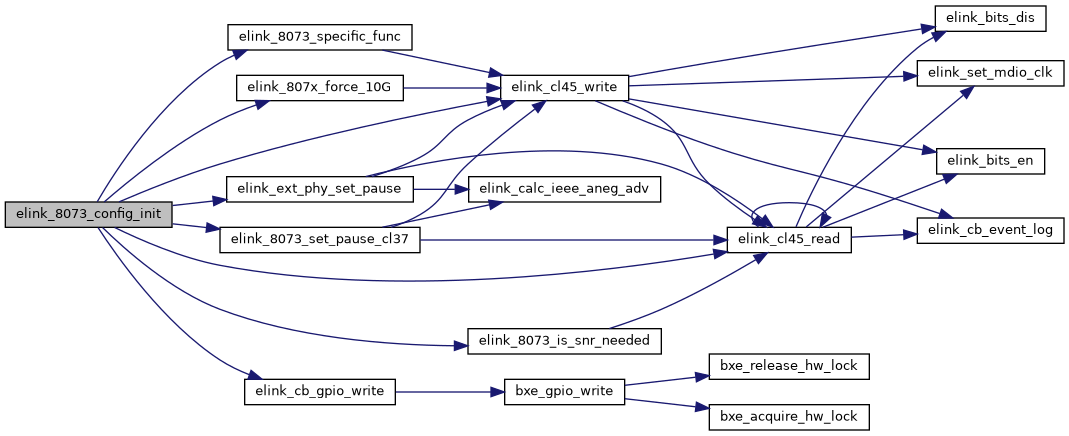

| static elink_status_t | elink_8073_config_init (struct elink_phy *phy, struct elink_params *params, struct elink_vars *vars) |

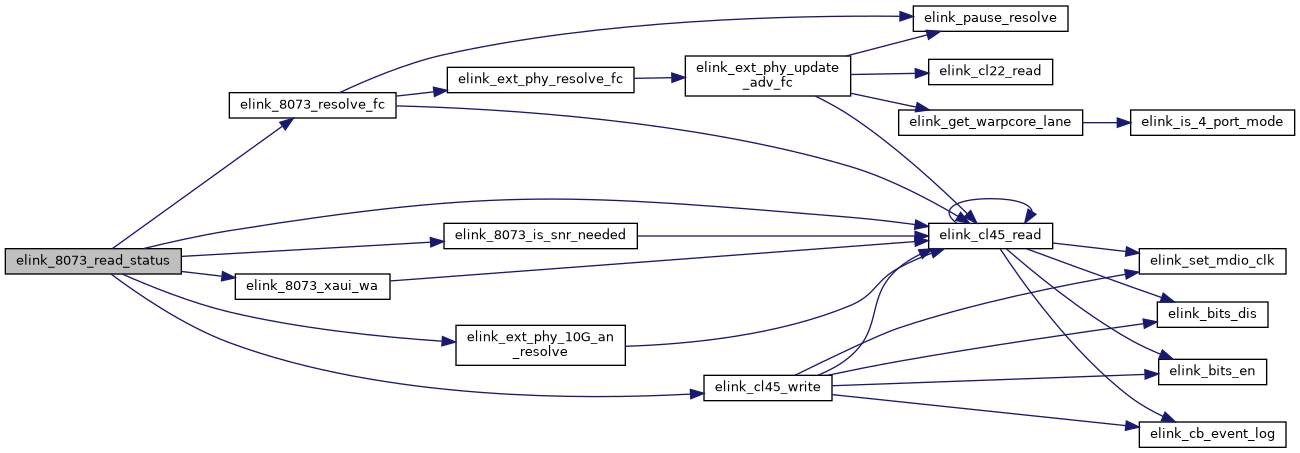

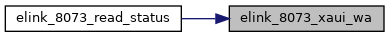

| static uint8_t | elink_8073_read_status (struct elink_phy *phy, struct elink_params *params, struct elink_vars *vars) |

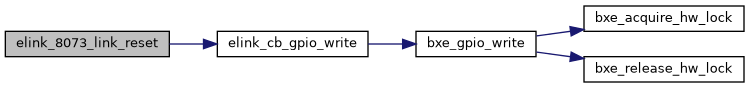

| static void | elink_8073_link_reset (struct elink_phy *phy, struct elink_params *params) |

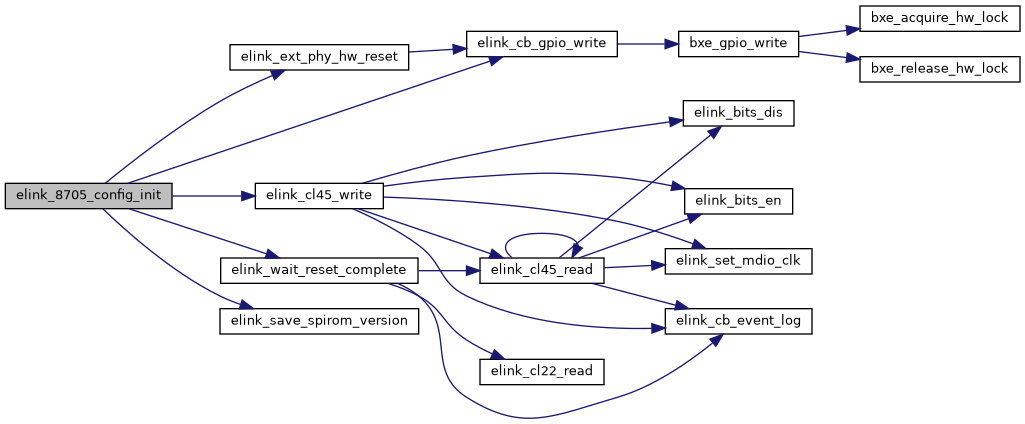

| static elink_status_t | elink_8705_config_init (struct elink_phy *phy, struct elink_params *params, struct elink_vars *vars) |

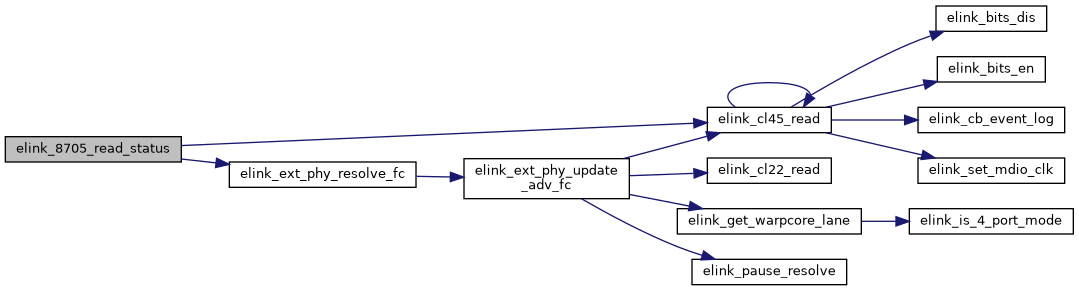

| static uint8_t | elink_8705_read_status (struct elink_phy *phy, struct elink_params *params, struct elink_vars *vars) |

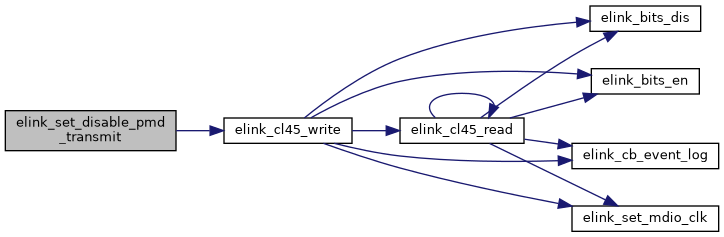

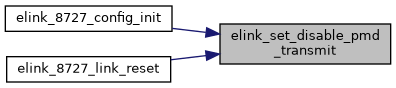

| static void | elink_set_disable_pmd_transmit (struct elink_params *params, struct elink_phy *phy, uint8_t pmd_dis) |

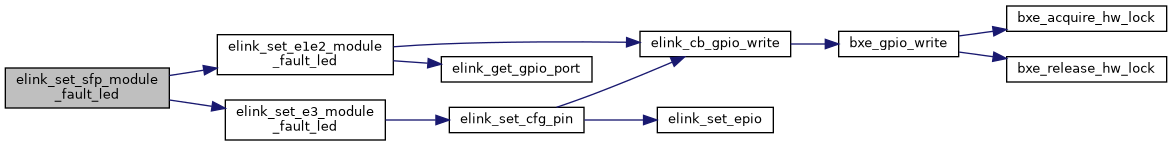

| static uint8_t | elink_get_gpio_port (struct elink_params *params) |

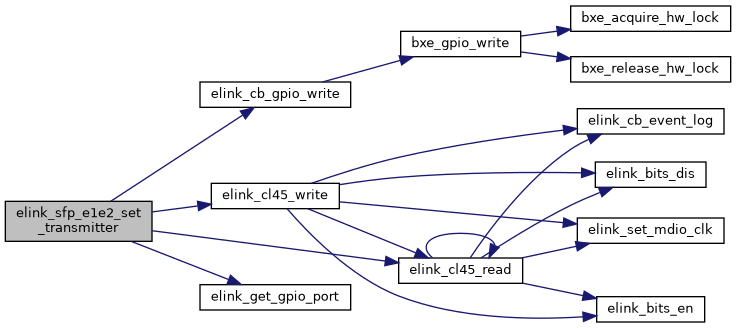

| static void | elink_sfp_e1e2_set_transmitter (struct elink_params *params, struct elink_phy *phy, uint8_t tx_en) |

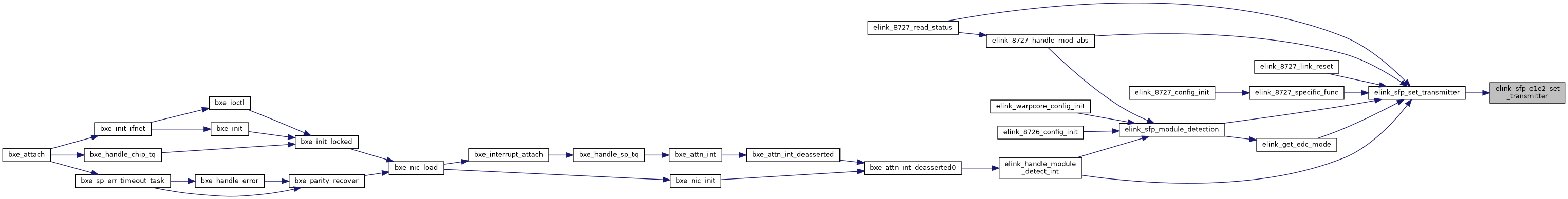

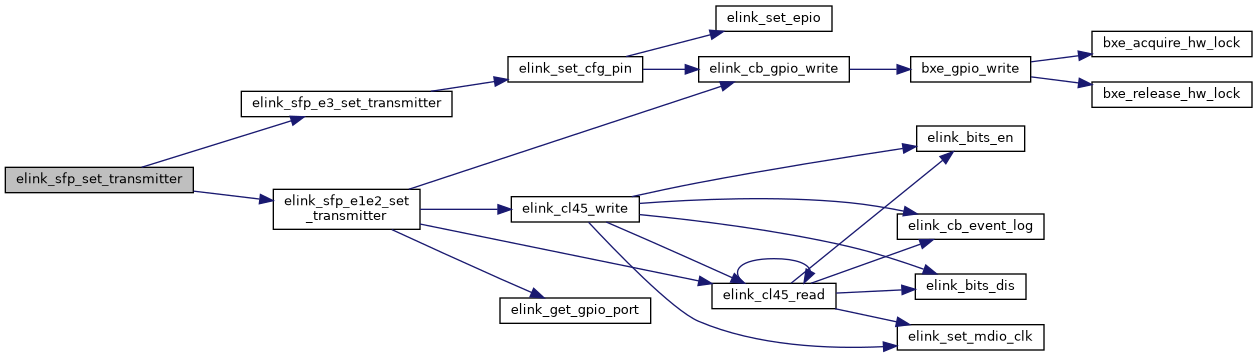

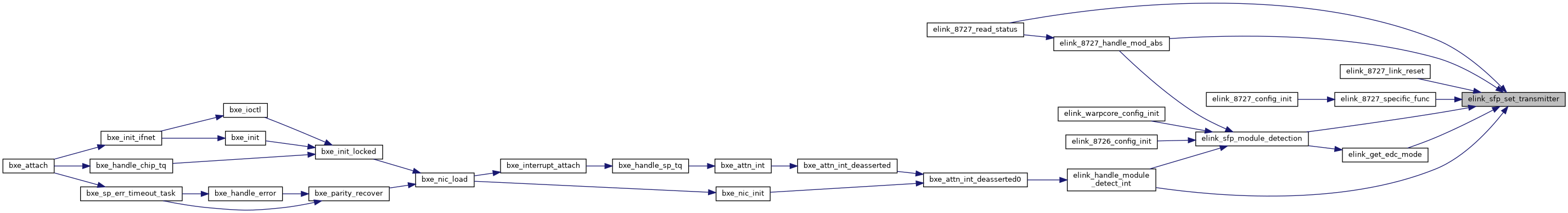

| static void | elink_sfp_set_transmitter (struct elink_params *params, struct elink_phy *phy, uint8_t tx_en) |

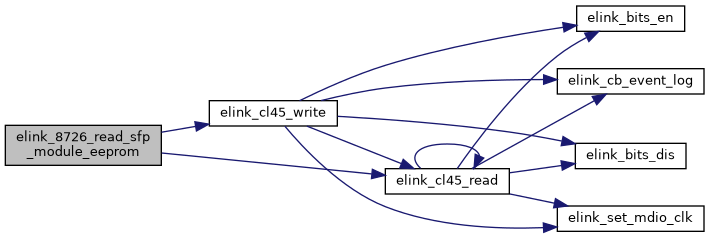

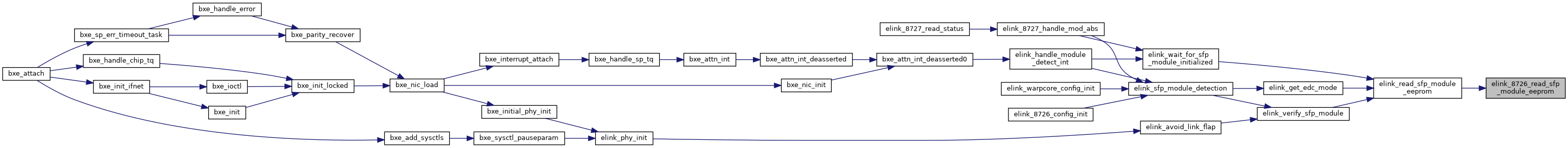

| static elink_status_t | elink_8726_read_sfp_module_eeprom (struct elink_phy *phy, struct elink_params *params, uint8_t dev_addr, uint16_t addr, uint8_t byte_cnt, uint8_t *o_buf, uint8_t is_init) |

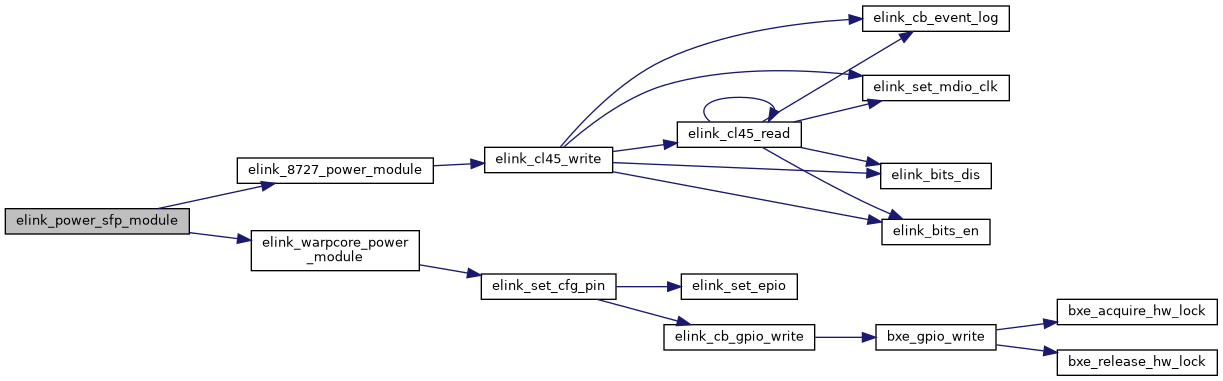

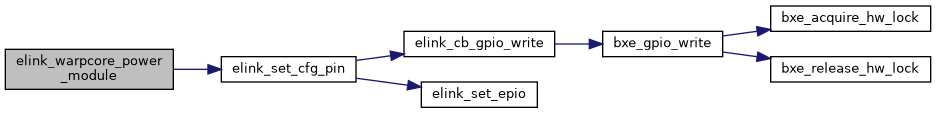

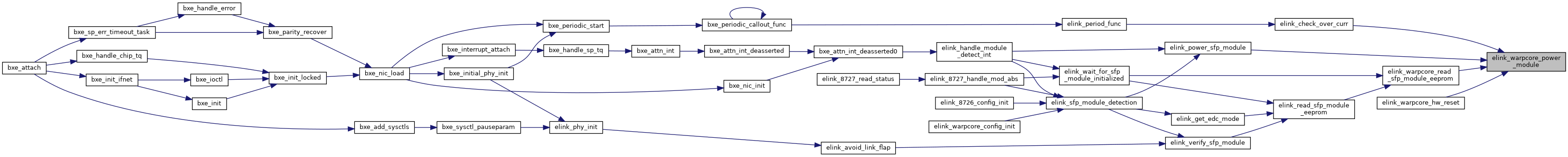

| static void | elink_warpcore_power_module (struct elink_params *params, uint8_t power) |

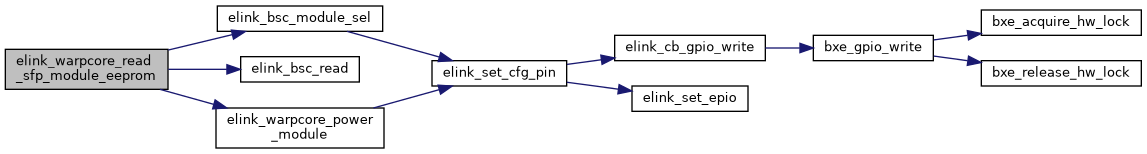

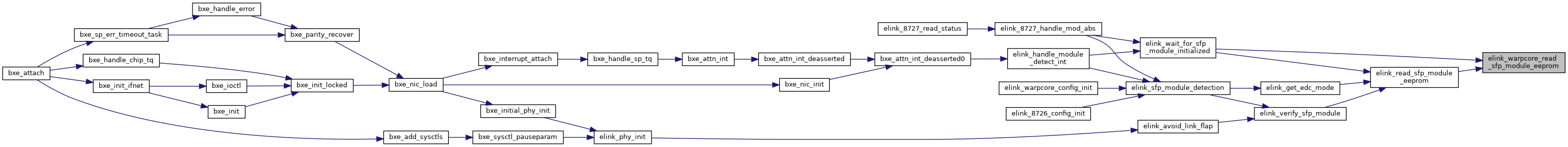

| static elink_status_t | elink_warpcore_read_sfp_module_eeprom (struct elink_phy *phy, struct elink_params *params, uint8_t dev_addr, uint16_t addr, uint8_t byte_cnt, uint8_t *o_buf, uint8_t is_init) |

| static elink_status_t | elink_8727_read_sfp_module_eeprom (struct elink_phy *phy, struct elink_params *params, uint8_t dev_addr, uint16_t addr, uint8_t byte_cnt, uint8_t *o_buf, uint8_t is_init) |

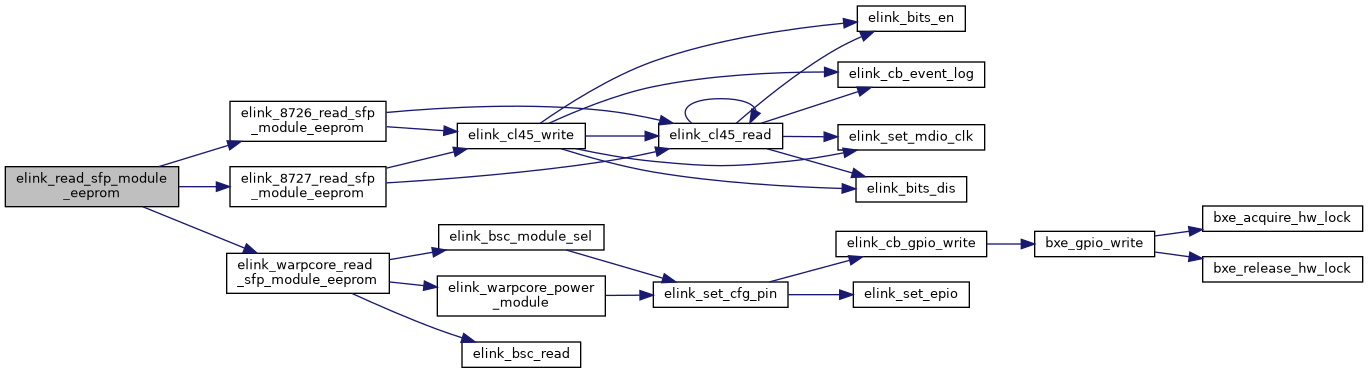

| elink_status_t | elink_read_sfp_module_eeprom (struct elink_phy *phy, struct elink_params *params, uint8_t dev_addr, uint16_t addr, uint16_t byte_cnt, uint8_t *o_buf) |

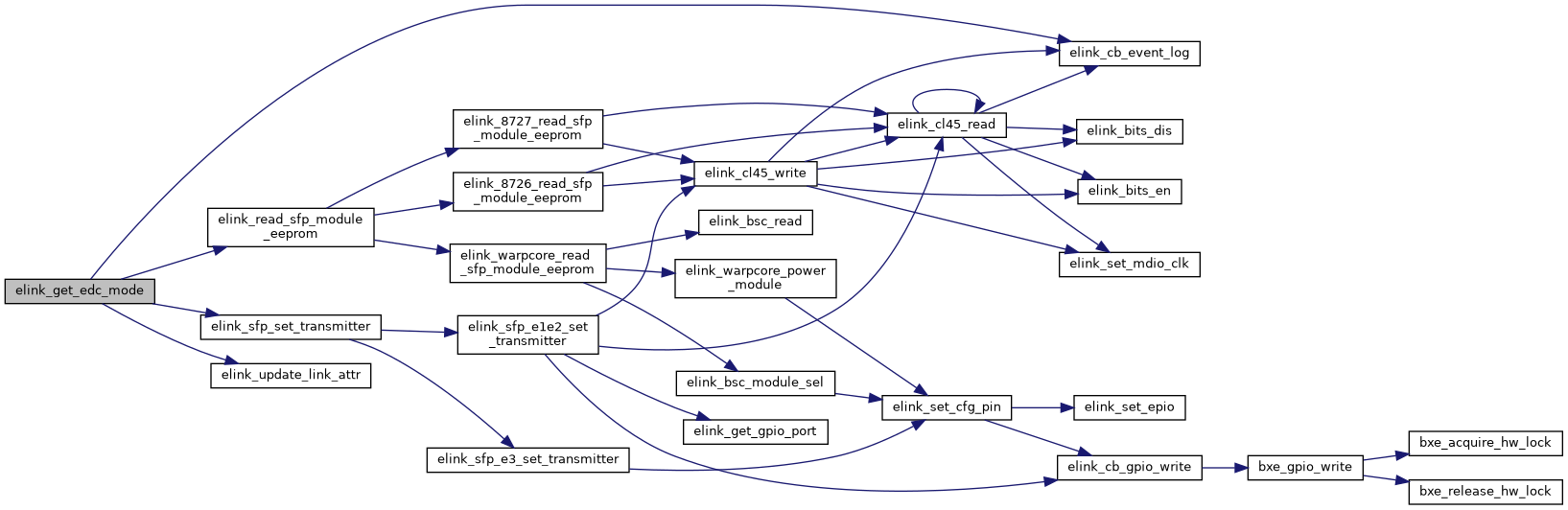

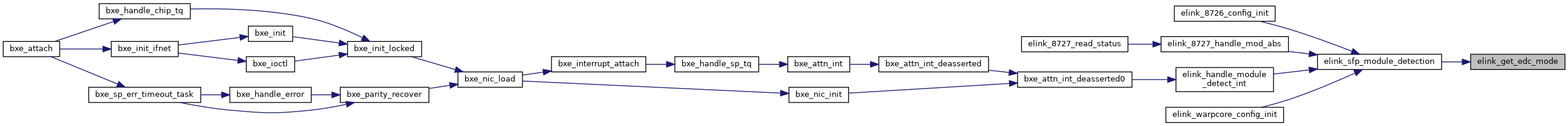

| static elink_status_t | elink_get_edc_mode (struct elink_phy *phy, struct elink_params *params, uint16_t *edc_mode) |

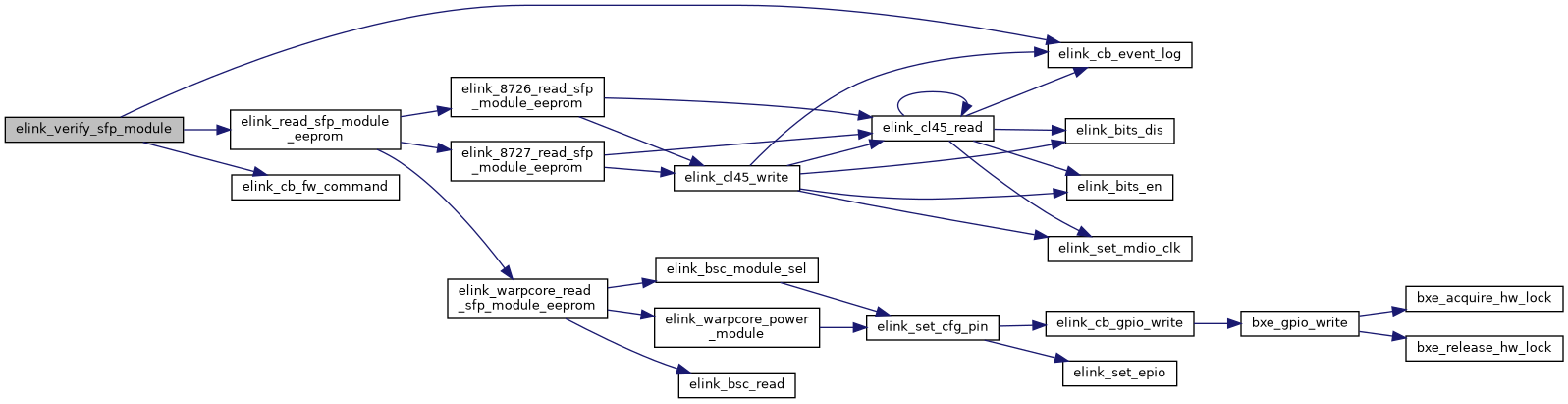

| static elink_status_t | elink_verify_sfp_module (struct elink_phy *phy, struct elink_params *params) |

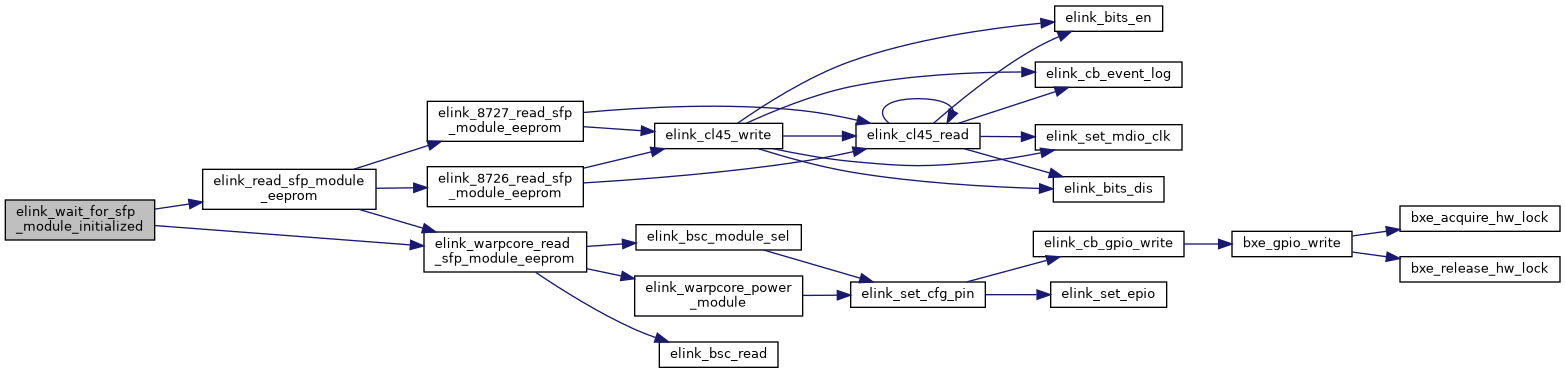

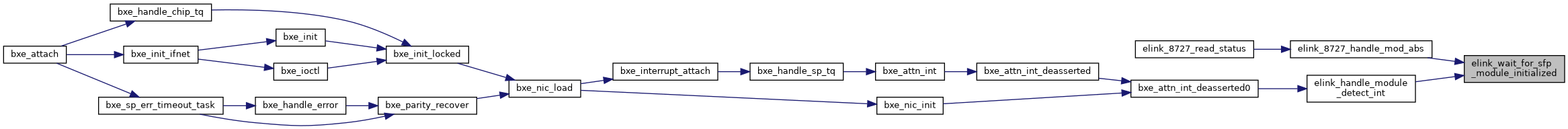

| static elink_status_t | elink_wait_for_sfp_module_initialized (struct elink_phy *phy, struct elink_params *params) |

| static void | elink_8727_power_module (struct bxe_softc *sc, struct elink_phy *phy, uint8_t is_power_up) |

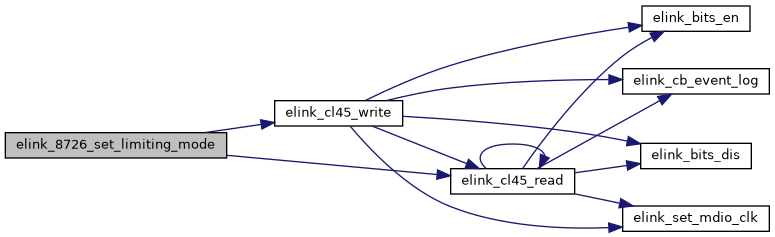

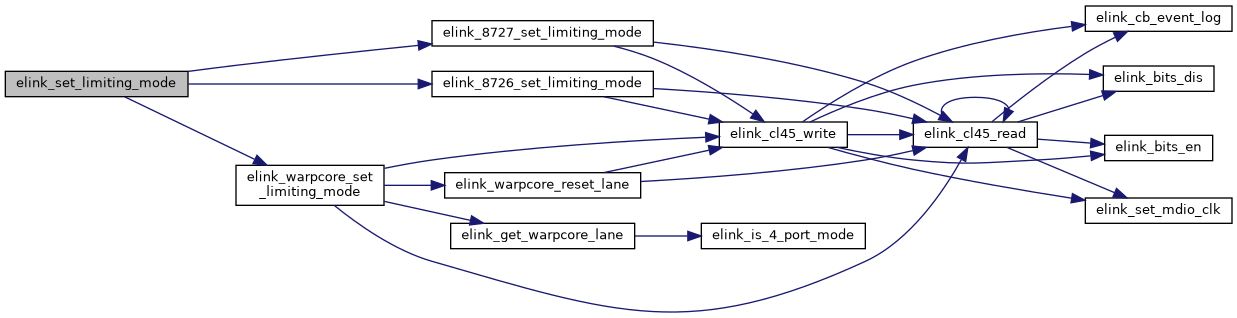

| static elink_status_t | elink_8726_set_limiting_mode (struct bxe_softc *sc, struct elink_phy *phy, uint16_t edc_mode) |

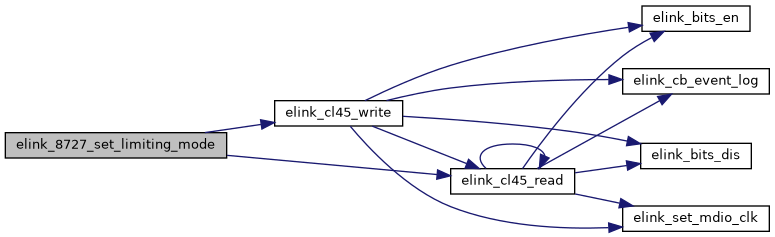

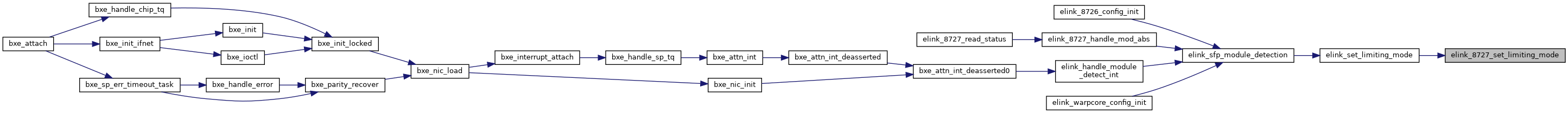

| static elink_status_t | elink_8727_set_limiting_mode (struct bxe_softc *sc, struct elink_phy *phy, uint16_t edc_mode) |

| static void | elink_8727_specific_func (struct elink_phy *phy, struct elink_params *params, uint32_t action) |

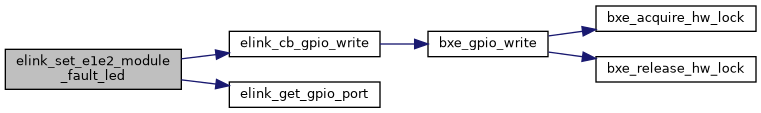

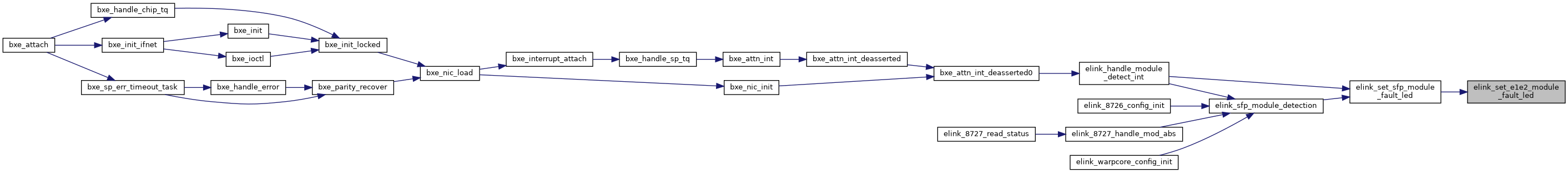

| static void | elink_set_e1e2_module_fault_led (struct elink_params *params, uint8_t gpio_mode) |

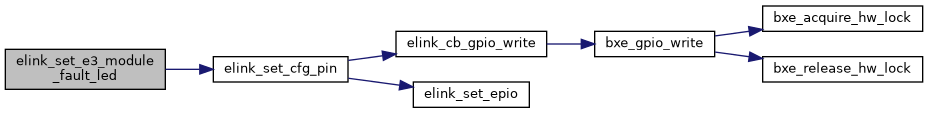

| static void | elink_set_e3_module_fault_led (struct elink_params *params, uint8_t gpio_mode) |

| static void | elink_set_sfp_module_fault_led (struct elink_params *params, uint8_t gpio_mode) |

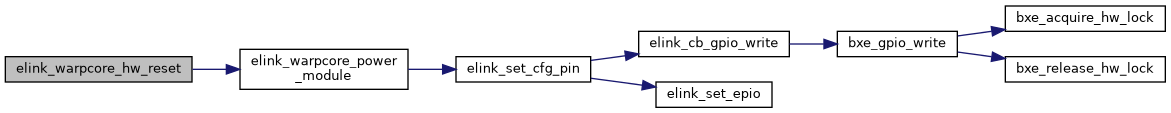

| static void | elink_warpcore_hw_reset (struct elink_phy *phy, struct elink_params *params) |

| static void | elink_power_sfp_module (struct elink_params *params, struct elink_phy *phy, uint8_t power) |

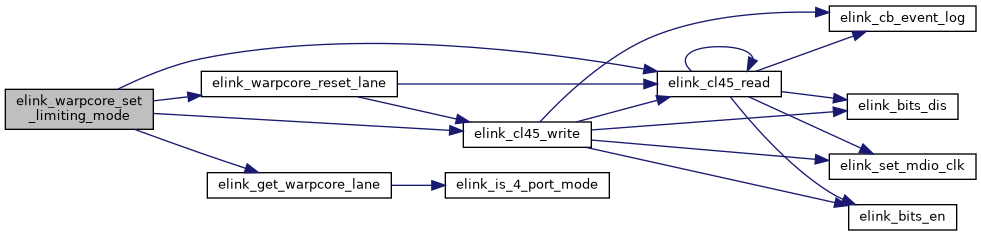

| static void | elink_warpcore_set_limiting_mode (struct elink_params *params, struct elink_phy *phy, uint16_t edc_mode) |

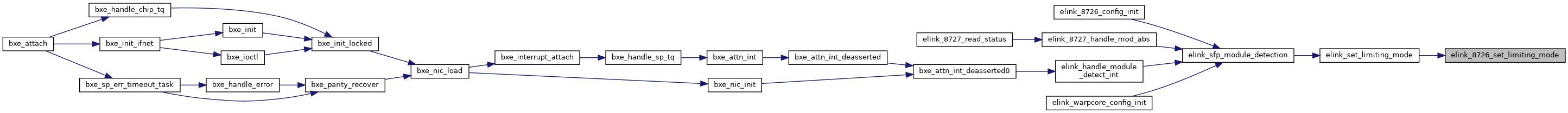

| static void | elink_set_limiting_mode (struct elink_params *params, struct elink_phy *phy, uint16_t edc_mode) |

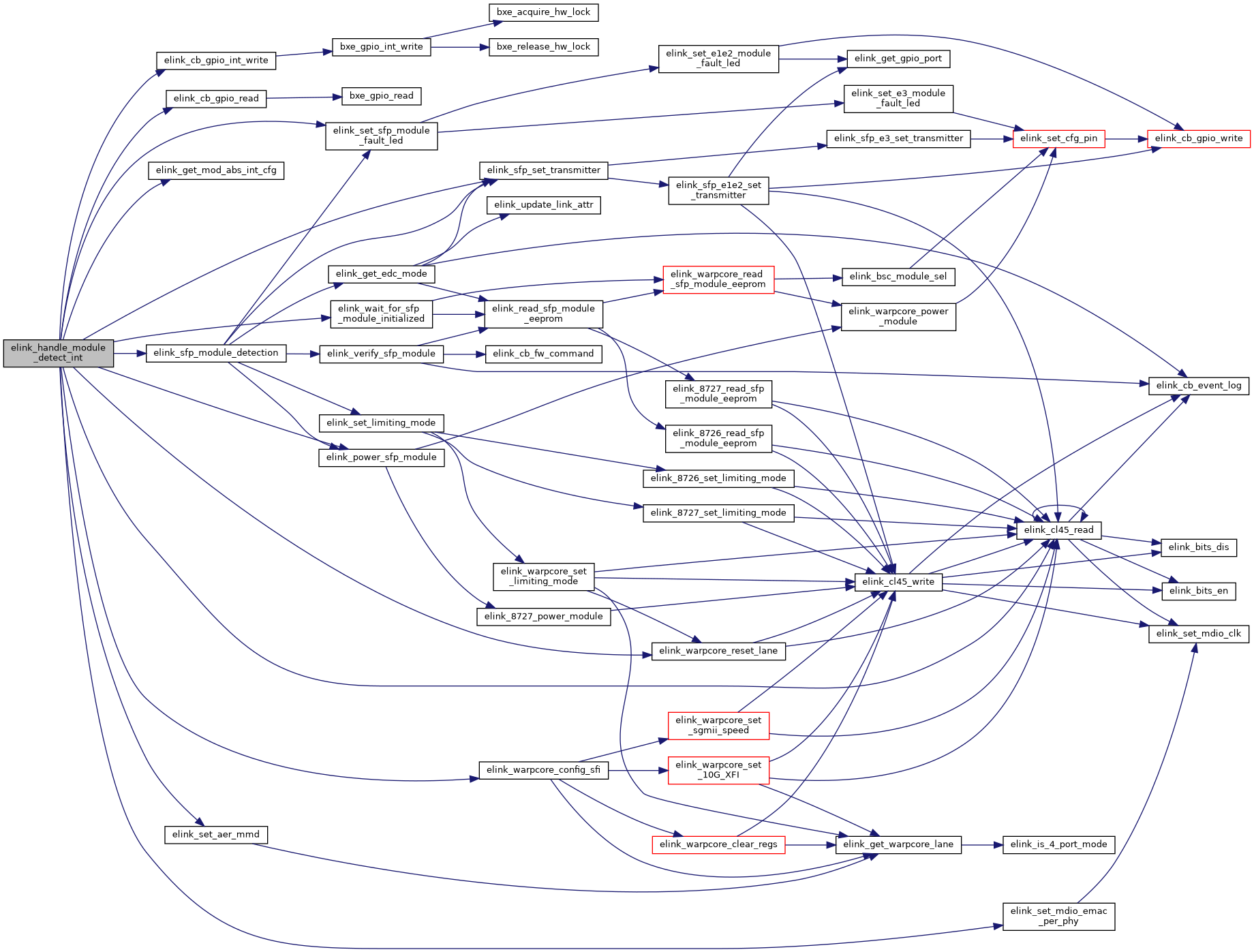

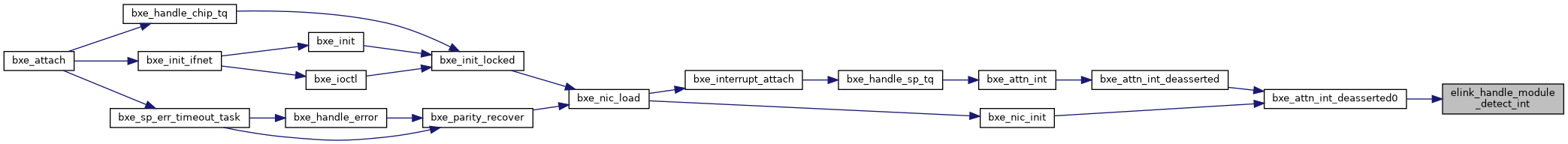

| void | elink_handle_module_detect_int (struct elink_params *params) |

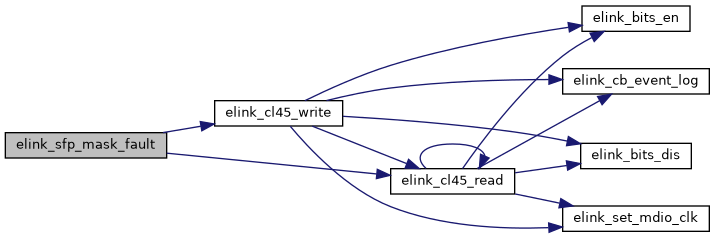

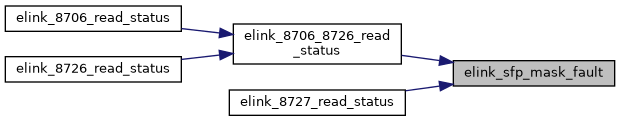

| static void | elink_sfp_mask_fault (struct bxe_softc *sc, struct elink_phy *phy, uint16_t alarm_status_offset, uint16_t alarm_ctrl_offset) |

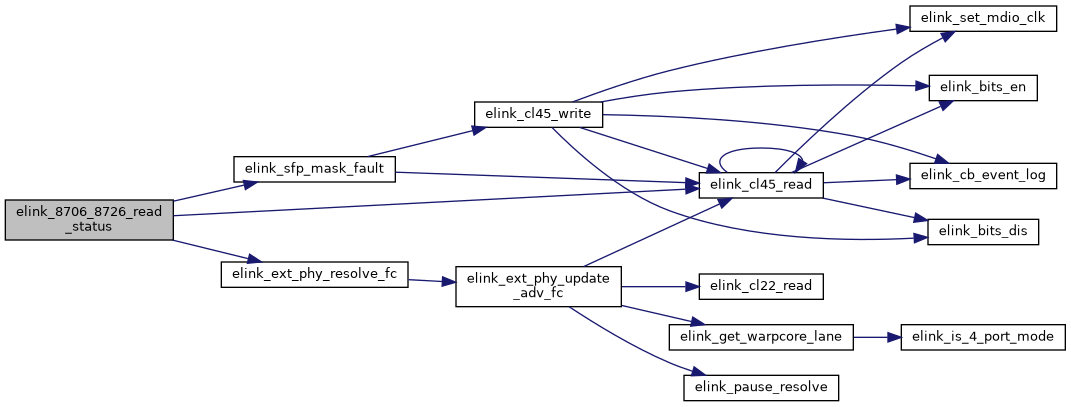

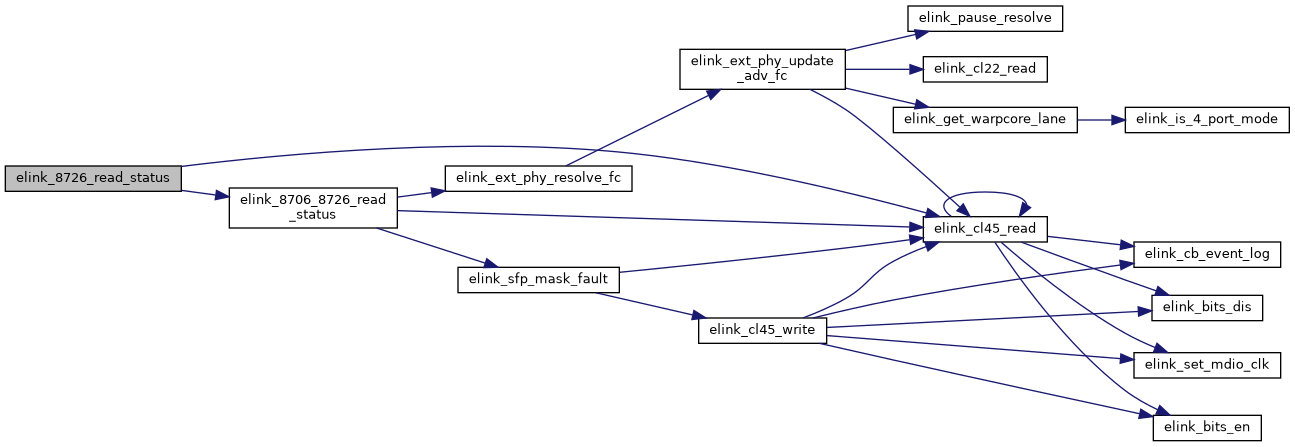

| static uint8_t | elink_8706_8726_read_status (struct elink_phy *phy, struct elink_params *params, struct elink_vars *vars) |

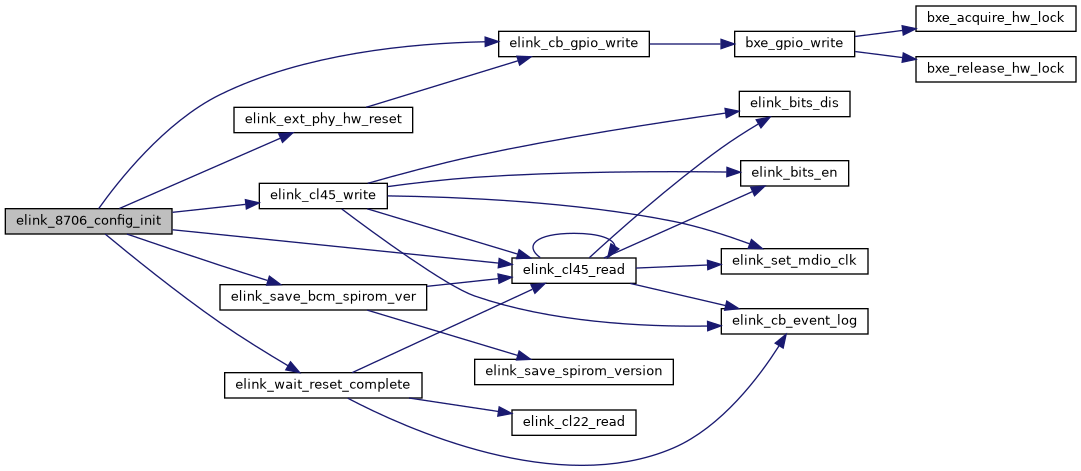

| static uint8_t | elink_8706_config_init (struct elink_phy *phy, struct elink_params *params, struct elink_vars *vars) |

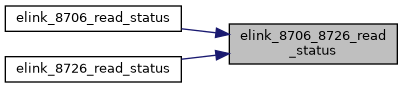

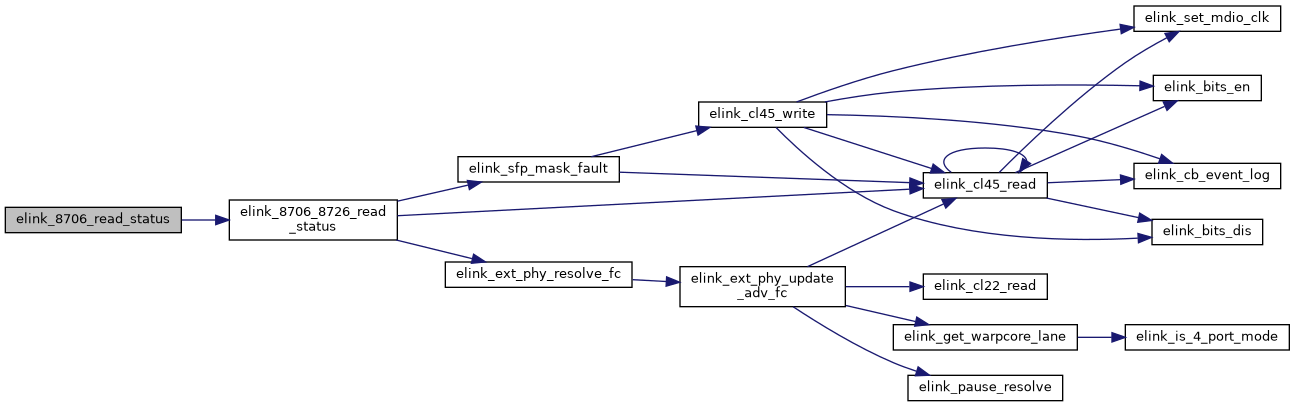

| static elink_status_t | elink_8706_read_status (struct elink_phy *phy, struct elink_params *params, struct elink_vars *vars) |

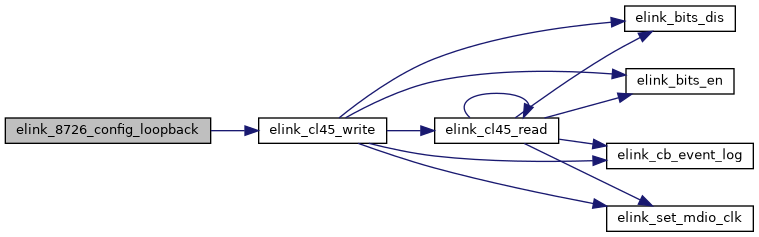

| static void | elink_8726_config_loopback (struct elink_phy *phy, struct elink_params *params) |

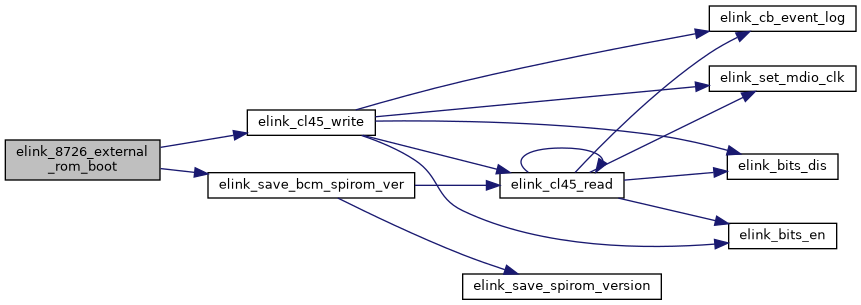

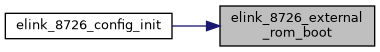

| static void | elink_8726_external_rom_boot (struct elink_phy *phy, struct elink_params *params) |

| static uint8_t | elink_8726_read_status (struct elink_phy *phy, struct elink_params *params, struct elink_vars *vars) |

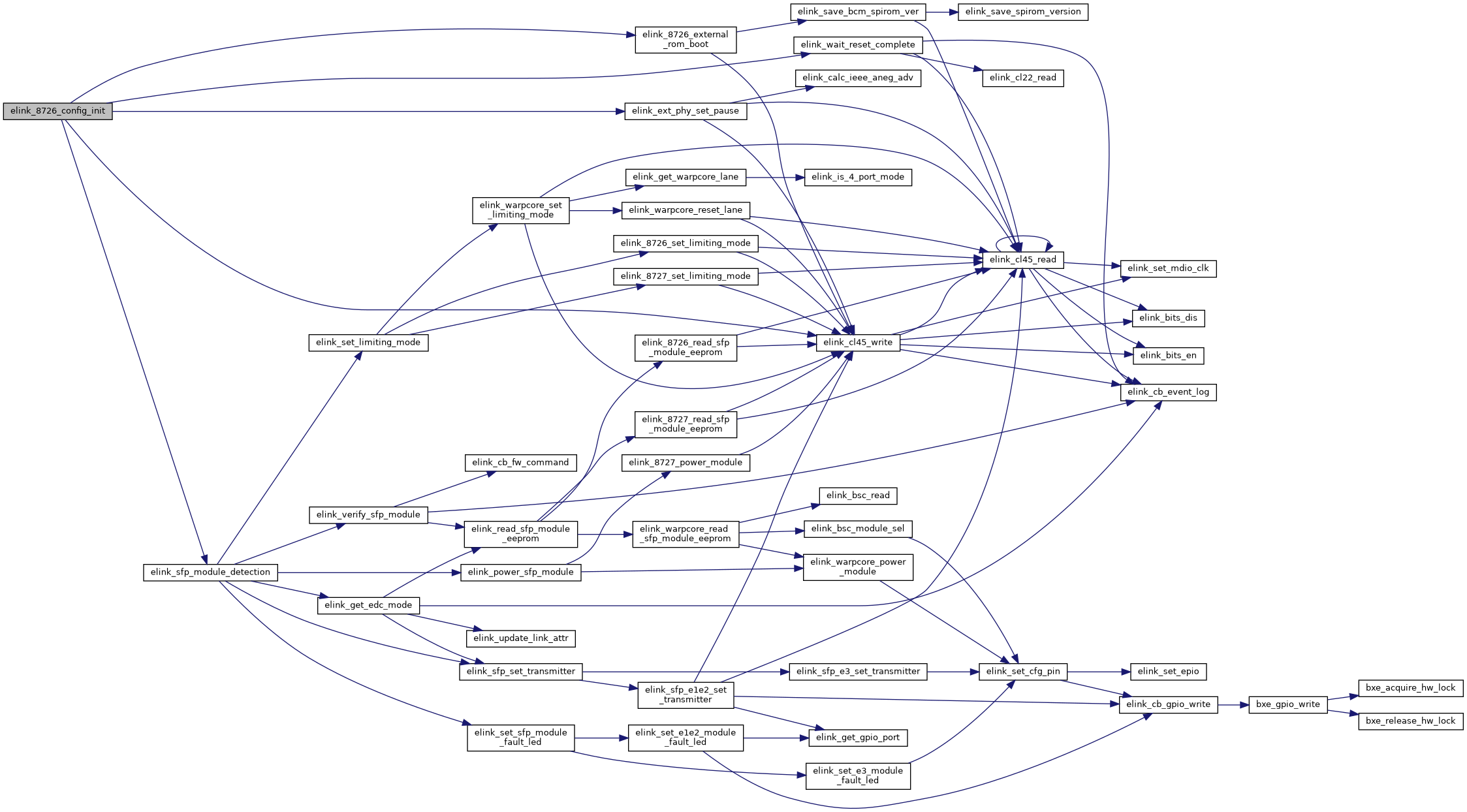

| static elink_status_t | elink_8726_config_init (struct elink_phy *phy, struct elink_params *params, struct elink_vars *vars) |

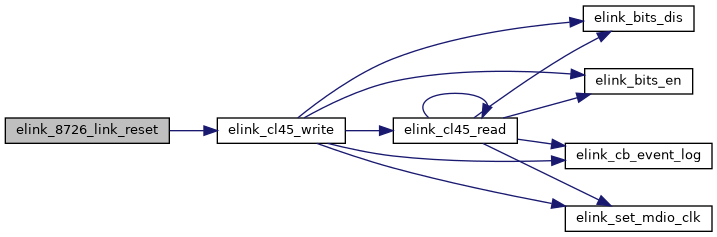

| static void | elink_8726_link_reset (struct elink_phy *phy, struct elink_params *params) |

| static void | elink_8727_set_link_led (struct elink_phy *phy, struct elink_params *params, uint8_t mode) |

| static void | elink_8727_hw_reset (struct elink_phy *phy, struct elink_params *params) |

| static void | elink_8727_config_speed (struct elink_phy *phy, struct elink_params *params) |

| static elink_status_t | elink_8727_config_init (struct elink_phy *phy, struct elink_params *params, struct elink_vars *vars) |

| static void | elink_8727_handle_mod_abs (struct elink_phy *phy, struct elink_params *params) |

| static uint8_t | elink_8727_read_status (struct elink_phy *phy, struct elink_params *params, struct elink_vars *vars) |

| static void | elink_8727_link_reset (struct elink_phy *phy, struct elink_params *params) |

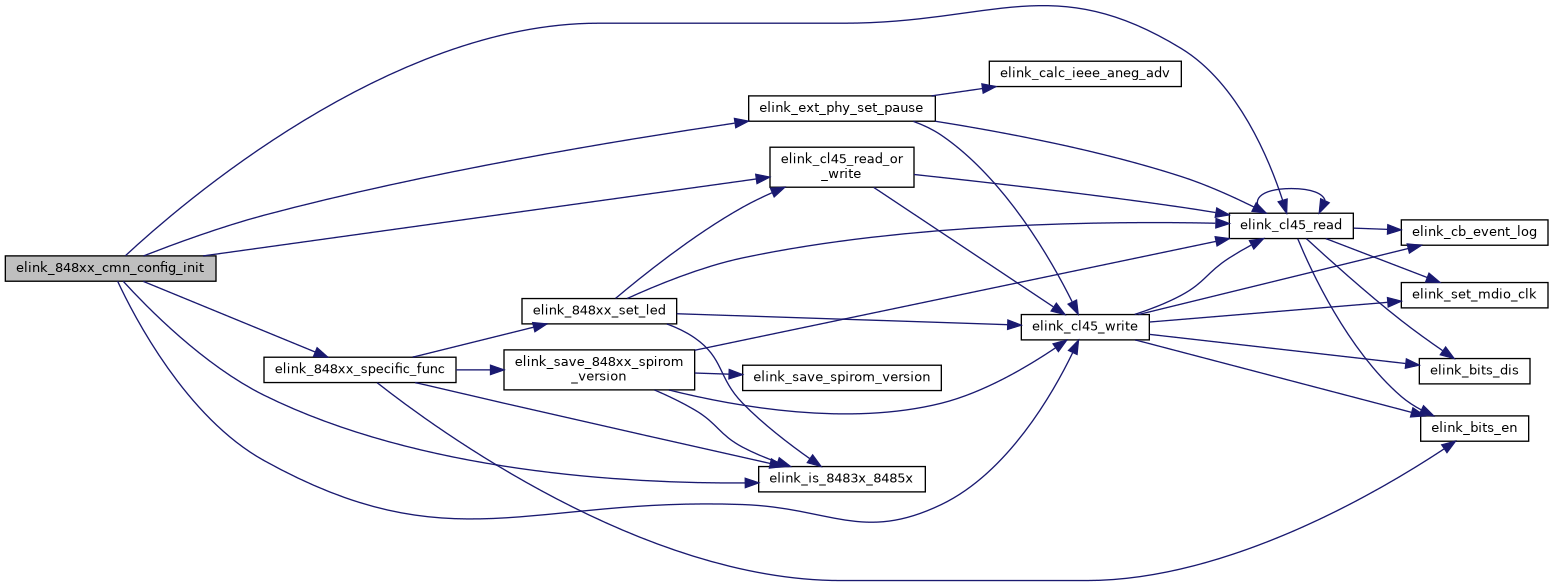

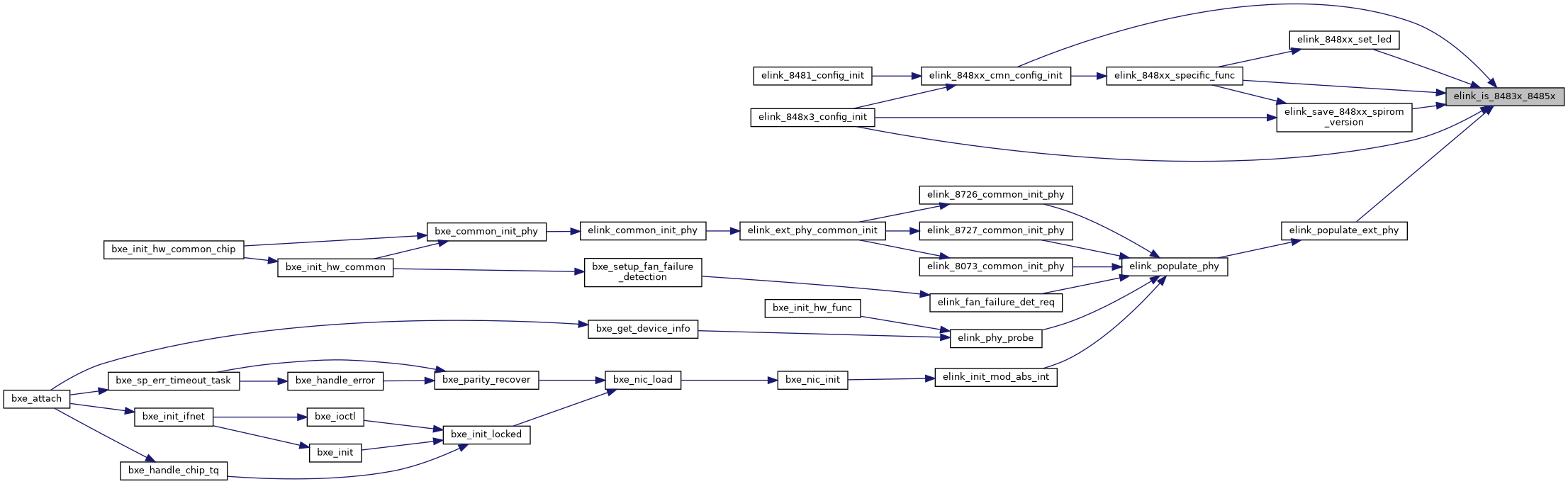

| static int | elink_is_8483x_8485x (struct elink_phy *phy) |

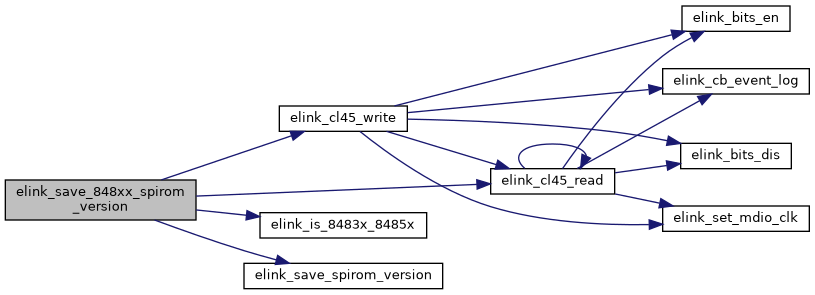

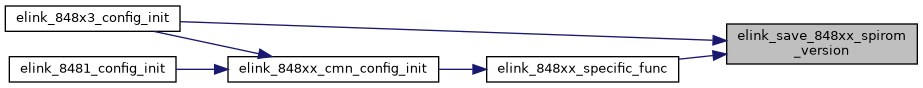

| static void | elink_save_848xx_spirom_version (struct elink_phy *phy, struct bxe_softc *sc, uint8_t port) |

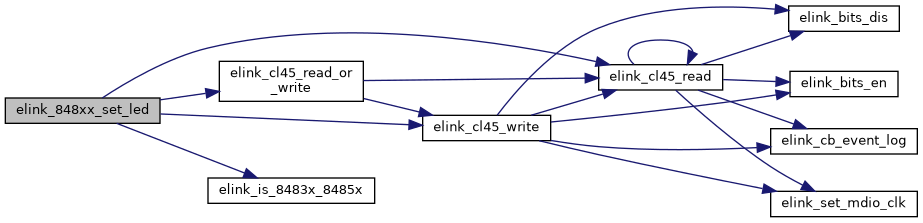

| static void | elink_848xx_set_led (struct bxe_softc *sc, struct elink_phy *phy) |

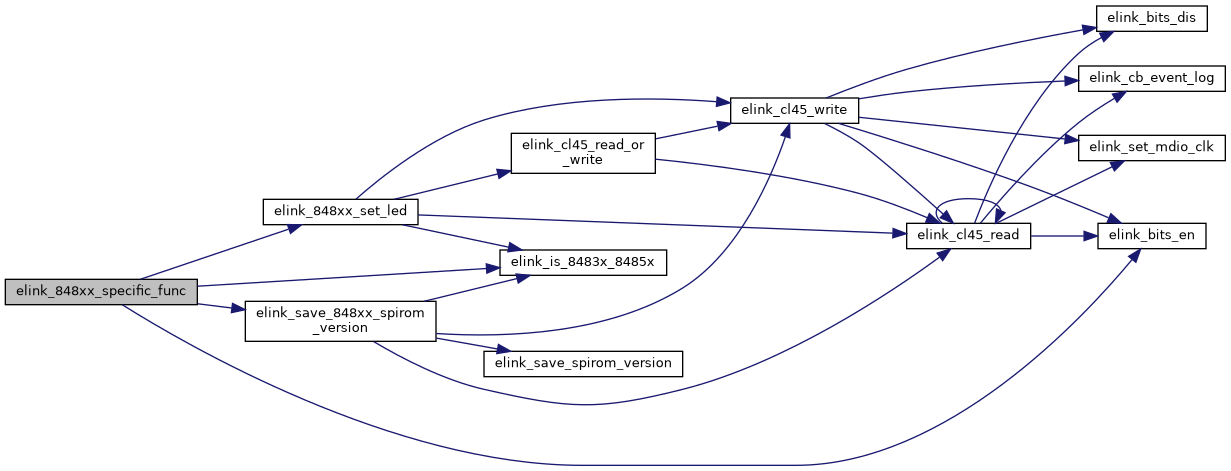

| static void | elink_848xx_specific_func (struct elink_phy *phy, struct elink_params *params, uint32_t action) |

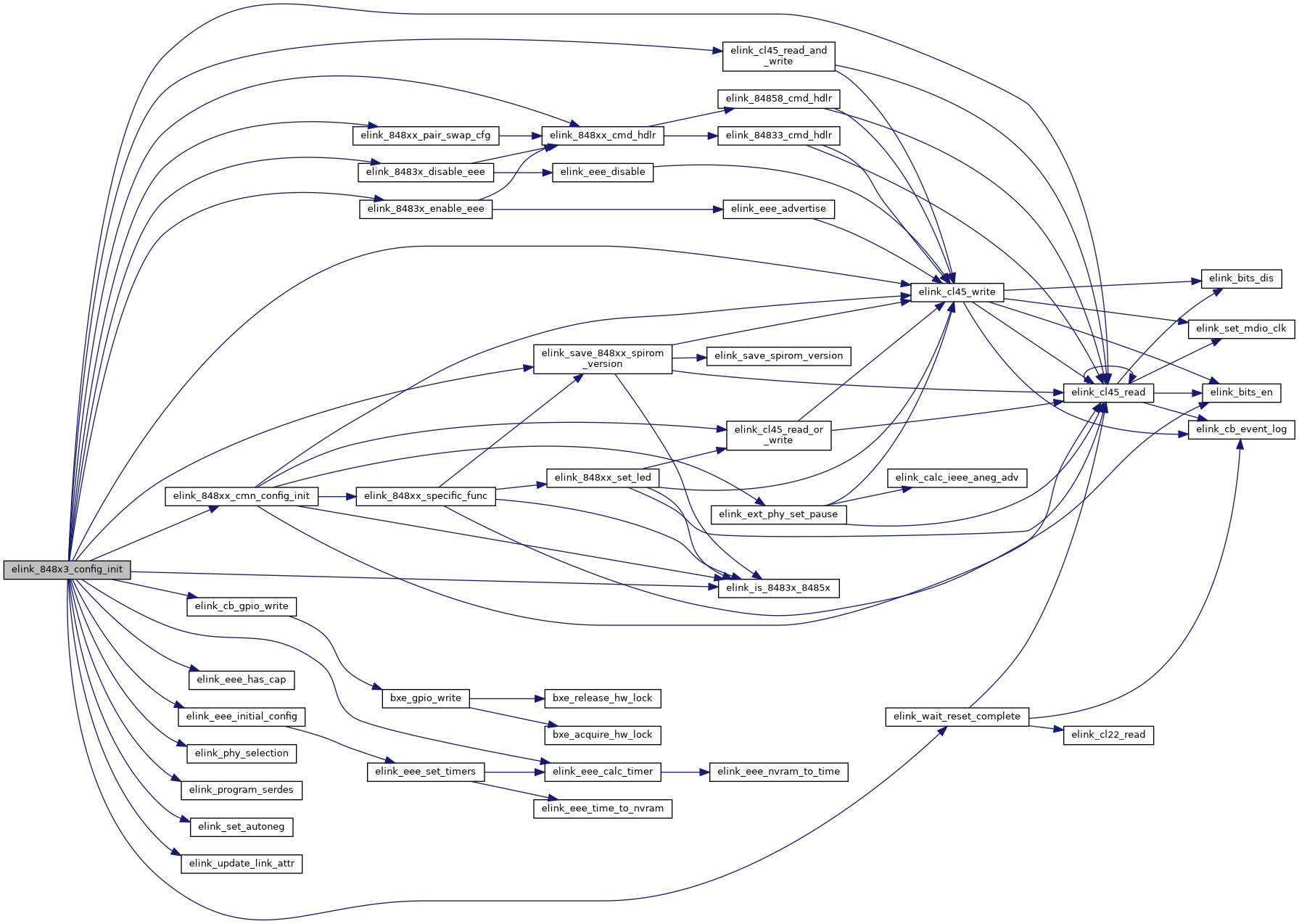

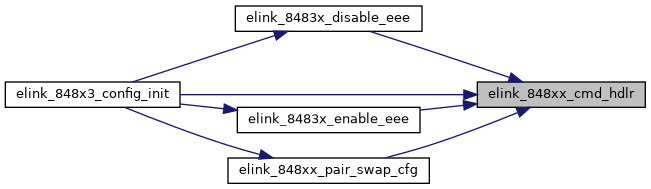

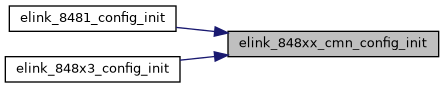

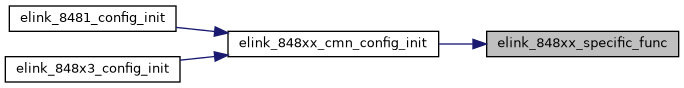

| static elink_status_t | elink_848xx_cmn_config_init (struct elink_phy *phy, struct elink_params *params, struct elink_vars *vars) |

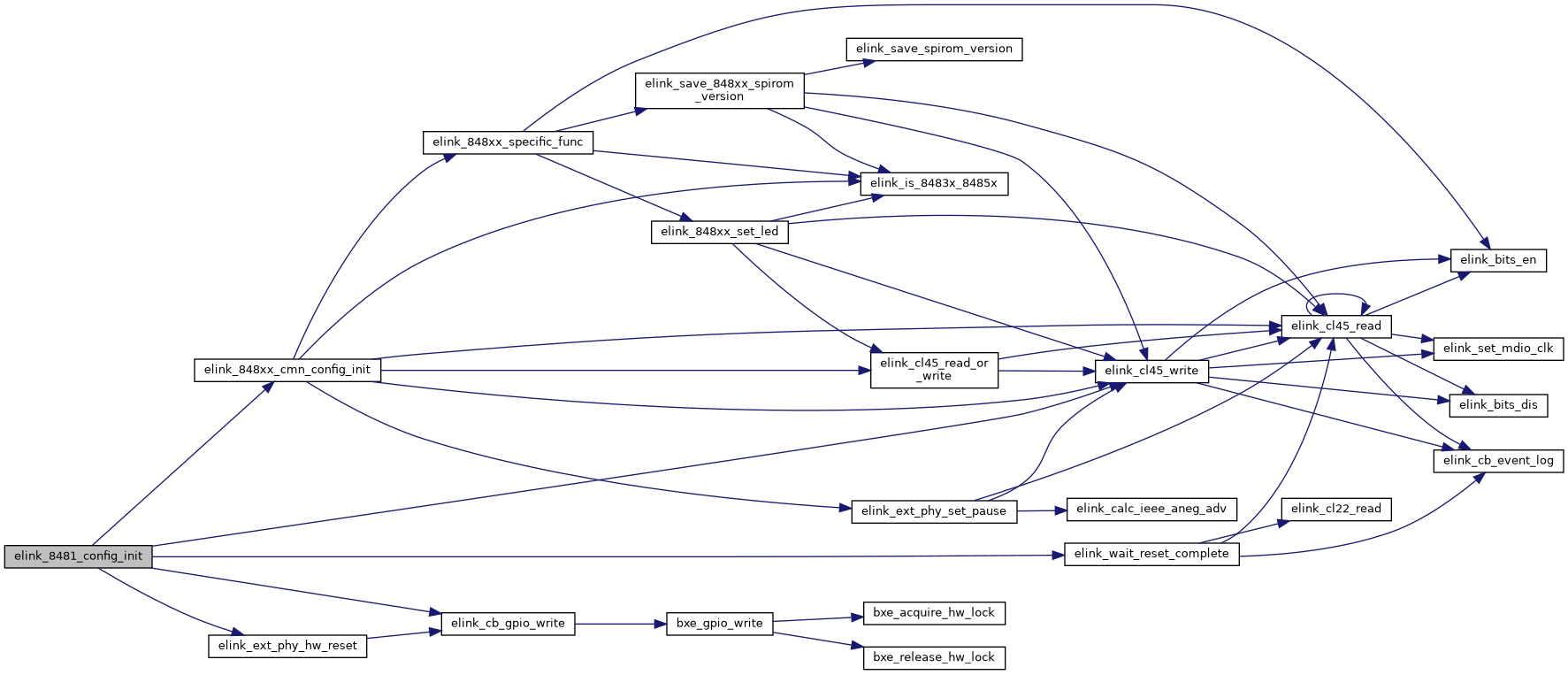

| static elink_status_t | elink_8481_config_init (struct elink_phy *phy, struct elink_params *params, struct elink_vars *vars) |

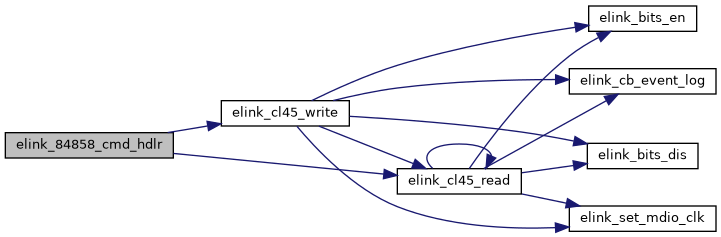

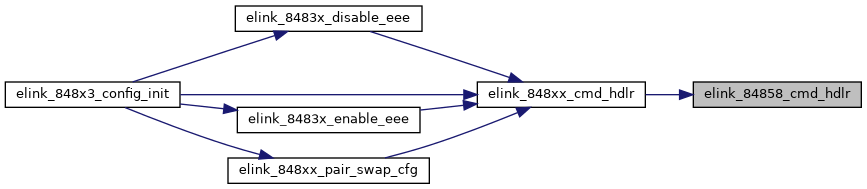

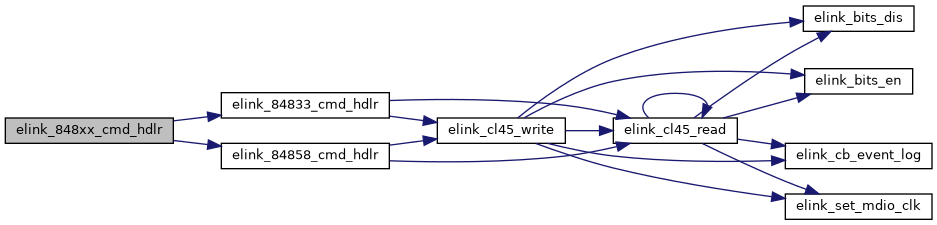

| static elink_status_t | elink_84858_cmd_hdlr (struct elink_phy *phy, struct elink_params *params, uint16_t fw_cmd, uint16_t cmd_args[], int argc) |

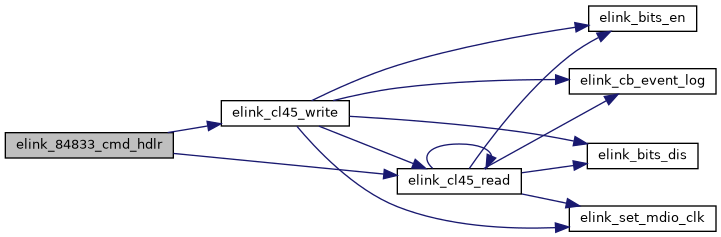

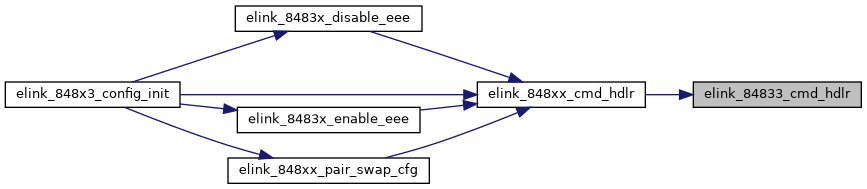

| static elink_status_t | elink_84833_cmd_hdlr (struct elink_phy *phy, struct elink_params *params, uint16_t fw_cmd, uint16_t cmd_args[], int argc, int process) |

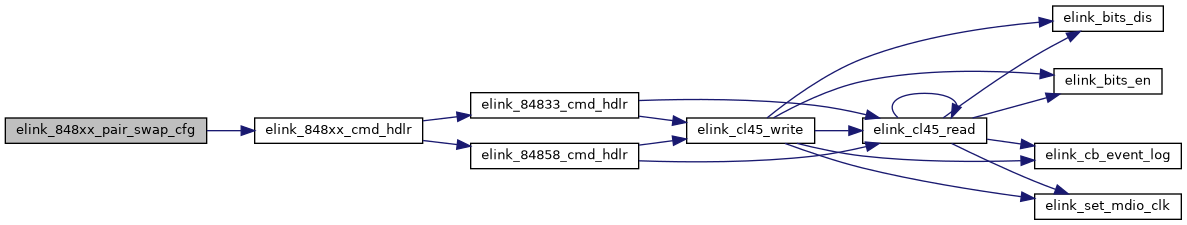

| static elink_status_t | elink_848xx_cmd_hdlr (struct elink_phy *phy, struct elink_params *params, uint16_t fw_cmd, uint16_t cmd_args[], int argc, int process) |

| static elink_status_t | elink_848xx_pair_swap_cfg (struct elink_phy *phy, struct elink_params *params, struct elink_vars *vars) |

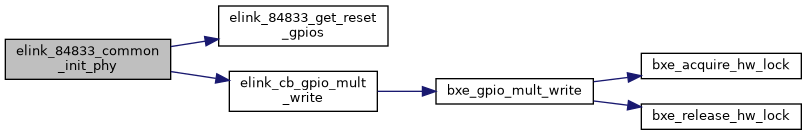

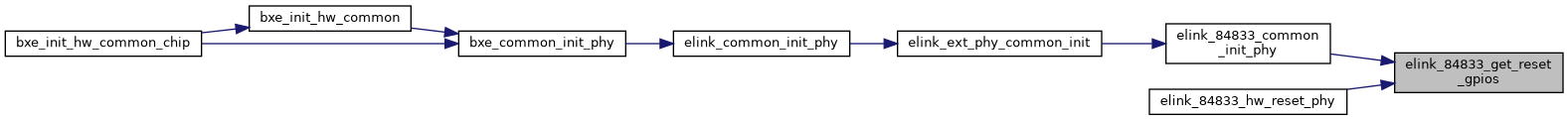

| static uint8_t | elink_84833_get_reset_gpios (struct bxe_softc *sc, uint32_t shmem_base_path[], uint32_t chip_id) |

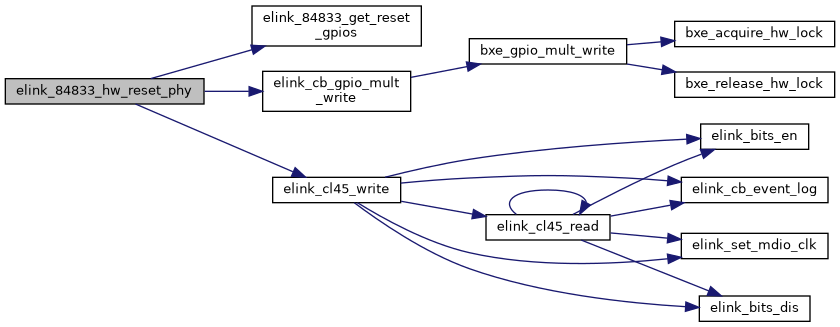

| static elink_status_t | elink_84833_hw_reset_phy (struct elink_phy *phy, struct elink_params *params) |

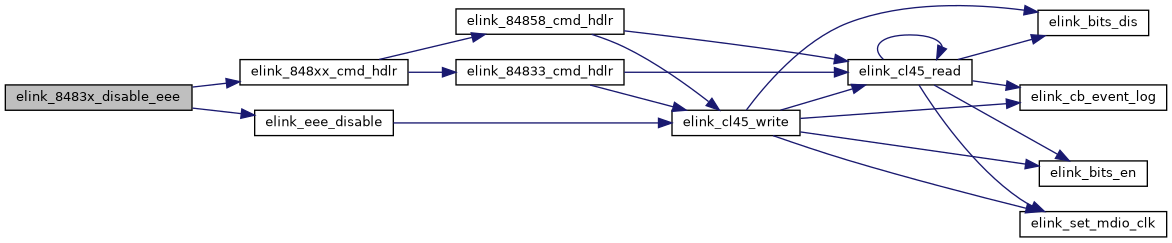

| static elink_status_t | elink_8483x_disable_eee (struct elink_phy *phy, struct elink_params *params, struct elink_vars *vars) |

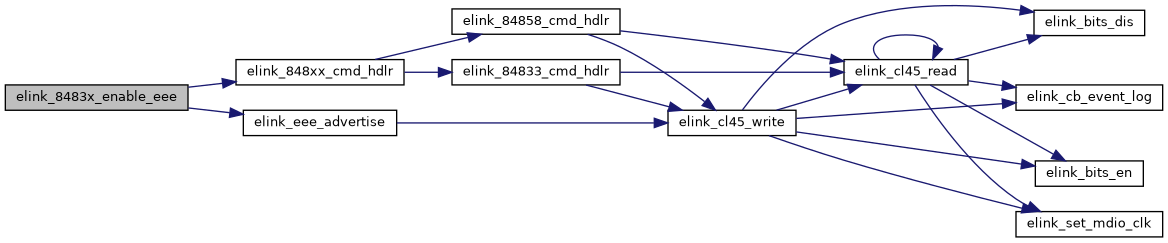

| static elink_status_t | elink_8483x_enable_eee (struct elink_phy *phy, struct elink_params *params, struct elink_vars *vars) |

| static elink_status_t | elink_848x3_config_init (struct elink_phy *phy, struct elink_params *params, struct elink_vars *vars) |

| static uint8_t | elink_848xx_read_status (struct elink_phy *phy, struct elink_params *params, struct elink_vars *vars) |

| static elink_status_t | elink_848xx_format_ver (uint32_t raw_ver, uint8_t *str, uint16_t *len) |

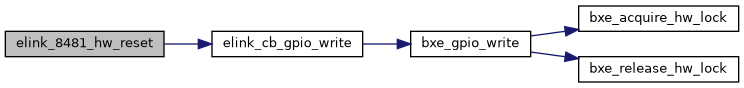

| static void | elink_8481_hw_reset (struct elink_phy *phy, struct elink_params *params) |

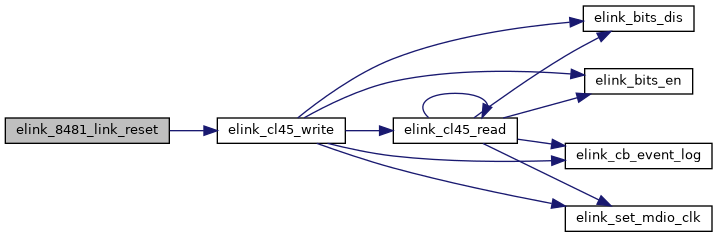

| static void | elink_8481_link_reset (struct elink_phy *phy, struct elink_params *params) |

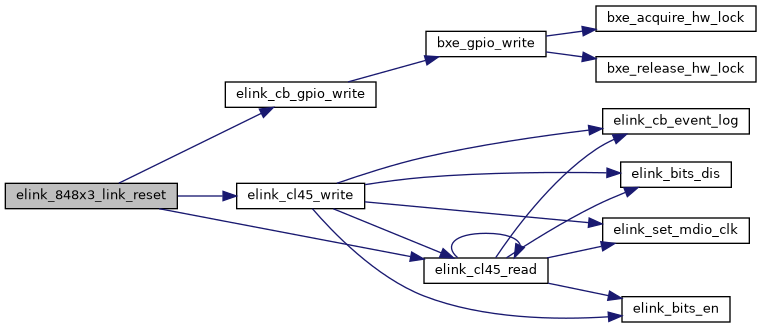

| static void | elink_848x3_link_reset (struct elink_phy *phy, struct elink_params *params) |

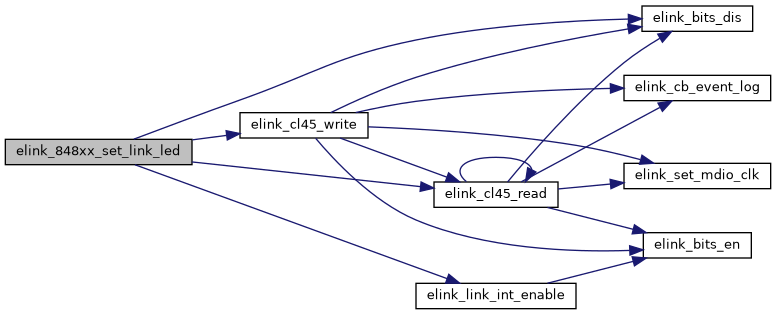

| static void | elink_848xx_set_link_led (struct elink_phy *phy, struct elink_params *params, uint8_t mode) |

| static void | elink_54618se_specific_func (struct elink_phy *phy, struct elink_params *params, uint32_t action) |

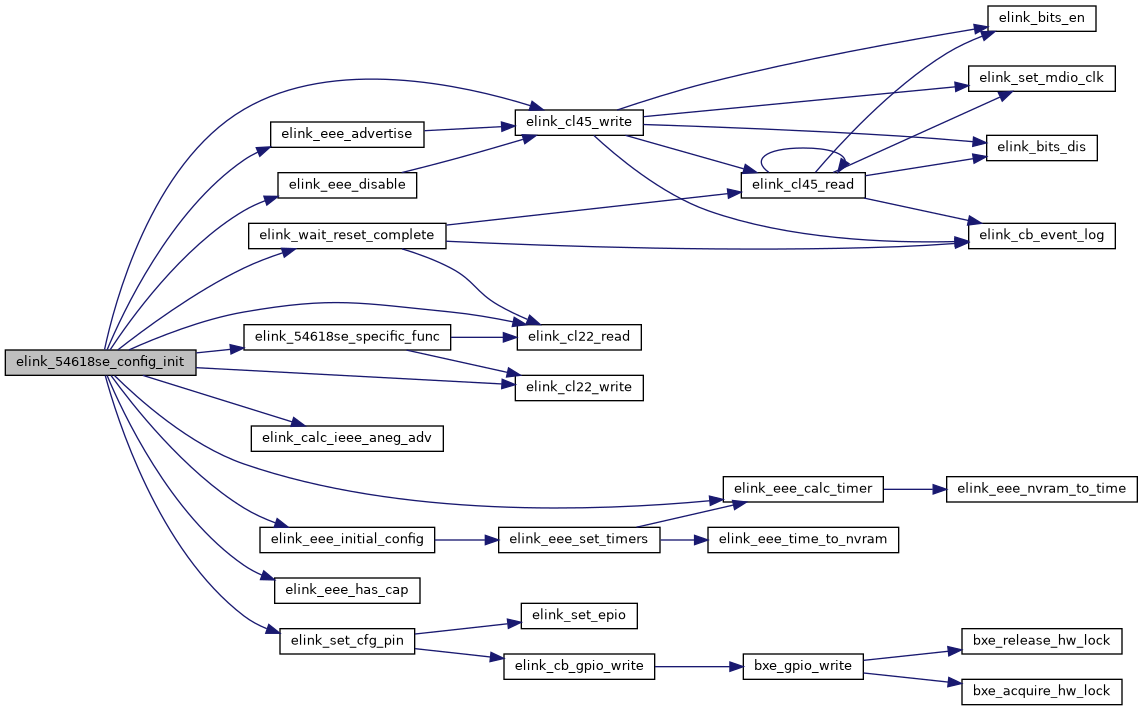

| static elink_status_t | elink_54618se_config_init (struct elink_phy *phy, struct elink_params *params, struct elink_vars *vars) |

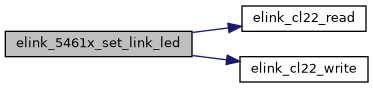

| static void | elink_5461x_set_link_led (struct elink_phy *phy, struct elink_params *params, uint8_t mode) |

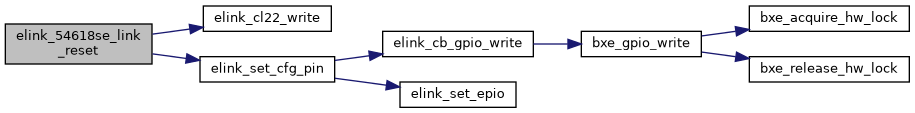

| static void | elink_54618se_link_reset (struct elink_phy *phy, struct elink_params *params) |

| static uint8_t | elink_54618se_read_status (struct elink_phy *phy, struct elink_params *params, struct elink_vars *vars) |

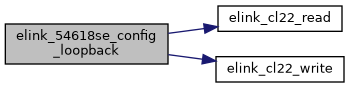

| static void | elink_54618se_config_loopback (struct elink_phy *phy, struct elink_params *params) |

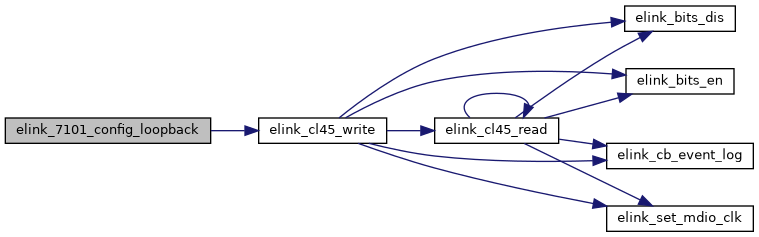

| static void | elink_7101_config_loopback (struct elink_phy *phy, struct elink_params *params) |

| static elink_status_t | elink_7101_config_init (struct elink_phy *phy, struct elink_params *params, struct elink_vars *vars) |

| static uint8_t | elink_7101_read_status (struct elink_phy *phy, struct elink_params *params, struct elink_vars *vars) |

| static elink_status_t | elink_7101_format_ver (uint32_t spirom_ver, uint8_t *str, uint16_t *len) |

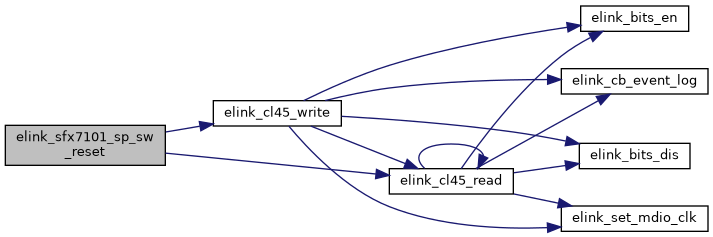

| void | elink_sfx7101_sp_sw_reset (struct bxe_softc *sc, struct elink_phy *phy) |

| static void | elink_7101_hw_reset (struct elink_phy *phy, struct elink_params *params) |

| static void | elink_7101_set_link_led (struct elink_phy *phy, struct elink_params *params, uint8_t mode) |

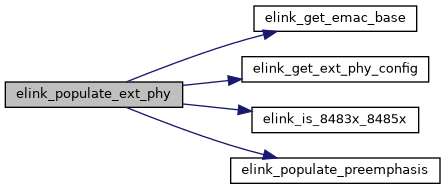

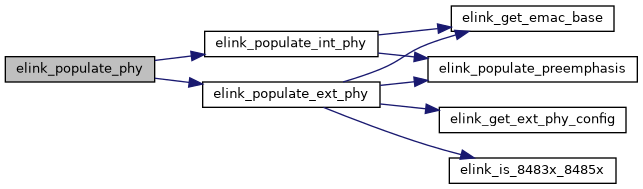

| static void | elink_populate_preemphasis (struct bxe_softc *sc, uint32_t shmem_base, struct elink_phy *phy, uint8_t port, uint8_t phy_index) |

| static uint32_t | elink_get_ext_phy_config (struct bxe_softc *sc, uint32_t shmem_base, uint8_t phy_index, uint8_t port) |

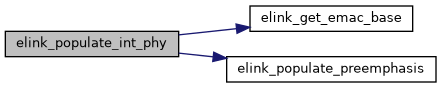

| static elink_status_t | elink_populate_int_phy (struct bxe_softc *sc, uint32_t shmem_base, uint8_t port, struct elink_phy *phy) |

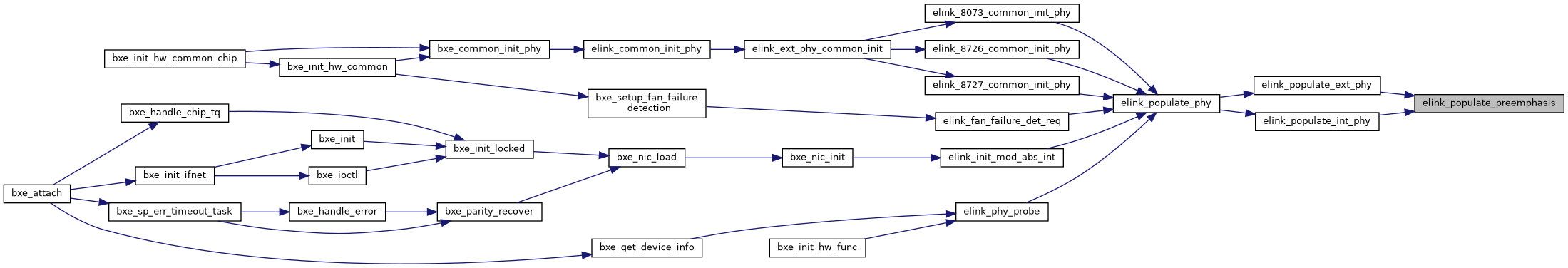

| static elink_status_t | elink_populate_ext_phy (struct bxe_softc *sc, uint8_t phy_index, uint32_t shmem_base, uint32_t shmem2_base, uint8_t port, struct elink_phy *phy) |

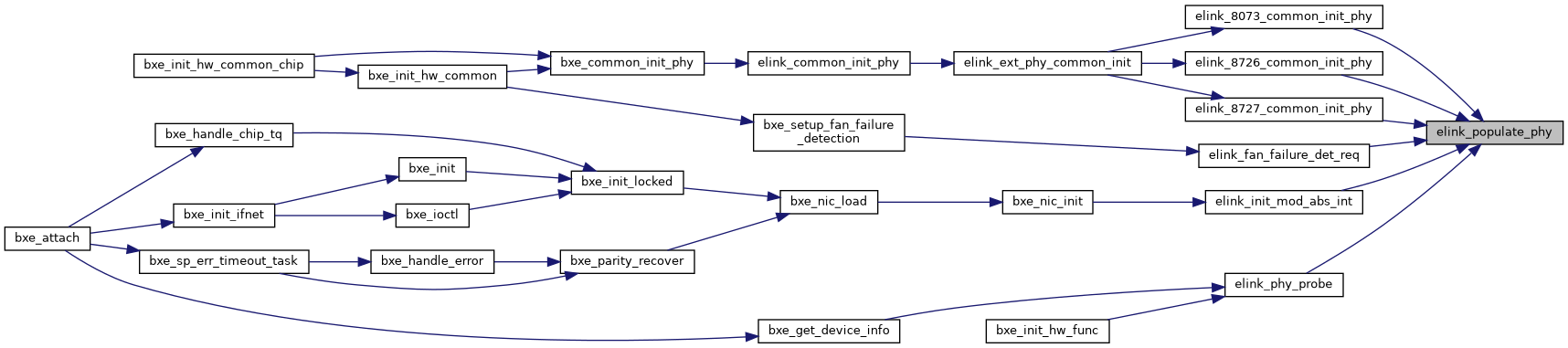

| static elink_status_t | elink_populate_phy (struct bxe_softc *sc, uint8_t phy_index, uint32_t shmem_base, uint32_t shmem2_base, uint8_t port, struct elink_phy *phy) |

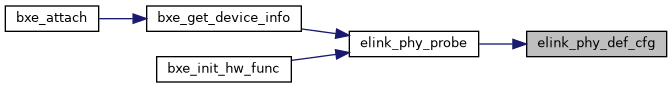

| static void | elink_phy_def_cfg (struct elink_params *params, struct elink_phy *phy, uint8_t phy_index) |

| uint32_t | elink_phy_selection (struct elink_params *params) |

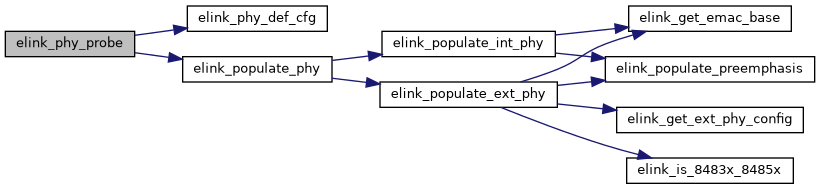

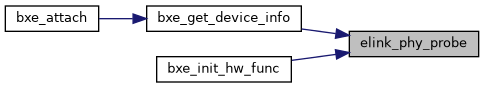

| elink_status_t | elink_phy_probe (struct elink_params *params) |

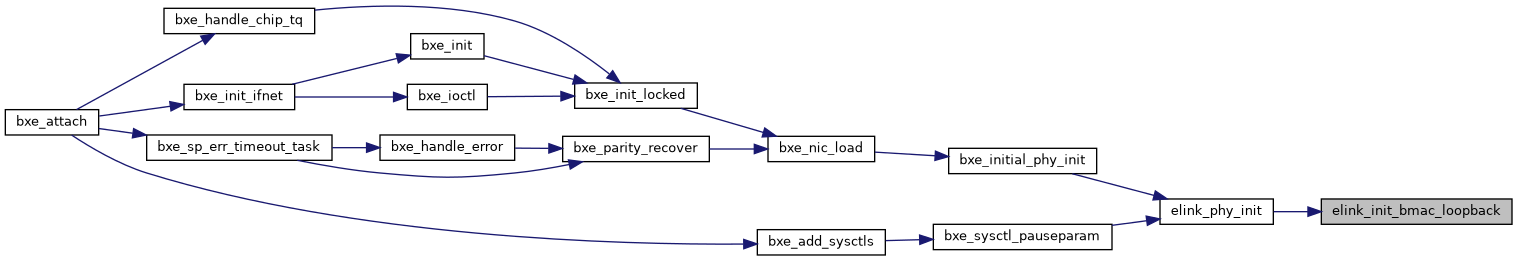

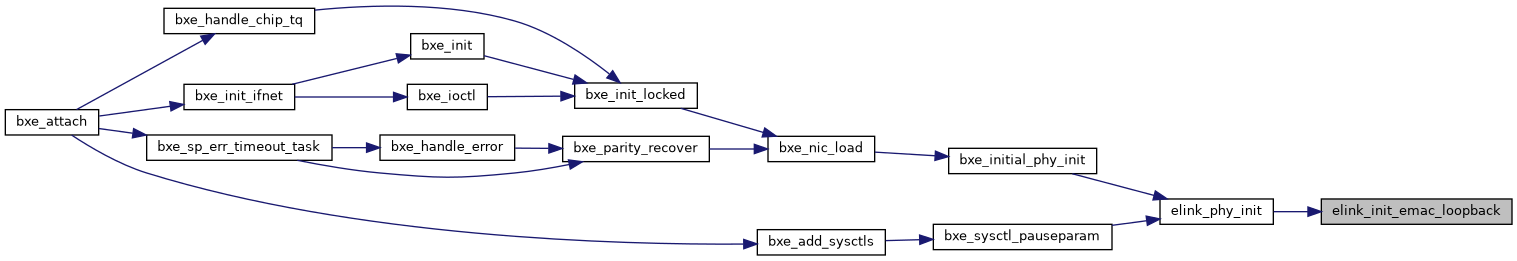

| static void | elink_init_bmac_loopback (struct elink_params *params, struct elink_vars *vars) |

| static void | elink_init_emac_loopback (struct elink_params *params, struct elink_vars *vars) |

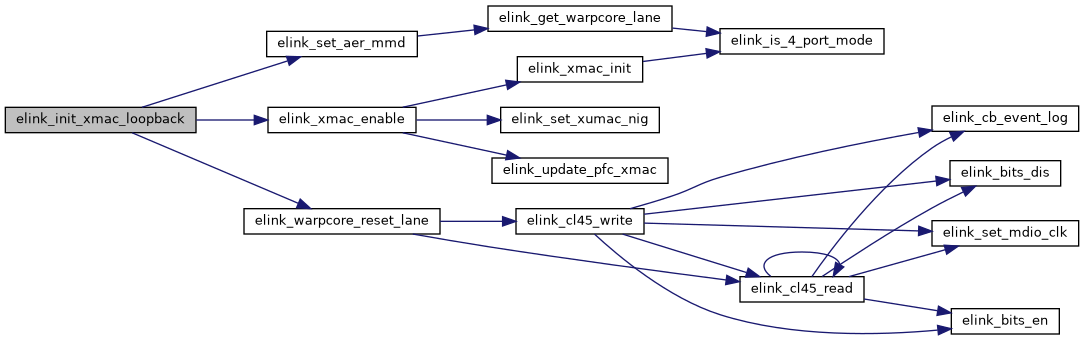

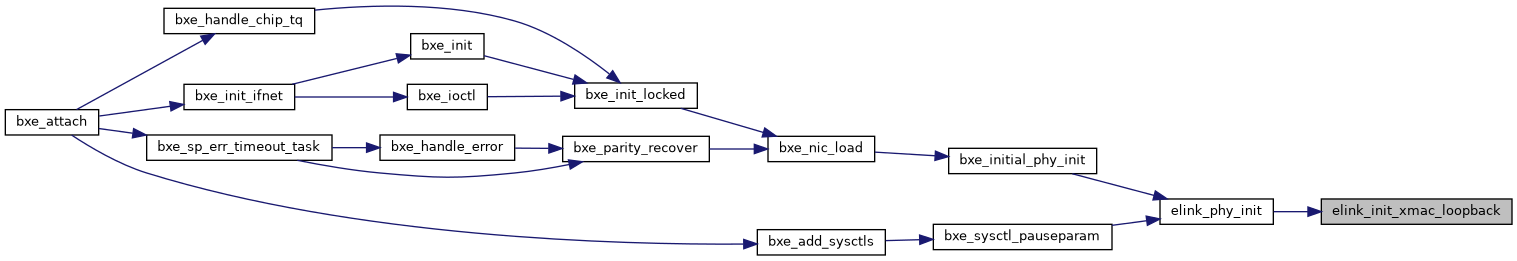

| static void | elink_init_xmac_loopback (struct elink_params *params, struct elink_vars *vars) |

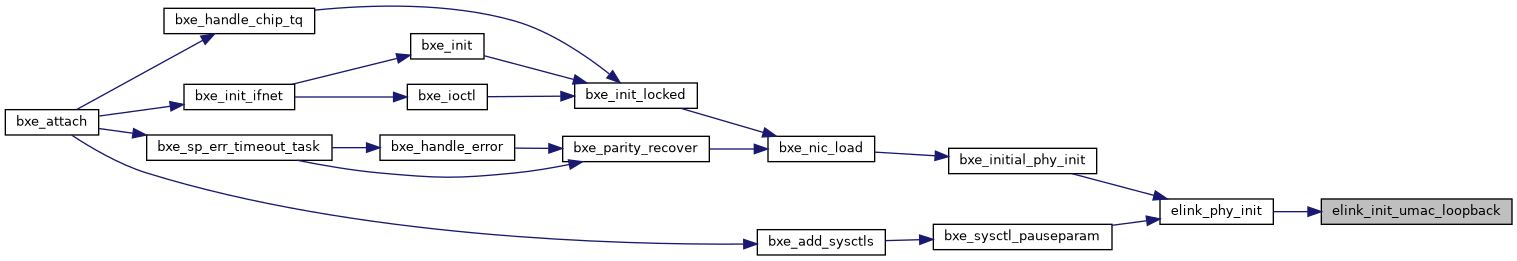

| static void | elink_init_umac_loopback (struct elink_params *params, struct elink_vars *vars) |

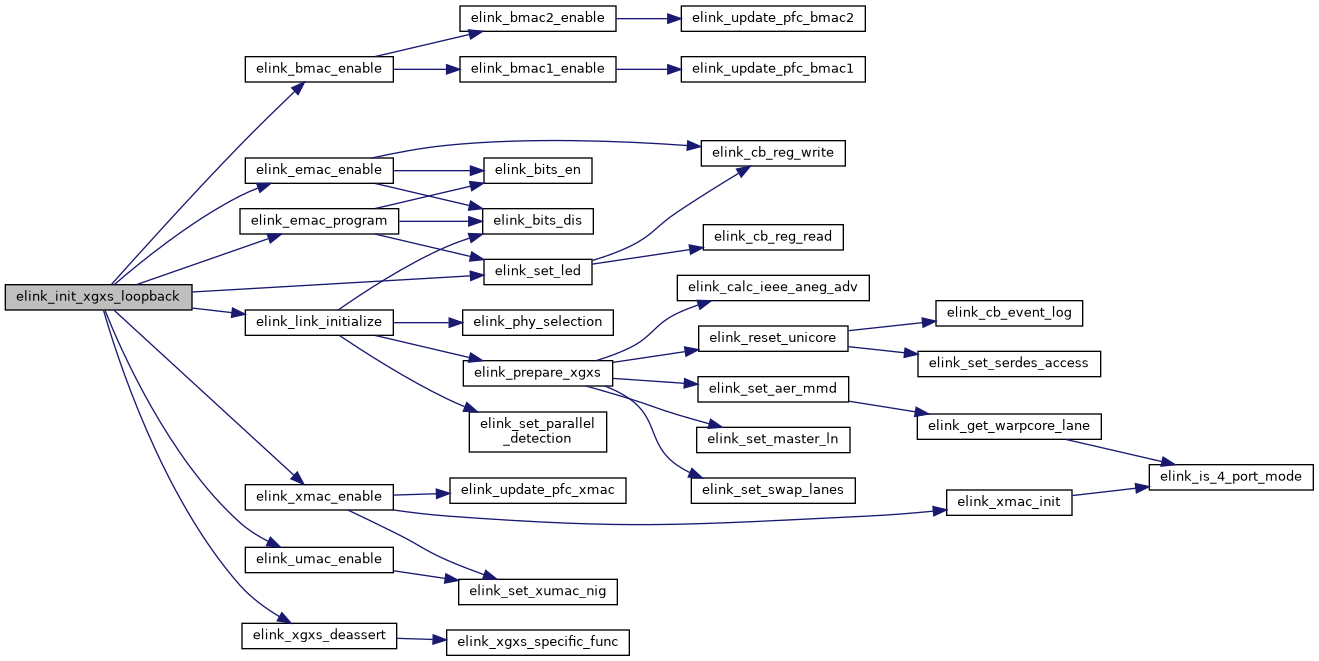

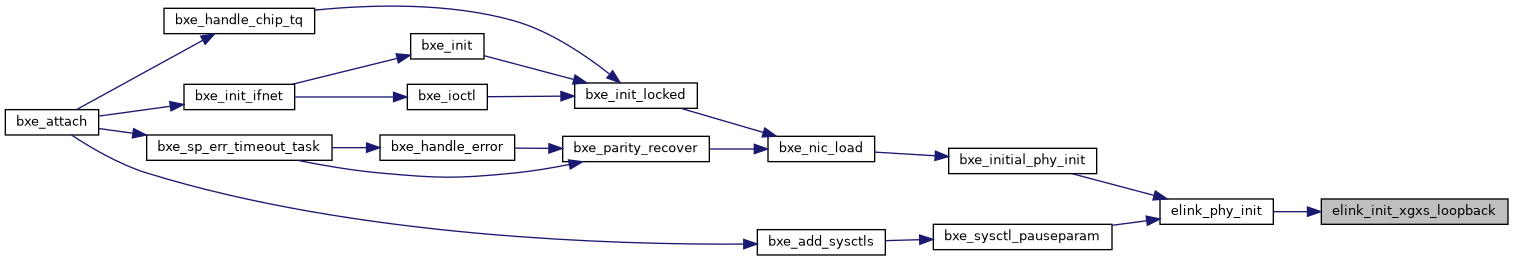

| static void | elink_init_xgxs_loopback (struct elink_params *params, struct elink_vars *vars) |

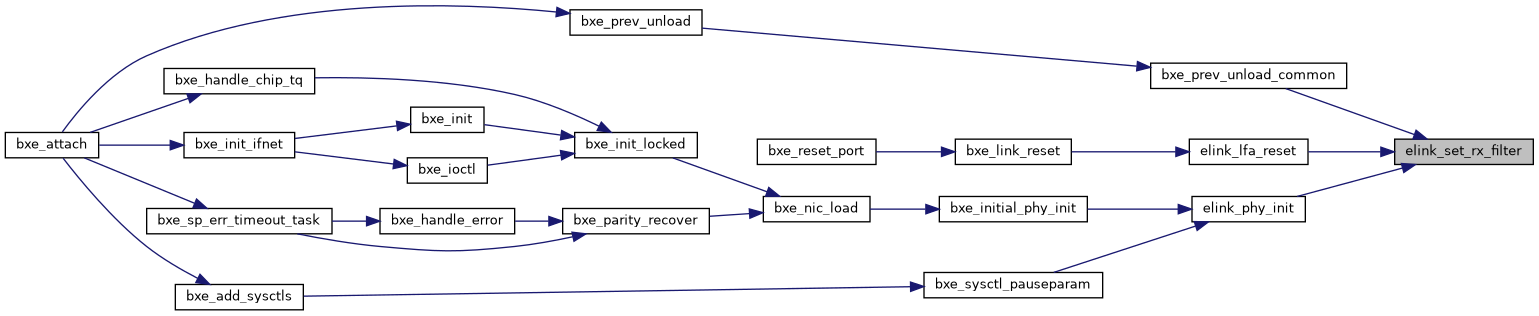

| void | elink_set_rx_filter (struct elink_params *params, uint8_t en) |

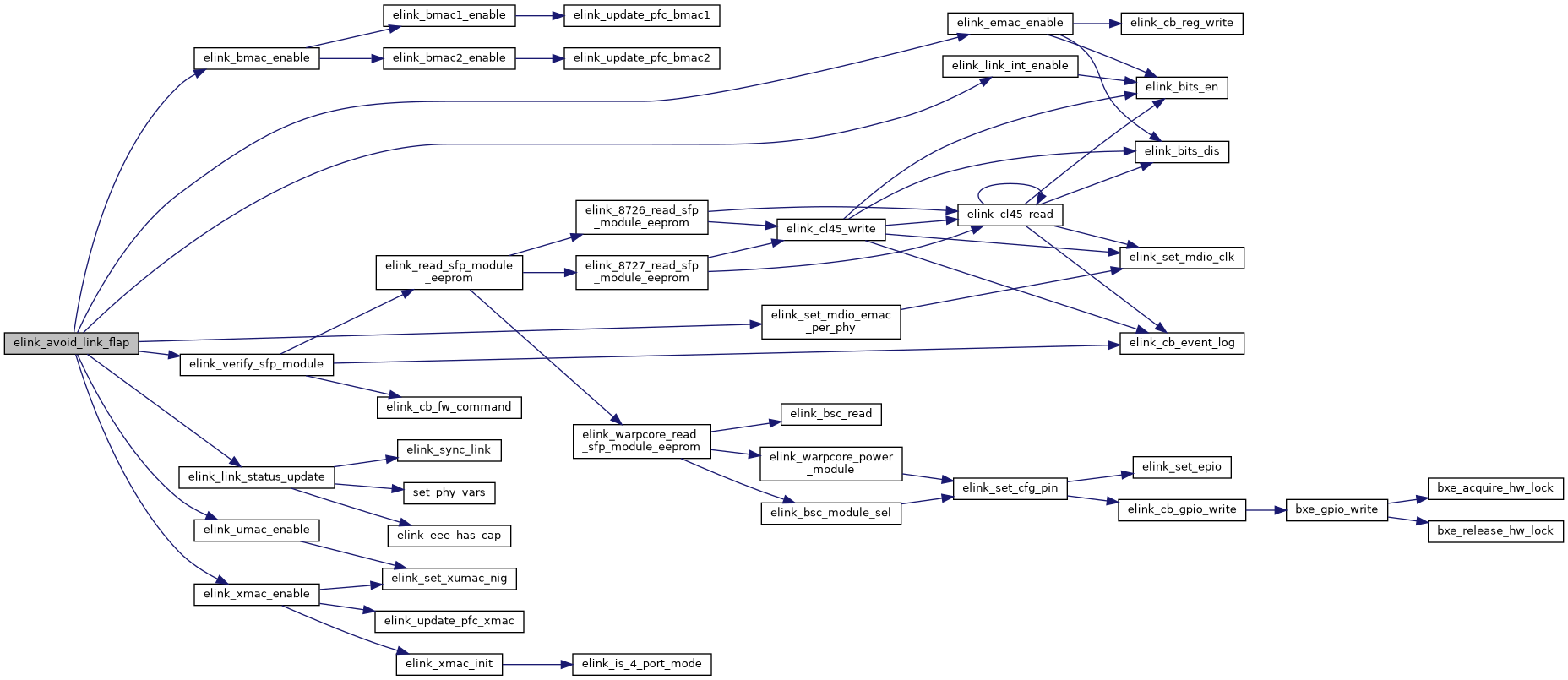

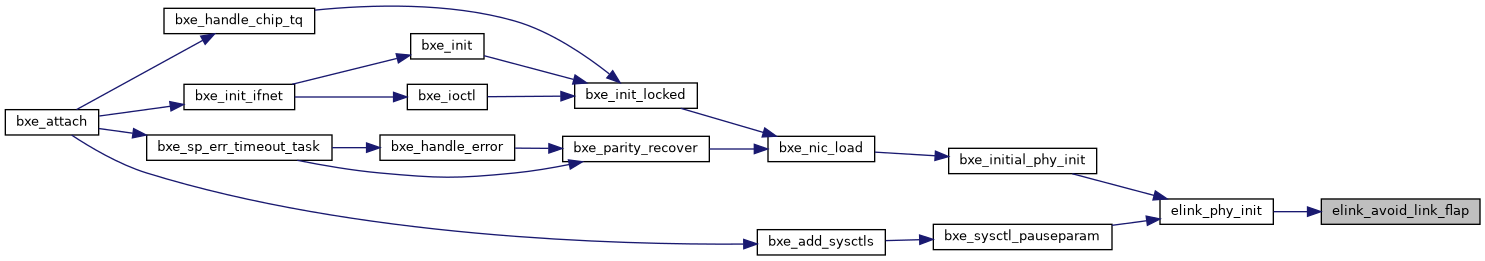

| static elink_status_t | elink_avoid_link_flap (struct elink_params *params, struct elink_vars *vars) |

| static void | elink_cannot_avoid_link_flap (struct elink_params *params, struct elink_vars *vars, int lfa_status) |

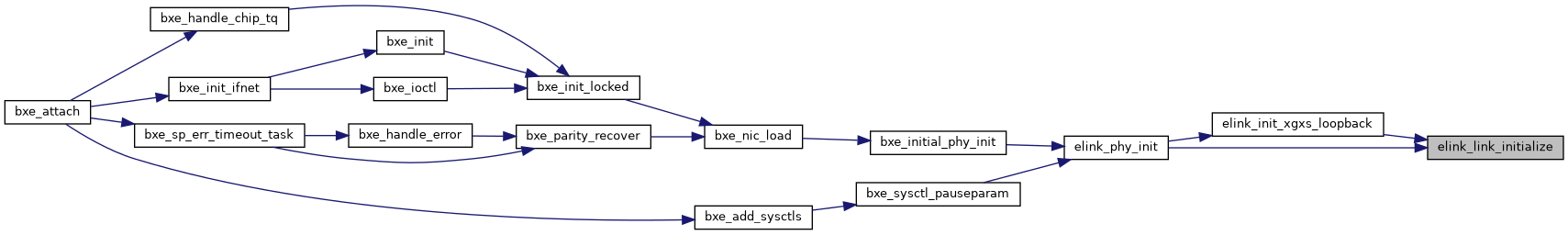

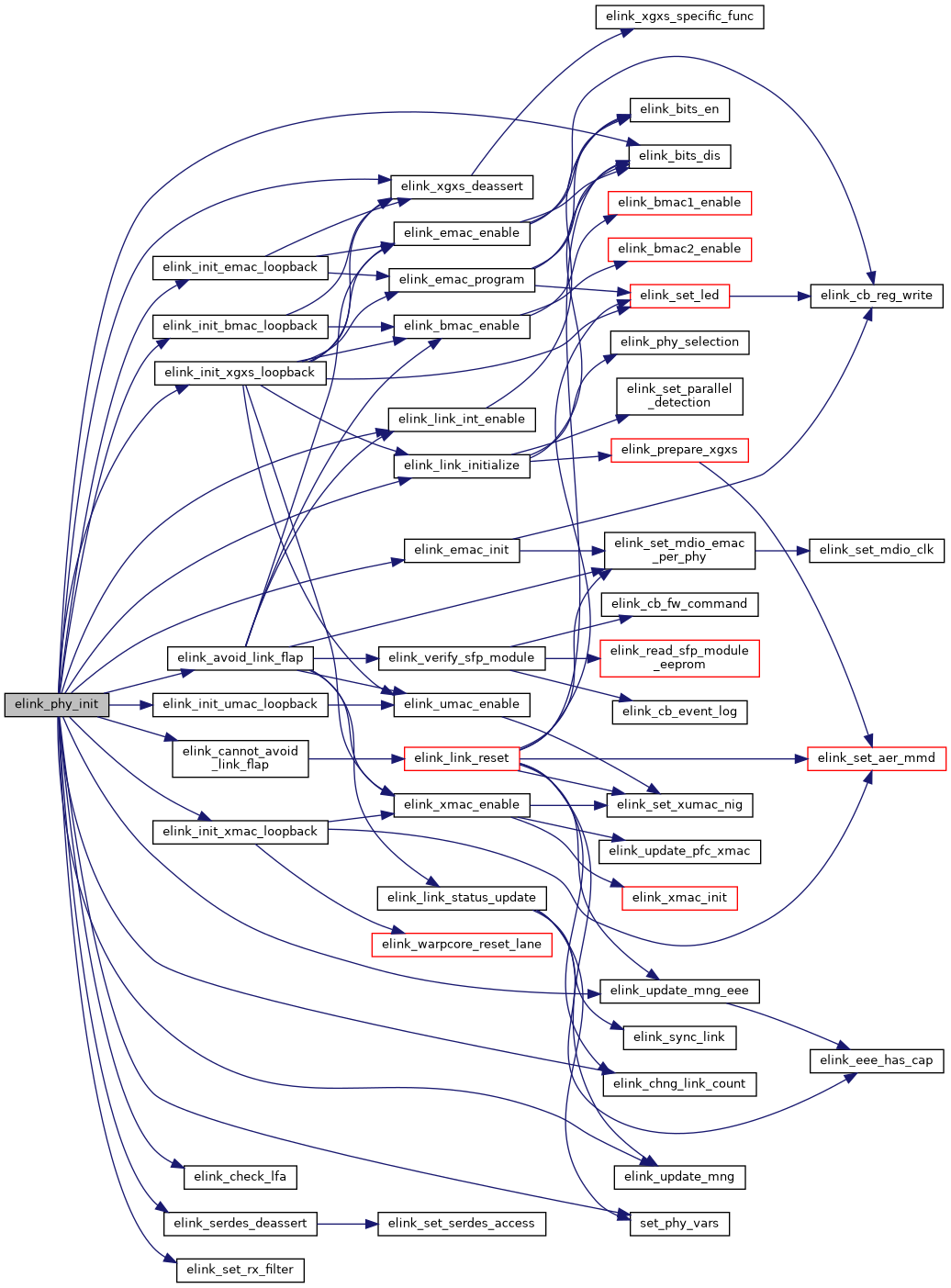

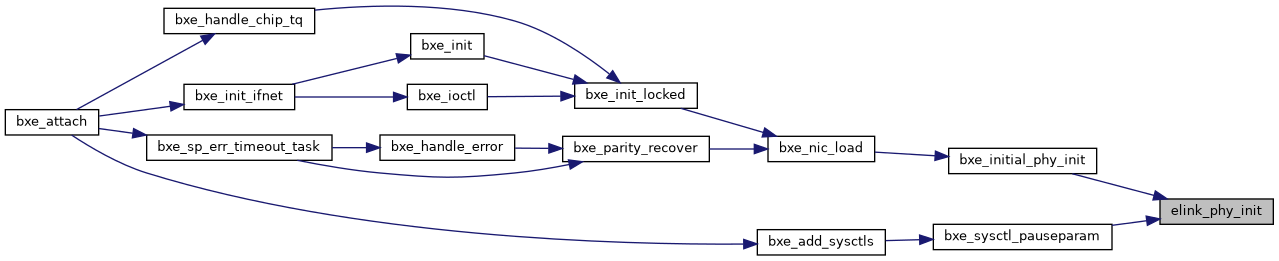

| elink_status_t | elink_phy_init (struct elink_params *params, struct elink_vars *vars) |

| elink_status_t | elink_link_reset (struct elink_params *params, struct elink_vars *vars, uint8_t reset_ext_phy) |

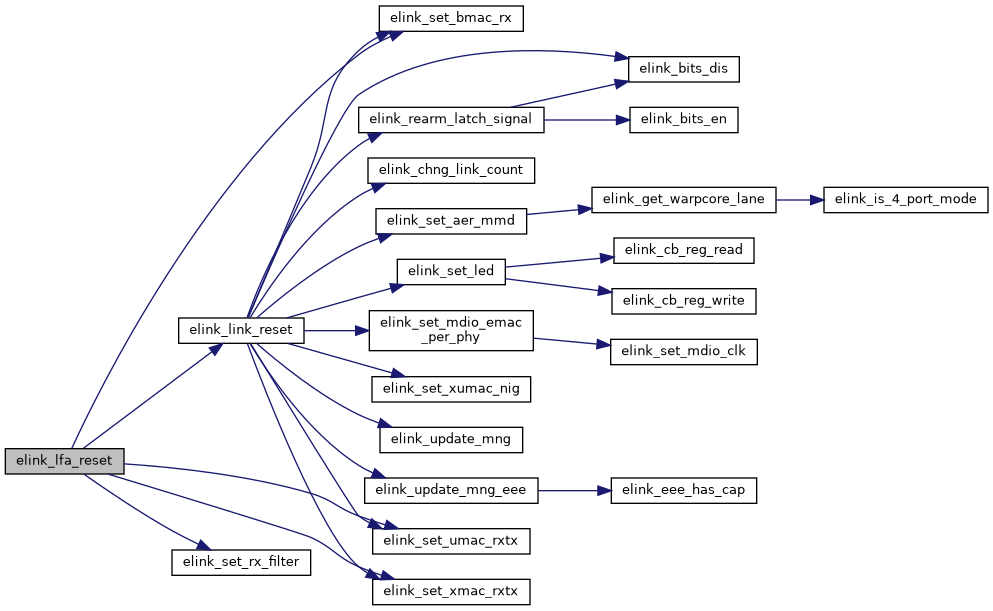

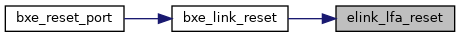

| elink_status_t | elink_lfa_reset (struct elink_params *params, struct elink_vars *vars) |

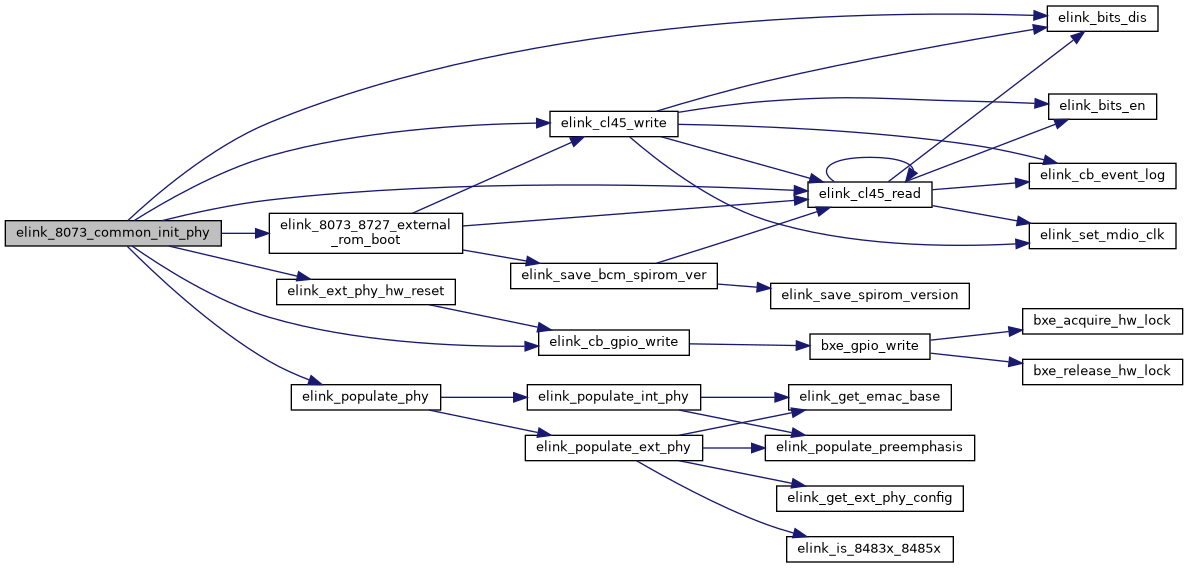

| static elink_status_t | elink_8073_common_init_phy (struct bxe_softc *sc, uint32_t shmem_base_path[], uint32_t shmem2_base_path[], uint8_t phy_index, uint32_t chip_id) |

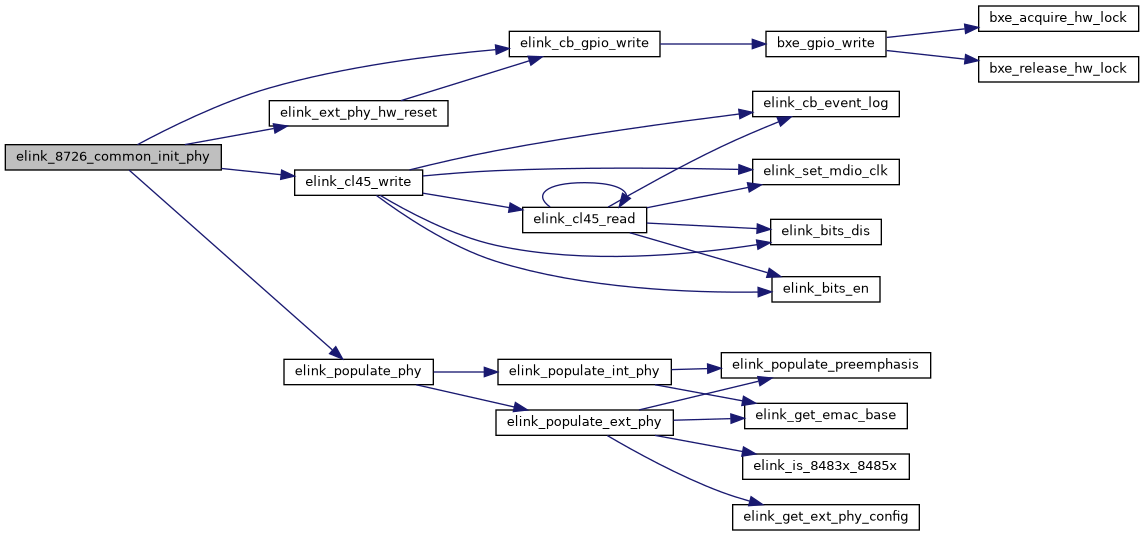

| static elink_status_t | elink_8726_common_init_phy (struct bxe_softc *sc, uint32_t shmem_base_path[], uint32_t shmem2_base_path[], uint8_t phy_index, uint32_t chip_id) |

| static void | elink_get_ext_phy_reset_gpio (struct bxe_softc *sc, uint32_t shmem_base, uint8_t *io_gpio, uint8_t *io_port) |

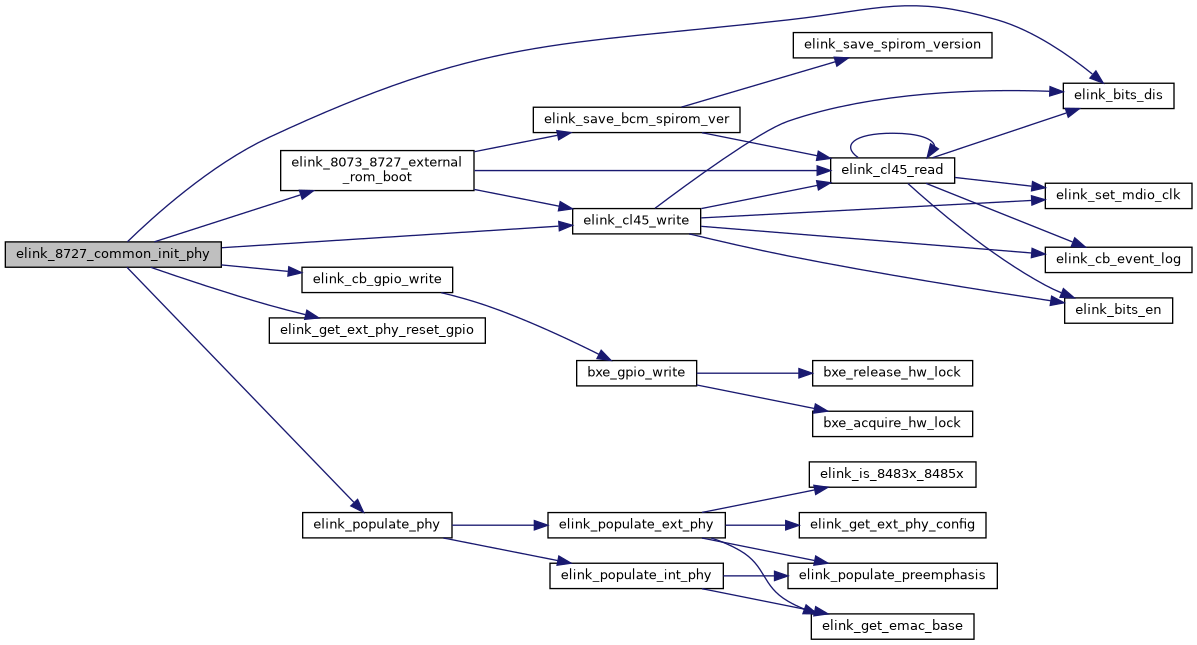

| static elink_status_t | elink_8727_common_init_phy (struct bxe_softc *sc, uint32_t shmem_base_path[], uint32_t shmem2_base_path[], uint8_t phy_index, uint32_t chip_id) |

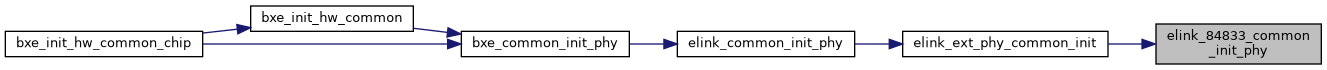

| static elink_status_t | elink_84833_common_init_phy (struct bxe_softc *sc, uint32_t shmem_base_path[], uint32_t shmem2_base_path[], uint8_t phy_index, uint32_t chip_id) |

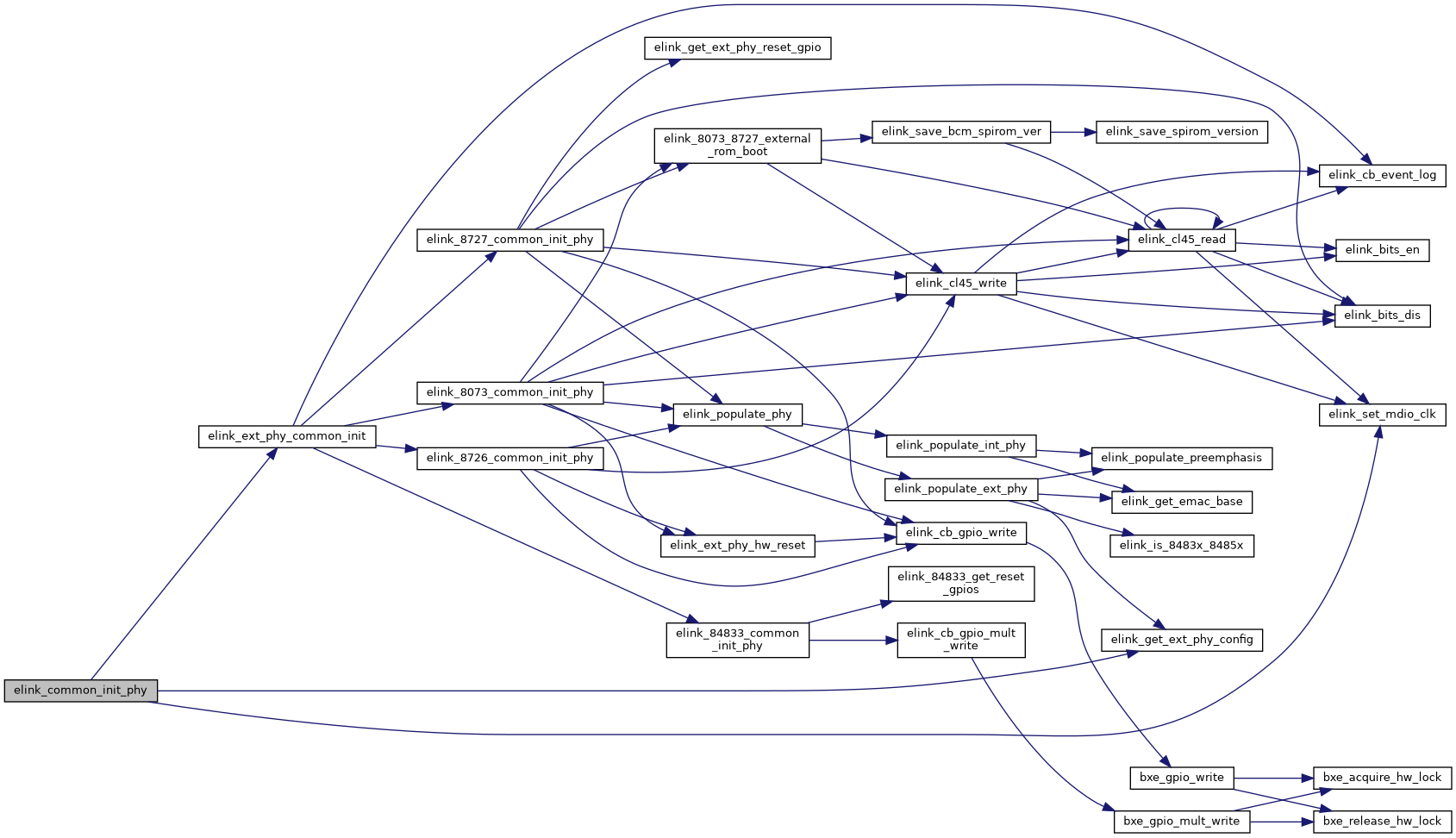

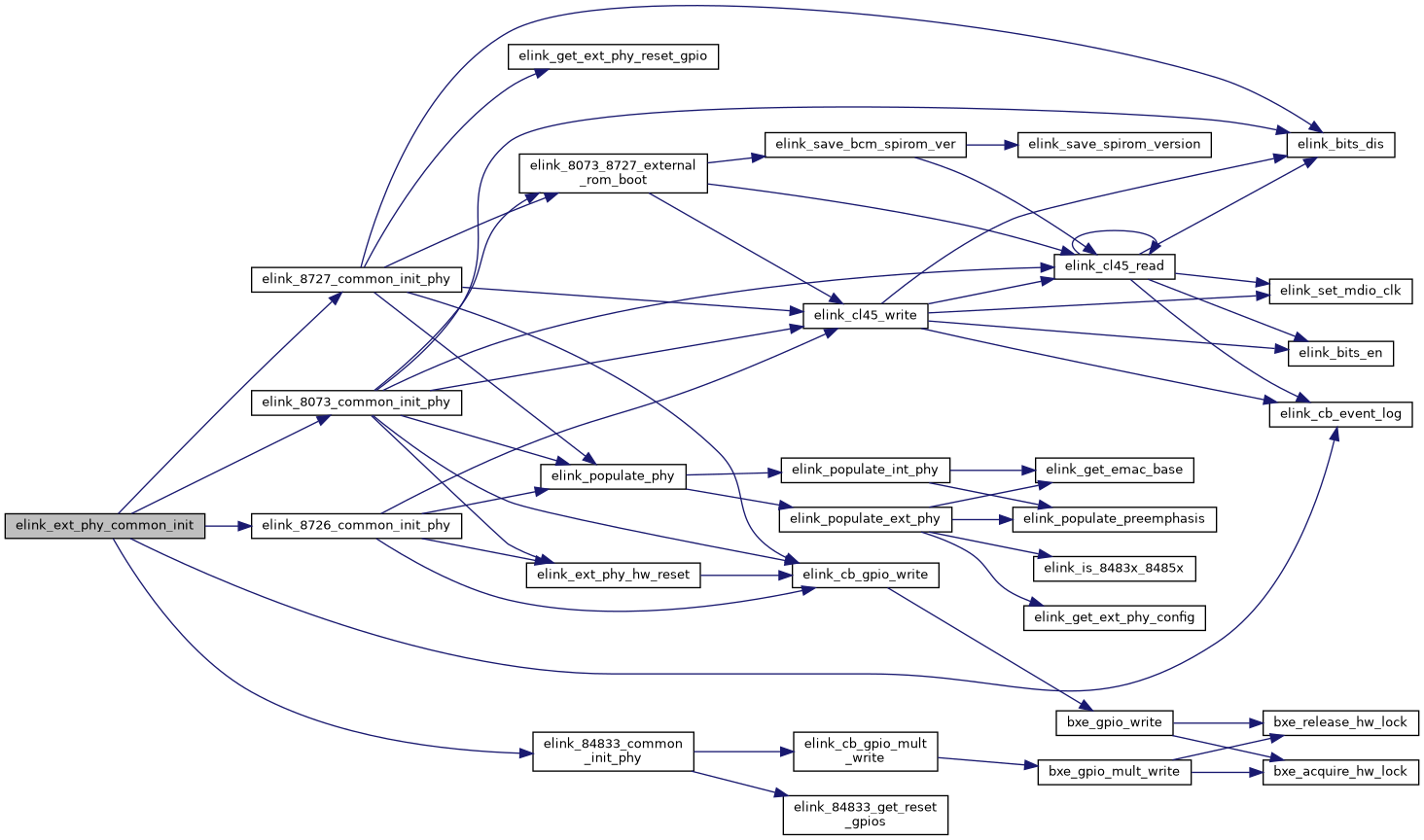

| static elink_status_t | elink_ext_phy_common_init (struct bxe_softc *sc, uint32_t shmem_base_path[], uint32_t shmem2_base_path[], uint8_t phy_index, uint32_t ext_phy_type, uint32_t chip_id) |

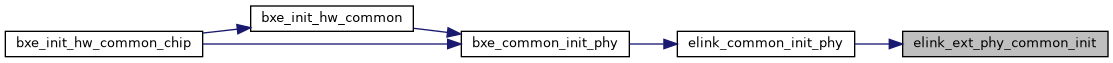

| elink_status_t | elink_common_init_phy (struct bxe_softc *sc, uint32_t shmem_base_path[], uint32_t shmem2_base_path[], uint32_t chip_id, uint8_t one_port_enabled) |

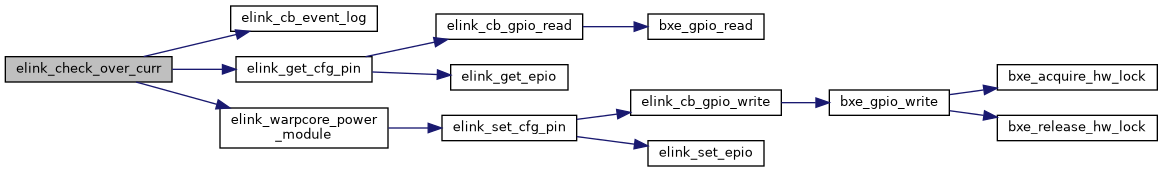

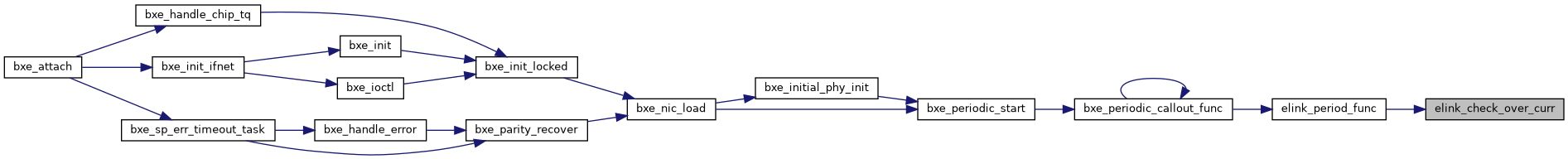

| static void | elink_check_over_curr (struct elink_params *params, struct elink_vars *vars) |

| static uint8_t | elink_analyze_link_error (struct elink_params *params, struct elink_vars *vars, uint32_t status, uint32_t phy_flag, uint32_t link_flag, uint8_t notify) |

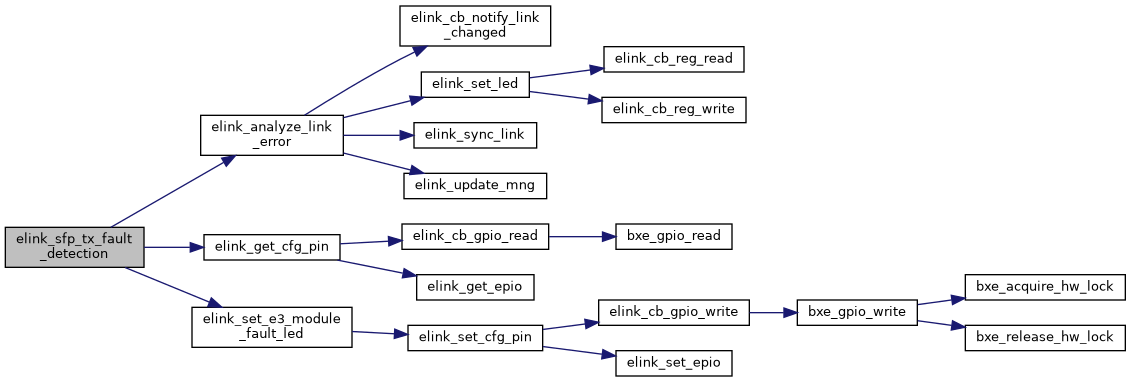

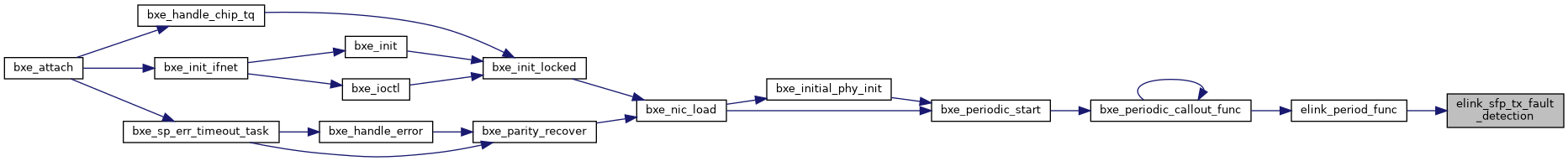

| static void | elink_sfp_tx_fault_detection (struct elink_phy *phy, struct elink_params *params, struct elink_vars *vars) |

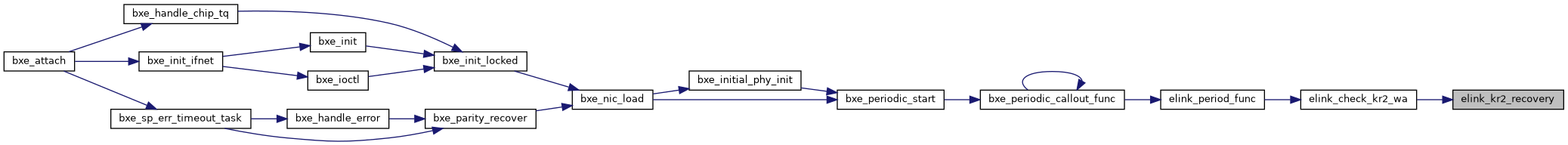

| static void | elink_kr2_recovery (struct elink_params *params, struct elink_vars *vars, struct elink_phy *phy) |

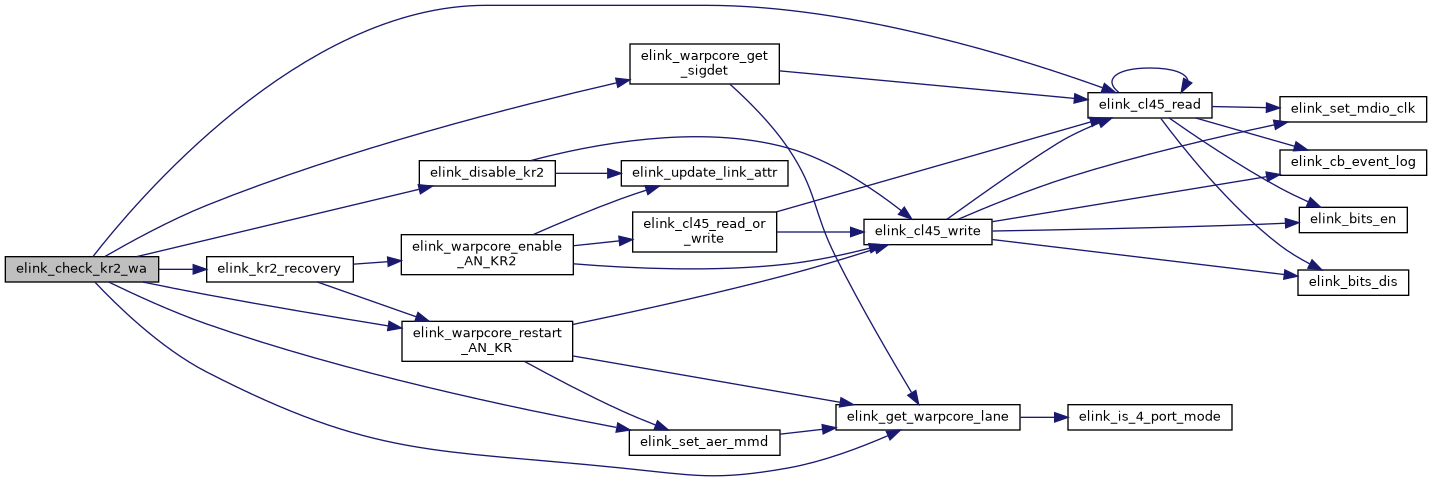

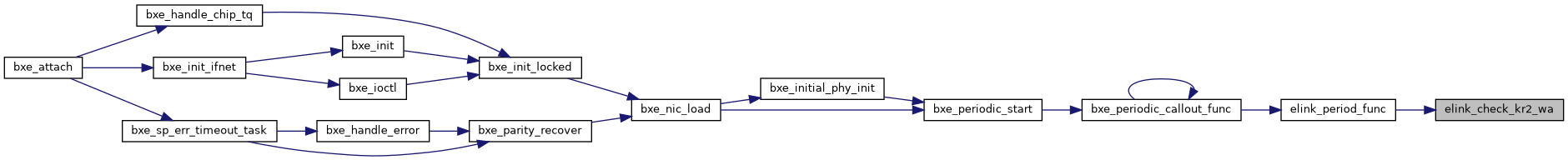

| static void | elink_check_kr2_wa (struct elink_params *params, struct elink_vars *vars, struct elink_phy *phy) |

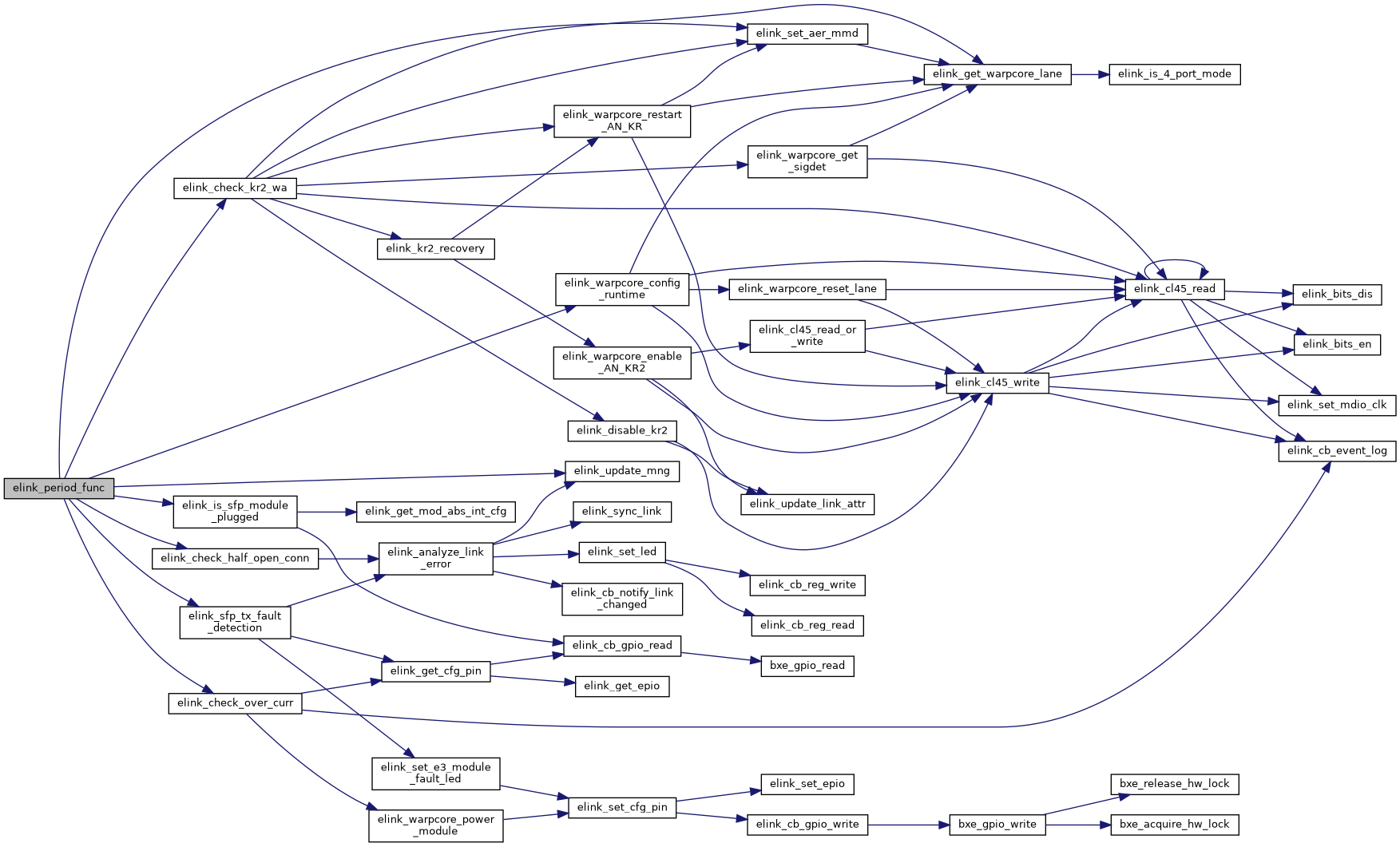

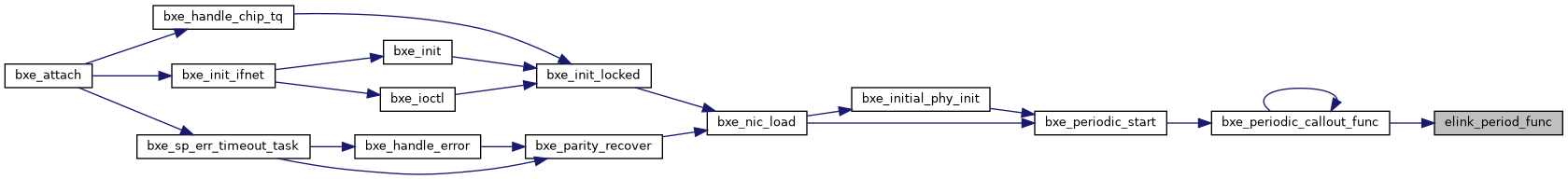

| void | elink_period_func (struct elink_params *params, struct elink_vars *vars) |

| uint8_t | elink_fan_failure_det_req (struct bxe_softc *sc, uint32_t shmem_base, uint32_t shmem2_base, uint8_t port) |

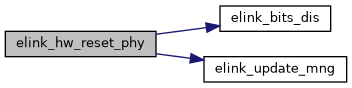

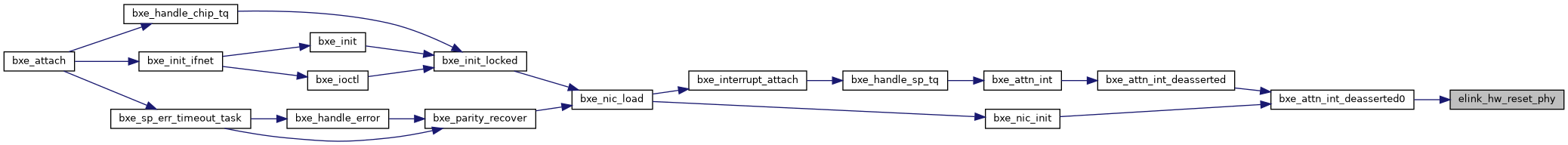

| void | elink_hw_reset_phy (struct elink_params *params) |

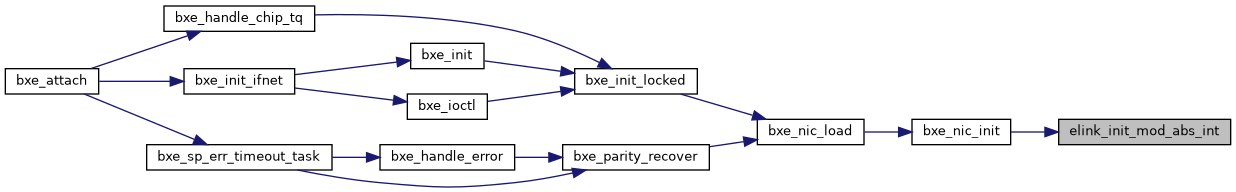

| void | elink_init_mod_abs_int (struct bxe_softc *sc, struct elink_vars *vars, uint32_t chip_id, uint32_t shmem_base, uint32_t shmem2_base, uint8_t port) |

Variables | |

| static const struct elink_phy | phy_null |

| static const struct elink_phy | phy_serdes |

| static const struct elink_phy | phy_xgxs |

| static const struct elink_phy | phy_warpcore |

| static const struct elink_phy | phy_7101 |

| static const struct elink_phy | phy_8073 |

| static const struct elink_phy | phy_8705 |

| static const struct elink_phy | phy_8706 |

| static const struct elink_phy | phy_8726 |

| static const struct elink_phy | phy_8727 |

| static const struct elink_phy | phy_8481 |

| static const struct elink_phy | phy_84823 |

| static const struct elink_phy | phy_84833 |

| static const struct elink_phy | phy_84834 |

| static const struct elink_phy | phy_84858 |

| static const struct elink_phy | phy_54618se |

Macro Definition Documentation

◆ BCM84858_PHY_ID

| #define BCM84858_PHY_ID 0x600d |

Definition at line 487 of file bxe_elink.c.

◆ CL22_RD_OVER_CL45

| #define CL22_RD_OVER_CL45 | ( | _sc, | |

| _phy, | |||

| _bank, | |||

| _addr, | |||

| _val | |||

| ) |

Definition at line 942 of file bxe_elink.c.

◆ CL22_WR_OVER_CL45

| #define CL22_WR_OVER_CL45 | ( | _sc, | |

| _phy, | |||

| _bank, | |||

| _addr, | |||

| _val | |||

| ) |

Definition at line 936 of file bxe_elink.c.

◆ DCBX_INVALID_COS

| #define DCBX_INVALID_COS (0xFF) |

Definition at line 917 of file bxe_elink.c.

◆ DEFAULT_TX_DRV_BRDCT

| #define DEFAULT_TX_DRV_BRDCT 2 |

Definition at line 927 of file bxe_elink.c.

◆ DEFAULT_TX_DRV_IFIR

| #define DEFAULT_TX_DRV_IFIR 0 |

Definition at line 928 of file bxe_elink.c.

◆ DEFAULT_TX_DRV_IPRE_DRIVER

| #define DEFAULT_TX_DRV_IPRE_DRIVER 6 |

Definition at line 930 of file bxe_elink.c.

◆ DEFAULT_TX_DRV_POST2

| #define DEFAULT_TX_DRV_POST2 3 |

Definition at line 929 of file bxe_elink.c.

◆ DIGITAL5_ACTUAL_SPEED_TX_MASK

| #define DIGITAL5_ACTUAL_SPEED_TX_MASK 0x003f |

Definition at line 733 of file bxe_elink.c.

◆ ELINK_AUTONEG_BAM

| #define ELINK_AUTONEG_BAM SHARED_HW_CFG_AN_ENABLE_BAM |

Definition at line 827 of file bxe_elink.c.

◆ ELINK_AUTONEG_CL37

| #define ELINK_AUTONEG_CL37 SHARED_HW_CFG_AN_ENABLE_CL37 |

Definition at line 825 of file bxe_elink.c.

◆ ELINK_AUTONEG_CL73

| #define ELINK_AUTONEG_CL73 SHARED_HW_CFG_AN_ENABLE_CL73 |

Definition at line 826 of file bxe_elink.c.

◆ ELINK_AUTONEG_PARALLEL

| #define ELINK_AUTONEG_PARALLEL SHARED_HW_CFG_AN_ENABLE_PARALLEL_DETECTION |

Definition at line 828 of file bxe_elink.c.

◆ ELINK_AUTONEG_REMOTE_PHY

| #define ELINK_AUTONEG_REMOTE_PHY SHARED_HW_CFG_AN_ENABLE_REMOTE_PHY |

Definition at line 832 of file bxe_elink.c.

◆ ELINK_AUTONEG_SGMII_FIBER_AUTODET

| #define ELINK_AUTONEG_SGMII_FIBER_AUTODET SHARED_HW_CFG_AN_EN_SGMII_FIBER_AUTO_DETECT |

Definition at line 830 of file bxe_elink.c.

◆ ELINK_EDC_MODE_ACTIVE_DAC

| #define ELINK_EDC_MODE_ACTIVE_DAC 0x0066 |

Definition at line 914 of file bxe_elink.c.

◆ ELINK_EDC_MODE_LIMITING

| #define ELINK_EDC_MODE_LIMITING 0x0044 |

Definition at line 912 of file bxe_elink.c.

◆ ELINK_EDC_MODE_LINEAR

| #define ELINK_EDC_MODE_LINEAR 0x0022 |

Definition at line 911 of file bxe_elink.c.

◆ ELINK_EDC_MODE_PASSIVE_DAC

| #define ELINK_EDC_MODE_PASSIVE_DAC 0x0055 |

Definition at line 913 of file bxe_elink.c.

◆ ELINK_ETH_HLEN

| #define ELINK_ETH_HLEN 14 |

Definition at line 764 of file bxe_elink.c.

◆ ELINK_ETH_MAX_JUMBO_PACKET_SIZE

| #define ELINK_ETH_MAX_JUMBO_PACKET_SIZE 9600 |

Definition at line 769 of file bxe_elink.c.

◆ ELINK_ETH_MAX_PACKET_SIZE

| #define ELINK_ETH_MAX_PACKET_SIZE 1500 |

Definition at line 768 of file bxe_elink.c.

◆ ELINK_ETH_MIN_PACKET_SIZE

| #define ELINK_ETH_MIN_PACKET_SIZE 60 |

Definition at line 767 of file bxe_elink.c.

◆ ELINK_ETH_OVREHEAD

| #define ELINK_ETH_OVREHEAD (ELINK_ETH_HLEN + 8 + 8) |

Definition at line 766 of file bxe_elink.c.

◆ ELINK_ETS_BW_LIMIT_CREDIT_UPPER_BOUND

| #define ELINK_ETS_BW_LIMIT_CREDIT_UPPER_BOUND (0x5000) |

Definition at line 919 of file bxe_elink.c.

◆ ELINK_ETS_BW_LIMIT_CREDIT_WEIGHT

| #define ELINK_ETS_BW_LIMIT_CREDIT_WEIGHT (0x5000) |

Definition at line 920 of file bxe_elink.c.

◆ ELINK_ETS_E3B0_NIG_MIN_W_VAL_20GBPS

| #define ELINK_ETS_E3B0_NIG_MIN_W_VAL_20GBPS (2720) |

Definition at line 922 of file bxe_elink.c.

◆ ELINK_ETS_E3B0_NIG_MIN_W_VAL_UP_TO_10GBPS

| #define ELINK_ETS_E3B0_NIG_MIN_W_VAL_UP_TO_10GBPS (1360) |

Definition at line 921 of file bxe_elink.c.

◆ ELINK_ETS_E3B0_PBF_MIN_W_VAL

| #define ELINK_ETS_E3B0_PBF_MIN_W_VAL (10000) |

Definition at line 923 of file bxe_elink.c.

◆ ELINK_GP_STATUS_100M

| #define ELINK_GP_STATUS_100M MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_100M |

Definition at line 841 of file bxe_elink.c.

◆ ELINK_GP_STATUS_10G_CX4

| #define ELINK_GP_STATUS_10G_CX4 MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_10G_CX4 |

Definition at line 848 of file bxe_elink.c.

◆ ELINK_GP_STATUS_10G_HIG

| #define ELINK_GP_STATUS_10G_HIG MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_10G_HIG |

Definition at line 846 of file bxe_elink.c.

◆ ELINK_GP_STATUS_10G_KR

| #define ELINK_GP_STATUS_10G_KR MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_10G_KR |

Definition at line 853 of file bxe_elink.c.

◆ ELINK_GP_STATUS_10G_KX4

| #define ELINK_GP_STATUS_10G_KX4 MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_10G_KX4 |

Definition at line 851 of file bxe_elink.c.

◆ ELINK_GP_STATUS_10G_SFI

| #define ELINK_GP_STATUS_10G_SFI MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_10G_SFI |

Definition at line 856 of file bxe_elink.c.

◆ ELINK_GP_STATUS_10G_XFI

| #define ELINK_GP_STATUS_10G_XFI MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_10G_XFI |

Definition at line 854 of file bxe_elink.c.

◆ ELINK_GP_STATUS_10M

| #define ELINK_GP_STATUS_10M MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_10M |

Definition at line 840 of file bxe_elink.c.

◆ ELINK_GP_STATUS_1G

| #define ELINK_GP_STATUS_1G MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_1G |

Definition at line 842 of file bxe_elink.c.

◆ ELINK_GP_STATUS_1G_KX

| #define ELINK_GP_STATUS_1G_KX MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_1G_KX |

Definition at line 850 of file bxe_elink.c.

◆ ELINK_GP_STATUS_20G_DXGXS

| #define ELINK_GP_STATUS_20G_DXGXS MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_20G_DXGXS |

Definition at line 855 of file bxe_elink.c.

◆ ELINK_GP_STATUS_20G_KR2

| #define ELINK_GP_STATUS_20G_KR2 MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_20G_KR2 |

Definition at line 857 of file bxe_elink.c.

◆ ELINK_GP_STATUS_2_5G

| #define ELINK_GP_STATUS_2_5G MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_2_5G |

Definition at line 843 of file bxe_elink.c.

◆ ELINK_GP_STATUS_5G

| #define ELINK_GP_STATUS_5G MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_5G |

Definition at line 844 of file bxe_elink.c.

◆ ELINK_GP_STATUS_6G

| #define ELINK_GP_STATUS_6G MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_6G |

Definition at line 845 of file bxe_elink.c.

◆ ELINK_GP_STATUS_PAUSE_RSOLUTION_RXSIDE

| #define ELINK_GP_STATUS_PAUSE_RSOLUTION_RXSIDE MDIO_GP_STATUS_TOP_AN_STATUS1_PAUSE_RSOLUTION_RXSIDE |

Definition at line 836 of file bxe_elink.c.

◆ ELINK_GP_STATUS_PAUSE_RSOLUTION_TXSIDE

| #define ELINK_GP_STATUS_PAUSE_RSOLUTION_TXSIDE MDIO_GP_STATUS_TOP_AN_STATUS1_PAUSE_RSOLUTION_TXSIDE |

Definition at line 834 of file bxe_elink.c.

◆ ELINK_GP_STATUS_SPEED_MASK

| #define ELINK_GP_STATUS_SPEED_MASK MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_MASK |

Definition at line 838 of file bxe_elink.c.

◆ ELINK_LINK_1000TFD

| #define ELINK_LINK_1000TFD LINK_STATUS_SPEED_AND_DUPLEX_1000TFD |

Definition at line 864 of file bxe_elink.c.

◆ ELINK_LINK_1000THD

| #define ELINK_LINK_1000THD LINK_STATUS_SPEED_AND_DUPLEX_1000THD |

Definition at line 863 of file bxe_elink.c.

◆ ELINK_LINK_1000XFD

| #define ELINK_LINK_1000XFD LINK_STATUS_SPEED_AND_DUPLEX_1000XFD |

Definition at line 865 of file bxe_elink.c.

◆ ELINK_LINK_100T4

| #define ELINK_LINK_100T4 LINK_STATUS_SPEED_AND_DUPLEX_100T4 |

Definition at line 861 of file bxe_elink.c.

◆ ELINK_LINK_100TXFD

| #define ELINK_LINK_100TXFD LINK_STATUS_SPEED_AND_DUPLEX_100TXFD |

Definition at line 862 of file bxe_elink.c.

◆ ELINK_LINK_100TXHD

| #define ELINK_LINK_100TXHD LINK_STATUS_SPEED_AND_DUPLEX_100TXHD |

Definition at line 860 of file bxe_elink.c.

◆ ELINK_LINK_10GTFD

| #define ELINK_LINK_10GTFD LINK_STATUS_SPEED_AND_DUPLEX_10GTFD |

Definition at line 869 of file bxe_elink.c.

◆ ELINK_LINK_10GXFD

| #define ELINK_LINK_10GXFD LINK_STATUS_SPEED_AND_DUPLEX_10GXFD |

Definition at line 870 of file bxe_elink.c.

◆ ELINK_LINK_10TFD

| #define ELINK_LINK_10TFD LINK_STATUS_SPEED_AND_DUPLEX_10TFD |

Definition at line 859 of file bxe_elink.c.

◆ ELINK_LINK_10THD

| #define ELINK_LINK_10THD LINK_STATUS_SPEED_AND_DUPLEX_10THD |

Definition at line 858 of file bxe_elink.c.

◆ ELINK_LINK_20GTFD

| #define ELINK_LINK_20GTFD LINK_STATUS_SPEED_AND_DUPLEX_20GTFD |

Definition at line 871 of file bxe_elink.c.

◆ ELINK_LINK_20GXFD

| #define ELINK_LINK_20GXFD LINK_STATUS_SPEED_AND_DUPLEX_20GXFD |

Definition at line 872 of file bxe_elink.c.

◆ ELINK_LINK_2500TFD

| #define ELINK_LINK_2500TFD LINK_STATUS_SPEED_AND_DUPLEX_2500TFD |

Definition at line 867 of file bxe_elink.c.

◆ ELINK_LINK_2500THD

| #define ELINK_LINK_2500THD LINK_STATUS_SPEED_AND_DUPLEX_2500THD |

Definition at line 866 of file bxe_elink.c.

◆ ELINK_LINK_2500XFD

| #define ELINK_LINK_2500XFD LINK_STATUS_SPEED_AND_DUPLEX_2500XFD |

Definition at line 868 of file bxe_elink.c.

◆ ELINK_LINK_UPDATE_MASK

| #define ELINK_LINK_UPDATE_MASK |

Definition at line 874 of file bxe_elink.c.

◆ ELINK_MAX_PACKET_SIZE

| #define ELINK_MAX_PACKET_SIZE (9700) |

Definition at line 925 of file bxe_elink.c.

◆ ELINK_MDIO_ACCESS_TIMEOUT

| #define ELINK_MDIO_ACCESS_TIMEOUT 1000 |

Definition at line 770 of file bxe_elink.c.

◆ ELINK_MDIO_AN_CL73_OR_37_COMPLETE

| #define ELINK_MDIO_AN_CL73_OR_37_COMPLETE |

Definition at line 808 of file bxe_elink.c.

◆ ELINK_NIG_LATCH_BC_ENABLE_MI_INT

| #define ELINK_NIG_LATCH_BC_ENABLE_MI_INT 0 |

Definition at line 787 of file bxe_elink.c.

◆ ELINK_NIG_MASK_MI_INT

| #define ELINK_NIG_MASK_MI_INT NIG_MASK_INTERRUPT_PORT0_REG_MASK_EMAC0_MISC_MI_INT |

Definition at line 799 of file bxe_elink.c.

◆ ELINK_NIG_MASK_SERDES0_LINK_STATUS

| #define ELINK_NIG_MASK_SERDES0_LINK_STATUS NIG_MASK_INTERRUPT_PORT0_REG_MASK_SERDES0_LINK_STATUS |

Definition at line 805 of file bxe_elink.c.

◆ ELINK_NIG_MASK_XGXS0_LINK10G

| #define ELINK_NIG_MASK_XGXS0_LINK10G NIG_MASK_INTERRUPT_PORT0_REG_MASK_XGXS0_LINK10G |

Definition at line 801 of file bxe_elink.c.

◆ ELINK_NIG_MASK_XGXS0_LINK_STATUS

| #define ELINK_NIG_MASK_XGXS0_LINK_STATUS NIG_MASK_INTERRUPT_PORT0_REG_MASK_XGXS0_LINK_STATUS |

Definition at line 803 of file bxe_elink.c.

◆ ELINK_NIG_STATUS_EMAC0_MI_INT

| #define ELINK_NIG_STATUS_EMAC0_MI_INT NIG_STATUS_INTERRUPT_PORT0_REG_STATUS_EMAC0_MISC_MI_INT |

Definition at line 789 of file bxe_elink.c.

◆ ELINK_NIG_STATUS_SERDES0_LINK_STATUS

| #define ELINK_NIG_STATUS_SERDES0_LINK_STATUS NIG_STATUS_INTERRUPT_PORT0_REG_STATUS_SERDES0_LINK_STATUS |

Definition at line 797 of file bxe_elink.c.

◆ ELINK_NIG_STATUS_XGXS0_LINK10G

| #define ELINK_NIG_STATUS_XGXS0_LINK10G NIG_STATUS_INTERRUPT_PORT0_REG_STATUS_XGXS0_LINK10G |

Definition at line 791 of file bxe_elink.c.

◆ ELINK_NIG_STATUS_XGXS0_LINK_STATUS

| #define ELINK_NIG_STATUS_XGXS0_LINK_STATUS NIG_STATUS_INTERRUPT_PORT0_REG_STATUS_XGXS0_LINK_STATUS |

Definition at line 793 of file bxe_elink.c.

◆ ELINK_NIG_STATUS_XGXS0_LINK_STATUS_SIZE

| #define ELINK_NIG_STATUS_XGXS0_LINK_STATUS_SIZE NIG_STATUS_INTERRUPT_PORT0_REG_STATUS_XGXS0_LINK_STATUS_SIZE |

Definition at line 795 of file bxe_elink.c.

◆ ELINK_SERDES_RESET_BITS

| #define ELINK_SERDES_RESET_BITS |

Definition at line 819 of file bxe_elink.c.

◆ ELINK_SFP_EEPROM_10G_COMP_CODE_ADDR

| #define ELINK_SFP_EEPROM_10G_COMP_CODE_ADDR 0x3 |

Definition at line 892 of file bxe_elink.c.

◆ ELINK_SFP_EEPROM_10G_COMP_CODE_LR_MASK

| #define ELINK_SFP_EEPROM_10G_COMP_CODE_LR_MASK (1<<5) |

Definition at line 894 of file bxe_elink.c.

◆ ELINK_SFP_EEPROM_10G_COMP_CODE_LRM_MASK

| #define ELINK_SFP_EEPROM_10G_COMP_CODE_LRM_MASK (1<<6) |

Definition at line 895 of file bxe_elink.c.

◆ ELINK_SFP_EEPROM_10G_COMP_CODE_SR_MASK

| #define ELINK_SFP_EEPROM_10G_COMP_CODE_SR_MASK (1<<4) |

Definition at line 893 of file bxe_elink.c.

◆ ELINK_SFP_EEPROM_1G_COMP_CODE_ADDR

| #define ELINK_SFP_EEPROM_1G_COMP_CODE_ADDR 0x6 |

Definition at line 897 of file bxe_elink.c.

◆ ELINK_SFP_EEPROM_1G_COMP_CODE_BASE_T

| #define ELINK_SFP_EEPROM_1G_COMP_CODE_BASE_T (1<<3) |

Definition at line 901 of file bxe_elink.c.

◆ ELINK_SFP_EEPROM_1G_COMP_CODE_CX

| #define ELINK_SFP_EEPROM_1G_COMP_CODE_CX (1<<2) |

Definition at line 900 of file bxe_elink.c.

◆ ELINK_SFP_EEPROM_1G_COMP_CODE_LX

| #define ELINK_SFP_EEPROM_1G_COMP_CODE_LX (1<<1) |

Definition at line 899 of file bxe_elink.c.

◆ ELINK_SFP_EEPROM_1G_COMP_CODE_SX

| #define ELINK_SFP_EEPROM_1G_COMP_CODE_SX (1<<0) |

Definition at line 898 of file bxe_elink.c.

◆ ELINK_SFP_EEPROM_CON_TYPE_ADDR

| #define ELINK_SFP_EEPROM_CON_TYPE_ADDR 0x2 |

Definition at line 885 of file bxe_elink.c.

◆ ELINK_SFP_EEPROM_CON_TYPE_VAL_COPPER

| #define ELINK_SFP_EEPROM_CON_TYPE_VAL_COPPER 0x21 |

Definition at line 888 of file bxe_elink.c.

◆ ELINK_SFP_EEPROM_CON_TYPE_VAL_LC

| #define ELINK_SFP_EEPROM_CON_TYPE_VAL_LC 0x7 |

Definition at line 887 of file bxe_elink.c.

◆ ELINK_SFP_EEPROM_CON_TYPE_VAL_RJ45

| #define ELINK_SFP_EEPROM_CON_TYPE_VAL_RJ45 0x22 |

Definition at line 889 of file bxe_elink.c.

◆ ELINK_SFP_EEPROM_CON_TYPE_VAL_UNKNOWN

| #define ELINK_SFP_EEPROM_CON_TYPE_VAL_UNKNOWN 0x0 |

Definition at line 886 of file bxe_elink.c.

◆ ELINK_SFP_EEPROM_FC_TX_TECH_ADDR

| #define ELINK_SFP_EEPROM_FC_TX_TECH_ADDR 0x8 |

Definition at line 903 of file bxe_elink.c.

◆ ELINK_SFP_EEPROM_FC_TX_TECH_BITMASK_COPPER_ACTIVE

| #define ELINK_SFP_EEPROM_FC_TX_TECH_BITMASK_COPPER_ACTIVE 0x8 |

Definition at line 905 of file bxe_elink.c.

◆ ELINK_SFP_EEPROM_FC_TX_TECH_BITMASK_COPPER_PASSIVE

| #define ELINK_SFP_EEPROM_FC_TX_TECH_BITMASK_COPPER_PASSIVE 0x4 |

Definition at line 904 of file bxe_elink.c.

◆ ELINK_SFP_EEPROM_OPTIONS_ADDR

| #define ELINK_SFP_EEPROM_OPTIONS_ADDR 0x40 |

Definition at line 907 of file bxe_elink.c.

◆ ELINK_SFP_EEPROM_OPTIONS_LINEAR_RX_OUT_MASK

| #define ELINK_SFP_EEPROM_OPTIONS_LINEAR_RX_OUT_MASK 0x1 |

Definition at line 908 of file bxe_elink.c.

◆ ELINK_SFP_EEPROM_OPTIONS_SIZE

| #define ELINK_SFP_EEPROM_OPTIONS_SIZE 2 |

Definition at line 909 of file bxe_elink.c.

◆ ELINK_XGXS_RESET_BITS

| #define ELINK_XGXS_RESET_BITS |

Definition at line 812 of file bxe_elink.c.

◆ I2C_BSC0

| #define I2C_BSC0 0 |

Definition at line 773 of file bxe_elink.c.

◆ I2C_BSC1

| #define I2C_BSC1 1 |

Definition at line 774 of file bxe_elink.c.

◆ I2C_SWITCH_WIDTH

| #define I2C_SWITCH_WIDTH 2 |

Definition at line 772 of file bxe_elink.c.

◆ I2C_WA_PWR_ITER

| #define I2C_WA_PWR_ITER (I2C_WA_RETRY_CNT - 1) |

Definition at line 776 of file bxe_elink.c.

◆ I2C_WA_RETRY_CNT

| #define I2C_WA_RETRY_CNT 3 |

Definition at line 775 of file bxe_elink.c.

◆ LED_BLINK_RATE_VAL_E1X_E2

| #define LED_BLINK_RATE_VAL_E1X_E2 480 |

Definition at line 782 of file bxe_elink.c.

◆ LED_BLINK_RATE_VAL_E3

| #define LED_BLINK_RATE_VAL_E3 354 |

Definition at line 781 of file bxe_elink.c.

◆ MAX_KR_LINK_RETRY

| #define MAX_KR_LINK_RETRY 4 |

Definition at line 926 of file bxe_elink.c.

◆ MCPR_IMC_COMMAND_READ_OP

| #define MCPR_IMC_COMMAND_READ_OP 1 |

Definition at line 777 of file bxe_elink.c.

◆ MCPR_IMC_COMMAND_WRITE_OP

| #define MCPR_IMC_COMMAND_WRITE_OP 2 |

Definition at line 778 of file bxe_elink.c.

◆ MDIO_10G_PARALLEL_DETECT_PAR_DET_10G_CONTROL

| #define MDIO_10G_PARALLEL_DETECT_PAR_DET_10G_CONTROL 0x11 |

Definition at line 196 of file bxe_elink.c.

◆ MDIO_10G_PARALLEL_DETECT_PAR_DET_10G_CONTROL_PARDET10G_EN

| #define MDIO_10G_PARALLEL_DETECT_PAR_DET_10G_CONTROL_PARDET10G_EN 0x1 |

Definition at line 197 of file bxe_elink.c.

◆ MDIO_10G_PARALLEL_DETECT_PAR_DET_10G_LINK

| #define MDIO_10G_PARALLEL_DETECT_PAR_DET_10G_LINK 0x13 |

Definition at line 198 of file bxe_elink.c.

◆ MDIO_10G_PARALLEL_DETECT_PAR_DET_10G_LINK_CNT

| #define MDIO_10G_PARALLEL_DETECT_PAR_DET_10G_LINK_CNT (0xb71<<1) |

Definition at line 199 of file bxe_elink.c.

◆ MDIO_10G_PARALLEL_DETECT_PAR_DET_10G_STATUS

| #define MDIO_10G_PARALLEL_DETECT_PAR_DET_10G_STATUS 0x10 |

Definition at line 194 of file bxe_elink.c.

◆ MDIO_10G_PARALLEL_DETECT_PAR_DET_10G_STATUS_PD_LINK

| #define MDIO_10G_PARALLEL_DETECT_PAR_DET_10G_STATUS_PD_LINK 0x8000 |

Definition at line 195 of file bxe_elink.c.

◆ MDIO_84833_SUPER_ISOLATE

| #define MDIO_84833_SUPER_ISOLATE 0x8000 |

Definition at line 531 of file bxe_elink.c.

◆ MDIO_84833_TOP_CFG_FW_EEE

| #define MDIO_84833_TOP_CFG_FW_EEE 0x10b1 |

Definition at line 528 of file bxe_elink.c.

◆ MDIO_84833_TOP_CFG_FW_NO_EEE

| #define MDIO_84833_TOP_CFG_FW_NO_EEE 0x1f81 |

Definition at line 529 of file bxe_elink.c.

◆ MDIO_84833_TOP_CFG_FW_REV

| #define MDIO_84833_TOP_CFG_FW_REV 0x400f |

Definition at line 527 of file bxe_elink.c.

◆ MDIO_84833_TOP_CFG_XGPHY_STRAP1

| #define MDIO_84833_TOP_CFG_XGPHY_STRAP1 0x401a |

Definition at line 530 of file bxe_elink.c.

◆ MDIO_848xx_CMD_HDLR_COMMAND

| #define MDIO_848xx_CMD_HDLR_COMMAND (MDIO_848xx_TOP_CFG_SCRATCH_REG0) |

Definition at line 544 of file bxe_elink.c.

◆ MDIO_848xx_CMD_HDLR_DATA1

| #define MDIO_848xx_CMD_HDLR_DATA1 (MDIO_848xx_TOP_CFG_SCRATCH_REG27) |

Definition at line 546 of file bxe_elink.c.

◆ MDIO_848xx_CMD_HDLR_DATA2

| #define MDIO_848xx_CMD_HDLR_DATA2 (MDIO_848xx_TOP_CFG_SCRATCH_REG28) |

Definition at line 547 of file bxe_elink.c.

◆ MDIO_848xx_CMD_HDLR_DATA3

| #define MDIO_848xx_CMD_HDLR_DATA3 (MDIO_848xx_TOP_CFG_SCRATCH_REG29) |

Definition at line 548 of file bxe_elink.c.

◆ MDIO_848xx_CMD_HDLR_DATA4

| #define MDIO_848xx_CMD_HDLR_DATA4 (MDIO_848xx_TOP_CFG_SCRATCH_REG30) |

Definition at line 549 of file bxe_elink.c.

◆ MDIO_848xx_CMD_HDLR_DATA5

| #define MDIO_848xx_CMD_HDLR_DATA5 (MDIO_848xx_TOP_CFG_SCRATCH_REG31) |

Definition at line 550 of file bxe_elink.c.

◆ MDIO_848xx_CMD_HDLR_STATUS

| #define MDIO_848xx_CMD_HDLR_STATUS (MDIO_848xx_TOP_CFG_SCRATCH_REG26) |

Definition at line 545 of file bxe_elink.c.

◆ MDIO_848xx_TOP_CFG_SCRATCH_REG0

| #define MDIO_848xx_TOP_CFG_SCRATCH_REG0 0x4005 |

Definition at line 533 of file bxe_elink.c.

◆ MDIO_848xx_TOP_CFG_SCRATCH_REG1

| #define MDIO_848xx_TOP_CFG_SCRATCH_REG1 0x4006 |

Definition at line 534 of file bxe_elink.c.

◆ MDIO_848xx_TOP_CFG_SCRATCH_REG2

| #define MDIO_848xx_TOP_CFG_SCRATCH_REG2 0x4007 |

Definition at line 535 of file bxe_elink.c.

◆ MDIO_848xx_TOP_CFG_SCRATCH_REG26

| #define MDIO_848xx_TOP_CFG_SCRATCH_REG26 0x4037 |

Definition at line 538 of file bxe_elink.c.

◆ MDIO_848xx_TOP_CFG_SCRATCH_REG27

| #define MDIO_848xx_TOP_CFG_SCRATCH_REG27 0x4038 |

Definition at line 539 of file bxe_elink.c.

◆ MDIO_848xx_TOP_CFG_SCRATCH_REG28

| #define MDIO_848xx_TOP_CFG_SCRATCH_REG28 0x4039 |

Definition at line 540 of file bxe_elink.c.

◆ MDIO_848xx_TOP_CFG_SCRATCH_REG29

| #define MDIO_848xx_TOP_CFG_SCRATCH_REG29 0x403a |

Definition at line 541 of file bxe_elink.c.

◆ MDIO_848xx_TOP_CFG_SCRATCH_REG3

| #define MDIO_848xx_TOP_CFG_SCRATCH_REG3 0x4008 |

Definition at line 536 of file bxe_elink.c.

◆ MDIO_848xx_TOP_CFG_SCRATCH_REG30

| #define MDIO_848xx_TOP_CFG_SCRATCH_REG30 0x403b |

Definition at line 542 of file bxe_elink.c.

◆ MDIO_848xx_TOP_CFG_SCRATCH_REG31

| #define MDIO_848xx_TOP_CFG_SCRATCH_REG31 0x403c |

Definition at line 543 of file bxe_elink.c.

◆ MDIO_848xx_TOP_CFG_SCRATCH_REG4

| #define MDIO_848xx_TOP_CFG_SCRATCH_REG4 0x4009 |

Definition at line 537 of file bxe_elink.c.

◆ MDIO_AER_BLOCK_AER_REG

| #define MDIO_AER_BLOCK_AER_REG 0x1E |

Definition at line 296 of file bxe_elink.c.

◆ MDIO_AN_DEVAD

| #define MDIO_AN_DEVAD 0x7 |

Definition at line 454 of file bxe_elink.c.

◆ MDIO_AN_REG_1000T_STATUS

| #define MDIO_AN_REG_1000T_STATUS 0xffea |

Definition at line 477 of file bxe_elink.c.

◆ MDIO_AN_REG_8073_2_5G

| #define MDIO_AN_REG_8073_2_5G 0x8329 |

Definition at line 479 of file bxe_elink.c.

◆ MDIO_AN_REG_8073_BAM

| #define MDIO_AN_REG_8073_BAM 0x8350 |

Definition at line 480 of file bxe_elink.c.

◆ MDIO_AN_REG_8481_1000T_CTRL

| #define MDIO_AN_REG_8481_1000T_CTRL 0xffe9 |

Definition at line 491 of file bxe_elink.c.

◆ MDIO_AN_REG_8481_10GBASE_T_AN_CTRL

| #define MDIO_AN_REG_8481_10GBASE_T_AN_CTRL 0x0020 |

Definition at line 482 of file bxe_elink.c.

◆ MDIO_AN_REG_8481_1G_100T_EXT_CTRL

| #define MDIO_AN_REG_8481_1G_100T_EXT_CTRL 0xfff0 |

Definition at line 492 of file bxe_elink.c.

◆ MDIO_AN_REG_8481_AUX_CTRL

| #define MDIO_AN_REG_8481_AUX_CTRL 0xfff8 |

Definition at line 496 of file bxe_elink.c.

◆ MDIO_AN_REG_8481_EXPANSION_REG_ACCESS

| #define MDIO_AN_REG_8481_EXPANSION_REG_ACCESS 0xfff7 |

Definition at line 495 of file bxe_elink.c.

◆ MDIO_AN_REG_8481_EXPANSION_REG_RD_RW

| #define MDIO_AN_REG_8481_EXPANSION_REG_RD_RW 0xfff5 |

Definition at line 494 of file bxe_elink.c.

◆ MDIO_AN_REG_8481_LEGACY_AN_ADV

| #define MDIO_AN_REG_8481_LEGACY_AN_ADV 0xffe4 |

Definition at line 489 of file bxe_elink.c.

◆ MDIO_AN_REG_8481_LEGACY_AN_EXPANSION

| #define MDIO_AN_REG_8481_LEGACY_AN_EXPANSION 0xffe6 |

Definition at line 490 of file bxe_elink.c.

◆ MDIO_AN_REG_8481_LEGACY_MII_CTRL

| #define MDIO_AN_REG_8481_LEGACY_MII_CTRL 0xffe0 |

Definition at line 483 of file bxe_elink.c.

◆ MDIO_AN_REG_8481_LEGACY_MII_STATUS

| #define MDIO_AN_REG_8481_LEGACY_MII_STATUS 0xffe1 |

Definition at line 485 of file bxe_elink.c.

◆ MDIO_AN_REG_8481_LEGACY_SHADOW

| #define MDIO_AN_REG_8481_LEGACY_SHADOW 0xfffc |

Definition at line 497 of file bxe_elink.c.

◆ MDIO_AN_REG_8481_MII_CTRL_FORCE_1G

| #define MDIO_AN_REG_8481_MII_CTRL_FORCE_1G 0x40 |

Definition at line 484 of file bxe_elink.c.

◆ MDIO_AN_REG_848xx_ID_LSB

| #define MDIO_AN_REG_848xx_ID_LSB 0xffe3 |

Definition at line 488 of file bxe_elink.c.

◆ MDIO_AN_REG_848xx_ID_MSB

| #define MDIO_AN_REG_848xx_ID_MSB 0xffe2 |

Definition at line 486 of file bxe_elink.c.

◆ MDIO_AN_REG_8727_MISC_CTRL

| #define MDIO_AN_REG_8727_MISC_CTRL 0x8309 |

Definition at line 396 of file bxe_elink.c.

◆ MDIO_AN_REG_ADV

| #define MDIO_AN_REG_ADV 0x0011 |

Definition at line 464 of file bxe_elink.c.

◆ MDIO_AN_REG_ADV2

| #define MDIO_AN_REG_ADV2 0x0012 |

Definition at line 465 of file bxe_elink.c.

◆ MDIO_AN_REG_ADV_PAUSE

| #define MDIO_AN_REG_ADV_PAUSE 0x0010 |

Definition at line 459 of file bxe_elink.c.

◆ MDIO_AN_REG_ADV_PAUSE_ASYMMETRIC

| #define MDIO_AN_REG_ADV_PAUSE_ASYMMETRIC 0x0800 |

Definition at line 461 of file bxe_elink.c.

◆ MDIO_AN_REG_ADV_PAUSE_BOTH

| #define MDIO_AN_REG_ADV_PAUSE_BOTH 0x0C00 |

Definition at line 462 of file bxe_elink.c.

◆ MDIO_AN_REG_ADV_PAUSE_MASK

| #define MDIO_AN_REG_ADV_PAUSE_MASK 0x0C00 |

Definition at line 463 of file bxe_elink.c.

◆ MDIO_AN_REG_ADV_PAUSE_PAUSE

| #define MDIO_AN_REG_ADV_PAUSE_PAUSE 0x0400 |

Definition at line 460 of file bxe_elink.c.

◆ MDIO_AN_REG_CL37_AN

| #define MDIO_AN_REG_CL37_AN 0xffe0 |

Definition at line 474 of file bxe_elink.c.

◆ MDIO_AN_REG_CL37_CL73

| #define MDIO_AN_REG_CL37_CL73 0x8370 |

Definition at line 473 of file bxe_elink.c.

◆ MDIO_AN_REG_CL37_FC_LD

| #define MDIO_AN_REG_CL37_FC_LD 0xffe4 |

Definition at line 475 of file bxe_elink.c.

◆ MDIO_AN_REG_CL37_FC_LP

| #define MDIO_AN_REG_CL37_FC_LP 0xffe5 |

Definition at line 476 of file bxe_elink.c.

◆ MDIO_AN_REG_CTRL

| #define MDIO_AN_REG_CTRL 0x0000 |

Definition at line 456 of file bxe_elink.c.

◆ MDIO_AN_REG_EEE_ADV

| #define MDIO_AN_REG_EEE_ADV 0x003c |

Definition at line 469 of file bxe_elink.c.

◆ MDIO_AN_REG_LINK_STATUS

| #define MDIO_AN_REG_LINK_STATUS 0x8304 |

Definition at line 472 of file bxe_elink.c.

◆ MDIO_AN_REG_LP_AUTO_NEG

| #define MDIO_AN_REG_LP_AUTO_NEG 0x0013 |

Definition at line 466 of file bxe_elink.c.

◆ MDIO_AN_REG_LP_AUTO_NEG2

| #define MDIO_AN_REG_LP_AUTO_NEG2 0x0014 |

Definition at line 467 of file bxe_elink.c.

◆ MDIO_AN_REG_LP_EEE_ADV

| #define MDIO_AN_REG_LP_EEE_ADV 0x003d |

Definition at line 470 of file bxe_elink.c.

◆ MDIO_AN_REG_MASTER_STATUS

| #define MDIO_AN_REG_MASTER_STATUS 0x0021 |

Definition at line 468 of file bxe_elink.c.

◆ MDIO_AN_REG_STATUS

| #define MDIO_AN_REG_STATUS 0x0001 |

Definition at line 457 of file bxe_elink.c.

◆ MDIO_AN_REG_STATUS_AN_COMPLETE

| #define MDIO_AN_REG_STATUS_AN_COMPLETE 0x0020 |

Definition at line 458 of file bxe_elink.c.

◆ MDIO_BAM_NEXT_PAGE_MP5_NEXT_PAGE_CTRL

| #define MDIO_BAM_NEXT_PAGE_MP5_NEXT_PAGE_CTRL 0x10 |

Definition at line 278 of file bxe_elink.c.

◆ MDIO_BAM_NEXT_PAGE_MP5_NEXT_PAGE_CTRL_BAM_MODE

| #define MDIO_BAM_NEXT_PAGE_MP5_NEXT_PAGE_CTRL_BAM_MODE 0x0001 |

Definition at line 279 of file bxe_elink.c.

◆ MDIO_BAM_NEXT_PAGE_MP5_NEXT_PAGE_CTRL_TETON_AN

| #define MDIO_BAM_NEXT_PAGE_MP5_NEXT_PAGE_CTRL_TETON_AN 0x0002 |

Definition at line 280 of file bxe_elink.c.

◆ MDIO_BLOCK0_XGXS_CONTROL

| #define MDIO_BLOCK0_XGXS_CONTROL 0x10 |

Definition at line 141 of file bxe_elink.c.

◆ MDIO_BLOCK1_LANE_CTRL0

| #define MDIO_BLOCK1_LANE_CTRL0 0x15 |

Definition at line 144 of file bxe_elink.c.

◆ MDIO_BLOCK1_LANE_CTRL1

| #define MDIO_BLOCK1_LANE_CTRL1 0x16 |

Definition at line 145 of file bxe_elink.c.

◆ MDIO_BLOCK1_LANE_CTRL2

| #define MDIO_BLOCK1_LANE_CTRL2 0x17 |

Definition at line 146 of file bxe_elink.c.

◆ MDIO_BLOCK1_LANE_PRBS

| #define MDIO_BLOCK1_LANE_PRBS 0x19 |

Definition at line 147 of file bxe_elink.c.

◆ MDIO_CL73_IEEEB0_CL73_AN_CONTROL

| #define MDIO_CL73_IEEEB0_CL73_AN_CONTROL 0x0 |

Definition at line 41 of file bxe_elink.c.

◆ MDIO_CL73_IEEEB0_CL73_AN_CONTROL_AN_EN

| #define MDIO_CL73_IEEEB0_CL73_AN_CONTROL_AN_EN 0x1000 |

Definition at line 43 of file bxe_elink.c.

◆ MDIO_CL73_IEEEB0_CL73_AN_CONTROL_MAIN_RST

| #define MDIO_CL73_IEEEB0_CL73_AN_CONTROL_MAIN_RST 0x8000 |

Definition at line 44 of file bxe_elink.c.

◆ MDIO_CL73_IEEEB0_CL73_AN_CONTROL_RESTART_AN

| #define MDIO_CL73_IEEEB0_CL73_AN_CONTROL_RESTART_AN 0x0200 |

Definition at line 42 of file bxe_elink.c.

◆ MDIO_CL73_IEEEB1_AN_ADV1

| #define MDIO_CL73_IEEEB1_AN_ADV1 0x00 |

Definition at line 47 of file bxe_elink.c.

◆ MDIO_CL73_IEEEB1_AN_ADV1_ASYMMETRIC

| #define MDIO_CL73_IEEEB1_AN_ADV1_ASYMMETRIC 0x0800 |

Definition at line 49 of file bxe_elink.c.

◆ MDIO_CL73_IEEEB1_AN_ADV1_PAUSE

| #define MDIO_CL73_IEEEB1_AN_ADV1_PAUSE 0x0400 |

Definition at line 48 of file bxe_elink.c.

◆ MDIO_CL73_IEEEB1_AN_ADV1_PAUSE_BOTH

| #define MDIO_CL73_IEEEB1_AN_ADV1_PAUSE_BOTH 0x0C00 |

Definition at line 50 of file bxe_elink.c.

◆ MDIO_CL73_IEEEB1_AN_ADV1_PAUSE_MASK

| #define MDIO_CL73_IEEEB1_AN_ADV1_PAUSE_MASK 0x0C00 |

Definition at line 51 of file bxe_elink.c.

◆ MDIO_CL73_IEEEB1_AN_ADV2

| #define MDIO_CL73_IEEEB1_AN_ADV2 0x01 |

Definition at line 52 of file bxe_elink.c.

◆ MDIO_CL73_IEEEB1_AN_ADV2_ADVR_1000M

| #define MDIO_CL73_IEEEB1_AN_ADV2_ADVR_1000M 0x0000 |

Definition at line 53 of file bxe_elink.c.

◆ MDIO_CL73_IEEEB1_AN_ADV2_ADVR_1000M_KX

| #define MDIO_CL73_IEEEB1_AN_ADV2_ADVR_1000M_KX 0x0020 |

Definition at line 54 of file bxe_elink.c.

◆ MDIO_CL73_IEEEB1_AN_ADV2_ADVR_10G_KR

| #define MDIO_CL73_IEEEB1_AN_ADV2_ADVR_10G_KR 0x0080 |

Definition at line 56 of file bxe_elink.c.

◆ MDIO_CL73_IEEEB1_AN_ADV2_ADVR_10G_KX4

| #define MDIO_CL73_IEEEB1_AN_ADV2_ADVR_10G_KX4 0x0040 |

Definition at line 55 of file bxe_elink.c.

◆ MDIO_CL73_IEEEB1_AN_LP_ADV1

| #define MDIO_CL73_IEEEB1_AN_LP_ADV1 0x03 |

Definition at line 57 of file bxe_elink.c.

◆ MDIO_CL73_IEEEB1_AN_LP_ADV1_ASYMMETRIC

| #define MDIO_CL73_IEEEB1_AN_LP_ADV1_ASYMMETRIC 0x0800 |

Definition at line 59 of file bxe_elink.c.

◆ MDIO_CL73_IEEEB1_AN_LP_ADV1_PAUSE

| #define MDIO_CL73_IEEEB1_AN_LP_ADV1_PAUSE 0x0400 |

Definition at line 58 of file bxe_elink.c.

◆ MDIO_CL73_IEEEB1_AN_LP_ADV1_PAUSE_BOTH

| #define MDIO_CL73_IEEEB1_AN_LP_ADV1_PAUSE_BOTH 0x0C00 |

Definition at line 60 of file bxe_elink.c.

◆ MDIO_CL73_IEEEB1_AN_LP_ADV1_PAUSE_MASK

| #define MDIO_CL73_IEEEB1_AN_LP_ADV1_PAUSE_MASK 0x0C00 |

Definition at line 61 of file bxe_elink.c.

◆ MDIO_CL73_IEEEB1_AN_LP_ADV2

| #define MDIO_CL73_IEEEB1_AN_LP_ADV2 0x04 |

Definition at line 62 of file bxe_elink.c.

◆ MDIO_CL73_USERB0_CL73_BAM_CTRL1

| #define MDIO_CL73_USERB0_CL73_BAM_CTRL1 0x12 |

Definition at line 288 of file bxe_elink.c.

◆ MDIO_CL73_USERB0_CL73_BAM_CTRL1_BAM_EN

| #define MDIO_CL73_USERB0_CL73_BAM_CTRL1_BAM_EN 0x8000 |

Definition at line 289 of file bxe_elink.c.

◆ MDIO_CL73_USERB0_CL73_BAM_CTRL1_BAM_NP_AFTER_BP_EN

| #define MDIO_CL73_USERB0_CL73_BAM_CTRL1_BAM_NP_AFTER_BP_EN 0x2000 |

Definition at line 291 of file bxe_elink.c.

◆ MDIO_CL73_USERB0_CL73_BAM_CTRL1_BAM_STATION_MNGR_EN

| #define MDIO_CL73_USERB0_CL73_BAM_CTRL1_BAM_STATION_MNGR_EN 0x4000 |

Definition at line 290 of file bxe_elink.c.

◆ MDIO_CL73_USERB0_CL73_BAM_CTRL3

| #define MDIO_CL73_USERB0_CL73_BAM_CTRL3 0x14 |

Definition at line 292 of file bxe_elink.c.

◆ MDIO_CL73_USERB0_CL73_BAM_CTRL3_USE_CL73_HCD_MR

| #define MDIO_CL73_USERB0_CL73_BAM_CTRL3_USE_CL73_HCD_MR 0x0001 |

Definition at line 293 of file bxe_elink.c.

◆ MDIO_CL73_USERB0_CL73_UCTRL

| #define MDIO_CL73_USERB0_CL73_UCTRL 0x10 |

Definition at line 283 of file bxe_elink.c.

◆ MDIO_CL73_USERB0_CL73_UCTRL_USTAT1_MUXSEL

| #define MDIO_CL73_USERB0_CL73_UCTRL_USTAT1_MUXSEL 0x0002 |

Definition at line 284 of file bxe_elink.c.

◆ MDIO_CL73_USERB0_CL73_USTAT1

| #define MDIO_CL73_USERB0_CL73_USTAT1 0x11 |

Definition at line 285 of file bxe_elink.c.

◆ MDIO_CL73_USERB0_CL73_USTAT1_AN_GOOD_CHECK_BAM37

| #define MDIO_CL73_USERB0_CL73_USTAT1_AN_GOOD_CHECK_BAM37 0x0400 |

Definition at line 287 of file bxe_elink.c.

◆ MDIO_CL73_USERB0_CL73_USTAT1_LINK_STATUS_CHECK

| #define MDIO_CL73_USERB0_CL73_USTAT1_LINK_STATUS_CHECK 0x0100 |

Definition at line 286 of file bxe_elink.c.

◆ MDIO_COMBO_IEEE0_AUTO_NEG_ADV

| #define MDIO_COMBO_IEEE0_AUTO_NEG_ADV 0x14 |

Definition at line 312 of file bxe_elink.c.

◆ MDIO_COMBO_IEEE0_AUTO_NEG_ADV_FULL_DUPLEX

| #define MDIO_COMBO_IEEE0_AUTO_NEG_ADV_FULL_DUPLEX 0x0020 |

Definition at line 313 of file bxe_elink.c.

◆ MDIO_COMBO_IEEE0_AUTO_NEG_ADV_HALF_DUPLEX

| #define MDIO_COMBO_IEEE0_AUTO_NEG_ADV_HALF_DUPLEX 0x0040 |

Definition at line 314 of file bxe_elink.c.

◆ MDIO_COMBO_IEEE0_AUTO_NEG_ADV_NEXT_PAGE

| #define MDIO_COMBO_IEEE0_AUTO_NEG_ADV_NEXT_PAGE 0x8000 |

Definition at line 320 of file bxe_elink.c.

◆ MDIO_COMBO_IEEE0_AUTO_NEG_ADV_PAUSE_ASYMMETRIC

| #define MDIO_COMBO_IEEE0_AUTO_NEG_ADV_PAUSE_ASYMMETRIC 0x0100 |

Definition at line 318 of file bxe_elink.c.

◆ MDIO_COMBO_IEEE0_AUTO_NEG_ADV_PAUSE_BOTH

| #define MDIO_COMBO_IEEE0_AUTO_NEG_ADV_PAUSE_BOTH 0x0180 |

Definition at line 319 of file bxe_elink.c.

◆ MDIO_COMBO_IEEE0_AUTO_NEG_ADV_PAUSE_MASK

| #define MDIO_COMBO_IEEE0_AUTO_NEG_ADV_PAUSE_MASK 0x0180 |

Definition at line 315 of file bxe_elink.c.

◆ MDIO_COMBO_IEEE0_AUTO_NEG_ADV_PAUSE_NONE

| #define MDIO_COMBO_IEEE0_AUTO_NEG_ADV_PAUSE_NONE 0x0000 |

Definition at line 316 of file bxe_elink.c.

◆ MDIO_COMBO_IEEE0_AUTO_NEG_ADV_PAUSE_SYMMETRIC

| #define MDIO_COMBO_IEEE0_AUTO_NEG_ADV_PAUSE_SYMMETRIC 0x0080 |

Definition at line 317 of file bxe_elink.c.

◆ MDIO_COMBO_IEEE0_AUTO_NEG_LINK_PARTNER_ABILITY1

| #define MDIO_COMBO_IEEE0_AUTO_NEG_LINK_PARTNER_ABILITY1 0x15 |

Definition at line 321 of file bxe_elink.c.

◆ MDIO_COMBO_IEEE0_AUTO_NEG_LINK_PARTNER_ABILITY1_ACK

| #define MDIO_COMBO_IEEE0_AUTO_NEG_LINK_PARTNER_ABILITY1_ACK 0x4000 |

Definition at line 323 of file bxe_elink.c.

◆ MDIO_COMBO_IEEE0_AUTO_NEG_LINK_PARTNER_ABILITY1_FULL_DUP_CAP

| #define MDIO_COMBO_IEEE0_AUTO_NEG_LINK_PARTNER_ABILITY1_FULL_DUP_CAP 0x0020 |

Definition at line 328 of file bxe_elink.c.

◆ MDIO_COMBO_IEEE0_AUTO_NEG_LINK_PARTNER_ABILITY1_HALF_DUP_CAP

| #define MDIO_COMBO_IEEE0_AUTO_NEG_LINK_PARTNER_ABILITY1_HALF_DUP_CAP 0x0040 |

Definition at line 327 of file bxe_elink.c.

◆ MDIO_COMBO_IEEE0_AUTO_NEG_LINK_PARTNER_ABILITY1_NEXT_PAGE

| #define MDIO_COMBO_IEEE0_AUTO_NEG_LINK_PARTNER_ABILITY1_NEXT_PAGE 0x8000 |

Definition at line 322 of file bxe_elink.c.

◆ MDIO_COMBO_IEEE0_AUTO_NEG_LINK_PARTNER_ABILITY1_PAUSE_BOTH

| #define MDIO_COMBO_IEEE0_AUTO_NEG_LINK_PARTNER_ABILITY1_PAUSE_BOTH 0x0180 |

Definition at line 326 of file bxe_elink.c.

◆ MDIO_COMBO_IEEE0_AUTO_NEG_LINK_PARTNER_ABILITY1_PAUSE_MASK

| #define MDIO_COMBO_IEEE0_AUTO_NEG_LINK_PARTNER_ABILITY1_PAUSE_MASK 0x0180 |

Definition at line 324 of file bxe_elink.c.

◆ MDIO_COMBO_IEEE0_AUTO_NEG_LINK_PARTNER_ABILITY1_PAUSE_NONE

| #define MDIO_COMBO_IEEE0_AUTO_NEG_LINK_PARTNER_ABILITY1_PAUSE_NONE 0x0000 |

Definition at line 325 of file bxe_elink.c.

◆ MDIO_COMBO_IEEE0_AUTO_NEG_LINK_PARTNER_ABILITY1_SGMII_MODE

| #define MDIO_COMBO_IEEE0_AUTO_NEG_LINK_PARTNER_ABILITY1_SGMII_MODE 0x0001 |

Definition at line 332 of file bxe_elink.c.

◆ MDIO_COMBO_IEEE0_MII_CONTROL

| #define MDIO_COMBO_IEEE0_MII_CONTROL 0x10 |

Definition at line 299 of file bxe_elink.c.

◆ MDIO_COMBO_IEEE0_MII_STATUS

| #define MDIO_COMBO_IEEE0_MII_STATUS 0x11 |

Definition at line 309 of file bxe_elink.c.

◆ MDIO_COMBO_IEEE0_MII_STATUS_AUTONEG_COMPLETE

| #define MDIO_COMBO_IEEE0_MII_STATUS_AUTONEG_COMPLETE 0x0020 |

Definition at line 311 of file bxe_elink.c.

◆ MDIO_COMBO_IEEE0_MII_STATUS_LINK_PASS

| #define MDIO_COMBO_IEEE0_MII_STATUS_LINK_PASS 0x0004 |

Definition at line 310 of file bxe_elink.c.

◆ MDIO_COMBO_IEEO_MII_CONTROL_AN_EN

| #define MDIO_COMBO_IEEO_MII_CONTROL_AN_EN 0x1000 |

Definition at line 306 of file bxe_elink.c.

◆ MDIO_COMBO_IEEO_MII_CONTROL_FULL_DUPLEX

| #define MDIO_COMBO_IEEO_MII_CONTROL_FULL_DUPLEX 0x0100 |

Definition at line 304 of file bxe_elink.c.

◆ MDIO_COMBO_IEEO_MII_CONTROL_LOOPBACK

| #define MDIO_COMBO_IEEO_MII_CONTROL_LOOPBACK 0x4000 |

Definition at line 307 of file bxe_elink.c.

◆ MDIO_COMBO_IEEO_MII_CONTROL_MAN_SGMII_SP_10

| #define MDIO_COMBO_IEEO_MII_CONTROL_MAN_SGMII_SP_10 0x0000 |

Definition at line 301 of file bxe_elink.c.

◆ MDIO_COMBO_IEEO_MII_CONTROL_MAN_SGMII_SP_100

| #define MDIO_COMBO_IEEO_MII_CONTROL_MAN_SGMII_SP_100 0x2000 |

Definition at line 302 of file bxe_elink.c.

◆ MDIO_COMBO_IEEO_MII_CONTROL_MAN_SGMII_SP_1000

| #define MDIO_COMBO_IEEO_MII_CONTROL_MAN_SGMII_SP_1000 0x0040 |

Definition at line 303 of file bxe_elink.c.

◆ MDIO_COMBO_IEEO_MII_CONTROL_MAN_SGMII_SP_MASK

| #define MDIO_COMBO_IEEO_MII_CONTROL_MAN_SGMII_SP_MASK 0x2040 |

Definition at line 300 of file bxe_elink.c.

◆ MDIO_COMBO_IEEO_MII_CONTROL_RESET

| #define MDIO_COMBO_IEEO_MII_CONTROL_RESET 0x8000 |

Definition at line 308 of file bxe_elink.c.

◆ MDIO_COMBO_IEEO_MII_CONTROL_RESTART_AN

| #define MDIO_COMBO_IEEO_MII_CONTROL_RESTART_AN 0x0200 |

Definition at line 305 of file bxe_elink.c.

◆ MDIO_CTL_DEVAD

| #define MDIO_CTL_DEVAD 0x1e |

Definition at line 500 of file bxe_elink.c.

◆ MDIO_CTL_REG_84823_CTRL_MAC_XFI

| #define MDIO_CTL_REG_84823_CTRL_MAC_XFI 0x0008 |

Definition at line 504 of file bxe_elink.c.

◆ MDIO_CTL_REG_84823_MEDIA

| #define MDIO_CTL_REG_84823_MEDIA 0x401a |

Definition at line 501 of file bxe_elink.c.

◆ MDIO_CTL_REG_84823_MEDIA_COPPER_CORE_DOWN

| #define MDIO_CTL_REG_84823_MEDIA_COPPER_CORE_DOWN 0x0080 |

Definition at line 513 of file bxe_elink.c.

◆ MDIO_CTL_REG_84823_MEDIA_FIBER_1G

| #define MDIO_CTL_REG_84823_MEDIA_FIBER_1G 0x1000 |

Definition at line 517 of file bxe_elink.c.

◆ MDIO_CTL_REG_84823_MEDIA_LINE_MASK

| #define MDIO_CTL_REG_84823_MEDIA_LINE_MASK 0x0060 |

Definition at line 507 of file bxe_elink.c.

◆ MDIO_CTL_REG_84823_MEDIA_LINE_XAUI_L

| #define MDIO_CTL_REG_84823_MEDIA_LINE_XAUI_L 0x0020 |

Definition at line 508 of file bxe_elink.c.

◆ MDIO_CTL_REG_84823_MEDIA_LINE_XFI

| #define MDIO_CTL_REG_84823_MEDIA_LINE_XFI 0x0040 |

Definition at line 509 of file bxe_elink.c.

◆ MDIO_CTL_REG_84823_MEDIA_MAC_MASK

| #define MDIO_CTL_REG_84823_MEDIA_MAC_MASK 0x0018 |

Definition at line 502 of file bxe_elink.c.

◆ MDIO_CTL_REG_84823_MEDIA_MAC_XAUI_M

| #define MDIO_CTL_REG_84823_MEDIA_MAC_XAUI_M 0x0010 |

Definition at line 505 of file bxe_elink.c.

◆ MDIO_CTL_REG_84823_MEDIA_PRIORITY_COPPER

| #define MDIO_CTL_REG_84823_MEDIA_PRIORITY_COPPER 0x0000 |

Definition at line 515 of file bxe_elink.c.

◆ MDIO_CTL_REG_84823_MEDIA_PRIORITY_FIBER

| #define MDIO_CTL_REG_84823_MEDIA_PRIORITY_FIBER 0x0100 |

Definition at line 516 of file bxe_elink.c.

◆ MDIO_CTL_REG_84823_MEDIA_PRIORITY_MASK

| #define MDIO_CTL_REG_84823_MEDIA_PRIORITY_MASK 0x0100 |

Definition at line 514 of file bxe_elink.c.

◆ MDIO_CTL_REG_84823_USER_CTRL_CMS

| #define MDIO_CTL_REG_84823_USER_CTRL_CMS 0x0080 |

Definition at line 519 of file bxe_elink.c.

◆ MDIO_CTL_REG_84823_USER_CTRL_REG

| #define MDIO_CTL_REG_84823_USER_CTRL_REG 0x4005 |

Definition at line 518 of file bxe_elink.c.

◆ MDIO_GP_STATUS_TOP_AN_STATUS1

| #define MDIO_GP_STATUS_TOP_AN_STATUS1 0x1B |

Definition at line 161 of file bxe_elink.c.

◆ MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_100M

| #define MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_100M 0x0100 |

Definition at line 172 of file bxe_elink.c.

◆ MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_10G_CX4

| #define MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_10G_CX4 0x0700 |

Definition at line 178 of file bxe_elink.c.

◆ MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_10G_HIG

| #define MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_10G_HIG 0x0600 |

Definition at line 177 of file bxe_elink.c.

◆ MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_10G_KR

| #define MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_10G_KR 0x0F00 |

Definition at line 186 of file bxe_elink.c.

◆ MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_10G_KX4

| #define MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_10G_KX4 0x0E00 |

Definition at line 185 of file bxe_elink.c.

◆ MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_10G_SFI

| #define MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_10G_SFI 0x1F00 |

Definition at line 189 of file bxe_elink.c.

◆ MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_10G_XFI

| #define MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_10G_XFI 0x1B00 |

Definition at line 187 of file bxe_elink.c.

◆ MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_10M

| #define MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_10M 0x0000 |

Definition at line 171 of file bxe_elink.c.

◆ MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_12_5G

| #define MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_12_5G 0x0900 |

Definition at line 180 of file bxe_elink.c.

◆ MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_12G_HIG

| #define MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_12G_HIG 0x0800 |

Definition at line 179 of file bxe_elink.c.

◆ MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_13G

| #define MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_13G 0x0A00 |

Definition at line 181 of file bxe_elink.c.

◆ MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_15G

| #define MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_15G 0x0B00 |

Definition at line 182 of file bxe_elink.c.

◆ MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_16G

| #define MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_16G 0x0C00 |

Definition at line 183 of file bxe_elink.c.

◆ MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_1G

| #define MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_1G 0x0200 |

Definition at line 173 of file bxe_elink.c.

◆ MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_1G_KX

| #define MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_1G_KX 0x0D00 |

Definition at line 184 of file bxe_elink.c.

◆ MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_20G_DXGXS

| #define MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_20G_DXGXS 0x1E00 |

Definition at line 188 of file bxe_elink.c.

◆ MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_20G_KR2

| #define MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_20G_KR2 0x3900 |

Definition at line 190 of file bxe_elink.c.

◆ MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_2_5G

| #define MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_2_5G 0x0300 |

Definition at line 174 of file bxe_elink.c.

◆ MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_5G

| #define MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_5G 0x0400 |

Definition at line 175 of file bxe_elink.c.

◆ MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_6G

| #define MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_6G 0x0500 |

Definition at line 176 of file bxe_elink.c.

◆ MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_MASK

| #define MDIO_GP_STATUS_TOP_AN_STATUS1_ACTUAL_SPEED_MASK 0x3f00 |

Definition at line 170 of file bxe_elink.c.

◆ MDIO_GP_STATUS_TOP_AN_STATUS1_CL37_AUTONEG_COMPLETE

| #define MDIO_GP_STATUS_TOP_AN_STATUS1_CL37_AUTONEG_COMPLETE 0x0002 |

Definition at line 163 of file bxe_elink.c.

◆ MDIO_GP_STATUS_TOP_AN_STATUS1_CL73_AUTONEG_COMPLETE

| #define MDIO_GP_STATUS_TOP_AN_STATUS1_CL73_AUTONEG_COMPLETE 0x0001 |

Definition at line 162 of file bxe_elink.c.

◆ MDIO_GP_STATUS_TOP_AN_STATUS1_CL73_LP_NP_BAM_ABLE

| #define MDIO_GP_STATUS_TOP_AN_STATUS1_CL73_LP_NP_BAM_ABLE 0x0020 |

Definition at line 167 of file bxe_elink.c.

◆ MDIO_GP_STATUS_TOP_AN_STATUS1_CL73_MR_LP_NP_AN_ABLE

| #define MDIO_GP_STATUS_TOP_AN_STATUS1_CL73_MR_LP_NP_AN_ABLE 0x0010 |

Definition at line 166 of file bxe_elink.c.

◆ MDIO_GP_STATUS_TOP_AN_STATUS1_DUPLEX_STATUS

| #define MDIO_GP_STATUS_TOP_AN_STATUS1_DUPLEX_STATUS 0x0008 |

Definition at line 165 of file bxe_elink.c.

◆ MDIO_GP_STATUS_TOP_AN_STATUS1_LINK_STATUS

| #define MDIO_GP_STATUS_TOP_AN_STATUS1_LINK_STATUS 0x0004 |

Definition at line 164 of file bxe_elink.c.

◆ MDIO_GP_STATUS_TOP_AN_STATUS1_PAUSE_RSOLUTION_RXSIDE

| #define MDIO_GP_STATUS_TOP_AN_STATUS1_PAUSE_RSOLUTION_RXSIDE 0x0080 |

Definition at line 169 of file bxe_elink.c.