#include "ixgbe_type.h"

Go to the source code of this file.

Macro Definition Documentation

◆ IXGBE_CS4223_SKU_ID

| #define IXGBE_CS4223_SKU_ID 0x0010 /* Quad port */ |

Definition at line 98 of file ixgbe_phy.h.

◆ IXGBE_CS4227

| #define IXGBE_CS4227 0xBE /* CS4227 address */ |

Definition at line 92 of file ixgbe_phy.h.

◆ IXGBE_CS4227_CHECK_DELAY

| #define IXGBE_CS4227_CHECK_DELAY 30 /* milliseconds */ |

Definition at line 117 of file ixgbe_phy.h.

◆ IXGBE_CS4227_EDC_MODE_CX1

| #define IXGBE_CS4227_EDC_MODE_CX1 0x0002 |

Definition at line 112 of file ixgbe_phy.h.

◆ IXGBE_CS4227_EDC_MODE_DIAG

| #define IXGBE_CS4227_EDC_MODE_DIAG 0x0008 |

Definition at line 114 of file ixgbe_phy.h.

◆ IXGBE_CS4227_EDC_MODE_SR

| #define IXGBE_CS4227_EDC_MODE_SR 0x0004 |

Definition at line 113 of file ixgbe_phy.h.

◆ IXGBE_CS4227_EEPROM_LOAD_OK

| #define IXGBE_CS4227_EEPROM_LOAD_OK 0x0001 |

Definition at line 109 of file ixgbe_phy.h.

◆ IXGBE_CS4227_EEPROM_STATUS

| #define IXGBE_CS4227_EEPROM_STATUS 0x5001 |

Definition at line 108 of file ixgbe_phy.h.

◆ IXGBE_CS4227_EFUSE_PDF_SKU

| #define IXGBE_CS4227_EFUSE_PDF_SKU 0x19F |

Definition at line 97 of file ixgbe_phy.h.

◆ IXGBE_CS4227_EFUSE_STATUS

| #define IXGBE_CS4227_EFUSE_STATUS 0x0181 |

Definition at line 103 of file ixgbe_phy.h.

◆ IXGBE_CS4227_GLOBAL_ID_LSB

| #define IXGBE_CS4227_GLOBAL_ID_LSB 0 |

Definition at line 93 of file ixgbe_phy.h.

◆ IXGBE_CS4227_GLOBAL_ID_MSB

| #define IXGBE_CS4227_GLOBAL_ID_MSB 1 |

Definition at line 94 of file ixgbe_phy.h.

◆ IXGBE_CS4227_GLOBAL_ID_VALUE

| #define IXGBE_CS4227_GLOBAL_ID_VALUE 0x03E5 |

Definition at line 96 of file ixgbe_phy.h.

◆ IXGBE_CS4227_HOST_SPARE22_MSB

| #define IXGBE_CS4227_HOST_SPARE22_MSB 0x1AAD /* Reg to program speed */ |

Definition at line 106 of file ixgbe_phy.h.

◆ IXGBE_CS4227_HOST_SPARE24_LSB

| #define IXGBE_CS4227_HOST_SPARE24_LSB 0x1AB0 /* Reg to program EDC */ |

Definition at line 107 of file ixgbe_phy.h.

◆ IXGBE_CS4227_LINE_SPARE22_MSB

| #define IXGBE_CS4227_LINE_SPARE22_MSB 0x12AD /* Reg to program speed */ |

Definition at line 104 of file ixgbe_phy.h.

◆ IXGBE_CS4227_LINE_SPARE24_LSB

| #define IXGBE_CS4227_LINE_SPARE24_LSB 0x12B0 /* Reg to program EDC */ |

Definition at line 105 of file ixgbe_phy.h.

◆ IXGBE_CS4227_RESET_COMPLETE

| #define IXGBE_CS4227_RESET_COMPLETE 0x5AA5 |

Definition at line 101 of file ixgbe_phy.h.

◆ IXGBE_CS4227_RESET_DELAY

| #define IXGBE_CS4227_RESET_DELAY 450 /* milliseconds */ |

Definition at line 116 of file ixgbe_phy.h.

◆ IXGBE_CS4227_RESET_HOLD

| #define IXGBE_CS4227_RESET_HOLD 500 /* microseconds */ |

Definition at line 115 of file ixgbe_phy.h.

◆ IXGBE_CS4227_RESET_PENDING

| #define IXGBE_CS4227_RESET_PENDING 0x1357 |

Definition at line 100 of file ixgbe_phy.h.

◆ IXGBE_CS4227_RETRIES

| #define IXGBE_CS4227_RETRIES 15 |

Definition at line 102 of file ixgbe_phy.h.

◆ IXGBE_CS4227_SCRATCH

| #define IXGBE_CS4227_SCRATCH 2 |

Definition at line 95 of file ixgbe_phy.h.

◆ IXGBE_CS4227_SKU_ID

| #define IXGBE_CS4227_SKU_ID 0x0014 /* Dual port */ |

Definition at line 99 of file ixgbe_phy.h.

◆ IXGBE_CS4227_SPEED_10G

| #define IXGBE_CS4227_SPEED_10G 0 |

Definition at line 111 of file ixgbe_phy.h.

◆ IXGBE_CS4227_SPEED_1G

| #define IXGBE_CS4227_SPEED_1G 0x8000 |

Definition at line 110 of file ixgbe_phy.h.

◆ IXGBE_I2C_EEPROM_BANK_LEN

| #define IXGBE_I2C_EEPROM_BANK_LEN 0xFF |

Definition at line 42 of file ixgbe_phy.h.

◆ IXGBE_I2C_EEPROM_DEV_ADDR

| #define IXGBE_I2C_EEPROM_DEV_ADDR 0xA0 |

Definition at line 40 of file ixgbe_phy.h.

◆ IXGBE_I2C_EEPROM_DEV_ADDR2

| #define IXGBE_I2C_EEPROM_DEV_ADDR2 0xA2 |

Definition at line 41 of file ixgbe_phy.h.

◆ IXGBE_I2C_EEPROM_READ_MASK

| #define IXGBE_I2C_EEPROM_READ_MASK 0x100 |

Definition at line 85 of file ixgbe_phy.h.

◆ IXGBE_I2C_EEPROM_STATUS_FAIL

| #define IXGBE_I2C_EEPROM_STATUS_FAIL 0x2 |

Definition at line 89 of file ixgbe_phy.h.

◆ IXGBE_I2C_EEPROM_STATUS_IN_PROGRESS

| #define IXGBE_I2C_EEPROM_STATUS_IN_PROGRESS 0x3 |

Definition at line 90 of file ixgbe_phy.h.

◆ IXGBE_I2C_EEPROM_STATUS_MASK

| #define IXGBE_I2C_EEPROM_STATUS_MASK 0x3 |

Definition at line 86 of file ixgbe_phy.h.

◆ IXGBE_I2C_EEPROM_STATUS_NO_OPERATION

| #define IXGBE_I2C_EEPROM_STATUS_NO_OPERATION 0x0 |

Definition at line 87 of file ixgbe_phy.h.

◆ IXGBE_I2C_EEPROM_STATUS_PASS

| #define IXGBE_I2C_EEPROM_STATUS_PASS 0x1 |

Definition at line 88 of file ixgbe_phy.h.

◆ IXGBE_I2C_T_BUF

| #define IXGBE_I2C_T_BUF 5 |

Definition at line 148 of file ixgbe_phy.h.

◆ IXGBE_I2C_T_FALL

| #define IXGBE_I2C_T_FALL 1 |

Definition at line 146 of file ixgbe_phy.h.

◆ IXGBE_I2C_T_HD_DATA

| #define IXGBE_I2C_T_HD_DATA 5 |

Definition at line 143 of file ixgbe_phy.h.

◆ IXGBE_I2C_T_HD_STA

| #define IXGBE_I2C_T_HD_STA 4 |

Definition at line 139 of file ixgbe_phy.h.

◆ IXGBE_I2C_T_HIGH

| #define IXGBE_I2C_T_HIGH 4 |

Definition at line 141 of file ixgbe_phy.h.

◆ IXGBE_I2C_T_LOW

| #define IXGBE_I2C_T_LOW 5 |

Definition at line 140 of file ixgbe_phy.h.

◆ IXGBE_I2C_T_RISE

| #define IXGBE_I2C_T_RISE 1 |

Definition at line 145 of file ixgbe_phy.h.

◆ IXGBE_I2C_T_SU_DATA

| #define IXGBE_I2C_T_SU_DATA 1 |

Definition at line 144 of file ixgbe_phy.h.

◆ IXGBE_I2C_T_SU_STA

| #define IXGBE_I2C_T_SU_STA 5 |

Definition at line 142 of file ixgbe_phy.h.

◆ IXGBE_I2C_T_SU_STO

| #define IXGBE_I2C_T_SU_STO 4 |

Definition at line 147 of file ixgbe_phy.h.

◆ IXGBE_PE

| #define IXGBE_PE 0xE0 /* Port expander address */ |

Definition at line 118 of file ixgbe_phy.h.

◆ IXGBE_PE_BIT1

| #define IXGBE_PE_BIT1 (1 << 1) |

Definition at line 121 of file ixgbe_phy.h.

◆ IXGBE_PE_CONFIG

| #define IXGBE_PE_CONFIG 3 /* Config register offset */ |

Definition at line 120 of file ixgbe_phy.h.

◆ IXGBE_PE_OUTPUT

| #define IXGBE_PE_OUTPUT 1 /* Output register offset */ |

Definition at line 119 of file ixgbe_phy.h.

◆ IXGBE_SFF_10GBASELR_CAPABLE

| #define IXGBE_SFF_10GBASELR_CAPABLE 0x20 |

Definition at line 76 of file ixgbe_phy.h.

◆ IXGBE_SFF_10GBASESR_CAPABLE

| #define IXGBE_SFF_10GBASESR_CAPABLE 0x10 |

Definition at line 75 of file ixgbe_phy.h.

◆ IXGBE_SFF_10GBE_COMP_CODES

| #define IXGBE_SFF_10GBE_COMP_CODES 0x3 |

Definition at line 51 of file ixgbe_phy.h.

◆ IXGBE_SFF_1GBASELX_CAPABLE

| #define IXGBE_SFF_1GBASELX_CAPABLE 0x2 |

Definition at line 73 of file ixgbe_phy.h.

◆ IXGBE_SFF_1GBASESX_CAPABLE

| #define IXGBE_SFF_1GBASESX_CAPABLE 0x1 |

Definition at line 72 of file ixgbe_phy.h.

◆ IXGBE_SFF_1GBASET_CAPABLE

| #define IXGBE_SFF_1GBASET_CAPABLE 0x8 |

Definition at line 74 of file ixgbe_phy.h.

◆ IXGBE_SFF_1GBE_COMP_CODES

| #define IXGBE_SFF_1GBE_COMP_CODES 0x6 |

Definition at line 50 of file ixgbe_phy.h.

◆ IXGBE_SFF_ADDRESSING_MODE

| #define IXGBE_SFF_ADDRESSING_MODE 0x4 |

Definition at line 80 of file ixgbe_phy.h.

◆ IXGBE_SFF_CABLE_SPEC_COMP

| #define IXGBE_SFF_CABLE_SPEC_COMP 0x3C |

Definition at line 53 of file ixgbe_phy.h.

◆ IXGBE_SFF_CABLE_TECHNOLOGY

| #define IXGBE_SFF_CABLE_TECHNOLOGY 0x8 |

Definition at line 52 of file ixgbe_phy.h.

◆ IXGBE_SFF_DA_ACTIVE_CABLE

| #define IXGBE_SFF_DA_ACTIVE_CABLE 0x8 |

Definition at line 70 of file ixgbe_phy.h.

◆ IXGBE_SFF_DA_PASSIVE_CABLE

| #define IXGBE_SFF_DA_PASSIVE_CABLE 0x4 |

Definition at line 69 of file ixgbe_phy.h.

◆ IXGBE_SFF_DA_SPEC_ACTIVE_LIMITING

| #define IXGBE_SFF_DA_SPEC_ACTIVE_LIMITING 0x4 |

Definition at line 71 of file ixgbe_phy.h.

◆ IXGBE_SFF_IDENTIFIER

| #define IXGBE_SFF_IDENTIFIER 0x0 |

Definition at line 45 of file ixgbe_phy.h.

◆ IXGBE_SFF_IDENTIFIER_QSFP_PLUS

| #define IXGBE_SFF_IDENTIFIER_QSFP_PLUS 0xD |

Definition at line 58 of file ixgbe_phy.h.

◆ IXGBE_SFF_IDENTIFIER_SFP

| #define IXGBE_SFF_IDENTIFIER_SFP 0x3 |

Definition at line 46 of file ixgbe_phy.h.

◆ IXGBE_SFF_QSFP_10GBE_COMP

| #define IXGBE_SFF_QSFP_10GBE_COMP 0x83 |

Definition at line 63 of file ixgbe_phy.h.

◆ IXGBE_SFF_QSFP_1GBE_COMP

| #define IXGBE_SFF_QSFP_1GBE_COMP 0x86 |

Definition at line 64 of file ixgbe_phy.h.

◆ IXGBE_SFF_QSFP_CABLE_LENGTH

| #define IXGBE_SFF_QSFP_CABLE_LENGTH 0x92 |

Definition at line 65 of file ixgbe_phy.h.

◆ IXGBE_SFF_QSFP_CONNECTOR

| #define IXGBE_SFF_QSFP_CONNECTOR 0x82 |

Definition at line 62 of file ixgbe_phy.h.

◆ IXGBE_SFF_QSFP_CONNECTOR_NOT_SEPARABLE

| #define IXGBE_SFF_QSFP_CONNECTOR_NOT_SEPARABLE 0x23 |

Definition at line 83 of file ixgbe_phy.h.

◆ IXGBE_SFF_QSFP_DA_ACTIVE_CABLE

| #define IXGBE_SFF_QSFP_DA_ACTIVE_CABLE 0x1 |

Definition at line 81 of file ixgbe_phy.h.

◆ IXGBE_SFF_QSFP_DA_PASSIVE_CABLE

| #define IXGBE_SFF_QSFP_DA_PASSIVE_CABLE 0x8 |

Definition at line 82 of file ixgbe_phy.h.

◆ IXGBE_SFF_QSFP_DEVICE_TECH

| #define IXGBE_SFF_QSFP_DEVICE_TECH 0x93 |

Definition at line 66 of file ixgbe_phy.h.

◆ IXGBE_SFF_QSFP_TRANSMITER_850NM_VCSEL

| #define IXGBE_SFF_QSFP_TRANSMITER_850NM_VCSEL 0x0 |

Definition at line 84 of file ixgbe_phy.h.

◆ IXGBE_SFF_QSFP_VENDOR_OUI_BYTE0

| #define IXGBE_SFF_QSFP_VENDOR_OUI_BYTE0 0xA5 |

Definition at line 59 of file ixgbe_phy.h.

◆ IXGBE_SFF_QSFP_VENDOR_OUI_BYTE1

| #define IXGBE_SFF_QSFP_VENDOR_OUI_BYTE1 0xA6 |

Definition at line 60 of file ixgbe_phy.h.

◆ IXGBE_SFF_QSFP_VENDOR_OUI_BYTE2

| #define IXGBE_SFF_QSFP_VENDOR_OUI_BYTE2 0xA7 |

Definition at line 61 of file ixgbe_phy.h.

◆ IXGBE_SFF_SFF_8472_COMP

| #define IXGBE_SFF_SFF_8472_COMP 0x5E |

Definition at line 55 of file ixgbe_phy.h.

◆ IXGBE_SFF_SFF_8472_ESCB

| #define IXGBE_SFF_SFF_8472_ESCB 0x76 |

Definition at line 57 of file ixgbe_phy.h.

◆ IXGBE_SFF_SFF_8472_OSCB

| #define IXGBE_SFF_SFF_8472_OSCB 0x6E |

Definition at line 56 of file ixgbe_phy.h.

◆ IXGBE_SFF_SFF_8472_SWAP

| #define IXGBE_SFF_SFF_8472_SWAP 0x5C |

Definition at line 54 of file ixgbe_phy.h.

◆ IXGBE_SFF_SFF_8472_UNSUP

| #define IXGBE_SFF_SFF_8472_UNSUP 0x00 |

Definition at line 156 of file ixgbe_phy.h.

◆ IXGBE_SFF_SOFT_RS_SELECT_10G

| #define IXGBE_SFF_SOFT_RS_SELECT_10G 0x8 |

Definition at line 78 of file ixgbe_phy.h.

◆ IXGBE_SFF_SOFT_RS_SELECT_1G

| #define IXGBE_SFF_SOFT_RS_SELECT_1G 0x0 |

Definition at line 79 of file ixgbe_phy.h.

◆ IXGBE_SFF_SOFT_RS_SELECT_MASK

| #define IXGBE_SFF_SOFT_RS_SELECT_MASK 0x8 |

Definition at line 77 of file ixgbe_phy.h.

◆ IXGBE_SFF_VENDOR_OUI_AVAGO

| #define IXGBE_SFF_VENDOR_OUI_AVAGO 0x00176A00 |

Definition at line 135 of file ixgbe_phy.h.

◆ IXGBE_SFF_VENDOR_OUI_BYTE0

| #define IXGBE_SFF_VENDOR_OUI_BYTE0 0x25 |

Definition at line 47 of file ixgbe_phy.h.

◆ IXGBE_SFF_VENDOR_OUI_BYTE0_SHIFT

| #define IXGBE_SFF_VENDOR_OUI_BYTE0_SHIFT 24 |

Definition at line 128 of file ixgbe_phy.h.

◆ IXGBE_SFF_VENDOR_OUI_BYTE1

| #define IXGBE_SFF_VENDOR_OUI_BYTE1 0x26 |

Definition at line 48 of file ixgbe_phy.h.

◆ IXGBE_SFF_VENDOR_OUI_BYTE1_SHIFT

| #define IXGBE_SFF_VENDOR_OUI_BYTE1_SHIFT 16 |

Definition at line 129 of file ixgbe_phy.h.

◆ IXGBE_SFF_VENDOR_OUI_BYTE2

| #define IXGBE_SFF_VENDOR_OUI_BYTE2 0x27 |

Definition at line 49 of file ixgbe_phy.h.

◆ IXGBE_SFF_VENDOR_OUI_BYTE2_SHIFT

| #define IXGBE_SFF_VENDOR_OUI_BYTE2_SHIFT 8 |

Definition at line 130 of file ixgbe_phy.h.

◆ IXGBE_SFF_VENDOR_OUI_FTL

| #define IXGBE_SFF_VENDOR_OUI_FTL 0x00906500 |

Definition at line 134 of file ixgbe_phy.h.

◆ IXGBE_SFF_VENDOR_OUI_INTEL

| #define IXGBE_SFF_VENDOR_OUI_INTEL 0x001B2100 |

Definition at line 136 of file ixgbe_phy.h.

◆ IXGBE_SFF_VENDOR_OUI_TYCO

| #define IXGBE_SFF_VENDOR_OUI_TYCO 0x00407600 |

Definition at line 133 of file ixgbe_phy.h.

◆ IXGBE_SFP_DETECT_RETRIES

| #define IXGBE_SFP_DETECT_RETRIES 10 |

Definition at line 150 of file ixgbe_phy.h.

◆ IXGBE_TAF_ASM_PAUSE

| #define IXGBE_TAF_ASM_PAUSE 0x800 |

Definition at line 125 of file ixgbe_phy.h.

◆ IXGBE_TAF_SYM_PAUSE

| #define IXGBE_TAF_SYM_PAUSE 0x400 |

Definition at line 124 of file ixgbe_phy.h.

◆ IXGBE_TN_LASI_STATUS_REG

| #define IXGBE_TN_LASI_STATUS_REG 0x9005 |

Definition at line 152 of file ixgbe_phy.h.

◆ IXGBE_TN_LASI_STATUS_TEMP_ALARM

| #define IXGBE_TN_LASI_STATUS_TEMP_ALARM 0x0008 |

Definition at line 153 of file ixgbe_phy.h.

Function Documentation

◆ ixgbe_check_phy_link_tnx()

| s32 ixgbe_check_phy_link_tnx | ( | struct ixgbe_hw * | hw, |

| ixgbe_link_speed * | speed, | ||

| bool * | link_up | ||

| ) |

ixgbe_check_phy_link_tnx - Determine link and speed status @hw: pointer to hardware structure @speed: current link speed @link_up: true is link is up, false otherwise

Reads the VS1 register to determine if link is up and the current speed for the PHY.

Definition at line 995 of file ixgbe_phy.c.

References DEBUGFUNC, IXGBE_LINK_SPEED_10GB_FULL, IXGBE_LINK_SPEED_1GB_FULL, IXGBE_MDIO_VENDOR_SPECIFIC_1_DEV_TYPE, IXGBE_MDIO_VENDOR_SPECIFIC_1_LINK_STATUS, IXGBE_MDIO_VENDOR_SPECIFIC_1_SPEED_STATUS, IXGBE_MDIO_VENDOR_SPECIFIC_1_STATUS, IXGBE_SUCCESS, ixgbe_phy_info::ops, ixgbe_hw::phy, phy_speed, ixgbe_phy_operations::read_reg, and usec_delay.

Referenced by ixgbe_init_phy_ops_82598(), and ixgbe_init_phy_ops_82599().

◆ ixgbe_check_reset_blocked()

ixgbe_check_reset_blocked - check status of MNG FW veto bit @hw: pointer to the hardware structure

This function checks the MMNGC.MNG_VETO bit to see if there are any constraints on link from manageability. For MAC's that don't have this bit just return faluse since the link can not be blocked via this method.

Definition at line 375 of file ixgbe_phy.c.

References DEBUGFUNC, ERROR_REPORT1, IXGBE_ERROR_SOFTWARE, ixgbe_mac_82598EB, IXGBE_MMNGC, IXGBE_MMNGC_MNG_VETO, IXGBE_READ_REG, ixgbe_hw::mac, and ixgbe_mac_info::type.

Referenced by ixgbe_disable_tx_laser_multispeed_fiber(), ixgbe_enter_lplu_t_x550em(), ixgbe_flap_tx_laser_multispeed_fiber(), ixgbe_reset_phy_fw(), ixgbe_reset_phy_generic(), ixgbe_reset_phy_nl(), ixgbe_restart_auto_neg(), ixgbe_set_copper_phy_power(), ixgbe_setup_fw_link(), ixgbe_setup_kr_x550em(), and prot_autoc_write_82599().

◆ ixgbe_get_copper_link_capabilities_generic()

| s32 ixgbe_get_copper_link_capabilities_generic | ( | struct ixgbe_hw * | hw, |

| ixgbe_link_speed * | speed, | ||

| bool * | autoneg | ||

| ) |

ixgbe_get_copper_link_capabilities_generic - Determines link capabilities @hw: pointer to hardware structure @speed: pointer to link speed @autoneg: boolean auto-negotiation value

Definition at line 970 of file ixgbe_phy.c.

References DEBUGFUNC, ixgbe_get_copper_speeds_supported(), IXGBE_SUCCESS, ixgbe_hw::phy, and ixgbe_phy_info::speeds_supported.

Referenced by ixgbe_get_link_capabilities_X540(), ixgbe_init_ops_X540(), ixgbe_init_phy_ops_82598(), ixgbe_init_phy_ops_82599(), ixgbe_setup_phy_link_generic(), and ixgbe_setup_phy_link_tnx().

◆ ixgbe_get_phy_firmware_version_generic()

ixgbe_get_phy_firmware_version_generic - Gets the PHY Firmware Version @hw: pointer to hardware structure @firmware_version: pointer to the PHY Firmware Version

Definition at line 1127 of file ixgbe_phy.c.

References AQ_FW_REV, DEBUGFUNC, IXGBE_MDIO_VENDOR_SPECIFIC_1_DEV_TYPE, ixgbe_phy_info::ops, ixgbe_hw::phy, and ixgbe_phy_operations::read_reg.

Referenced by ixgbe_init_phy_ops_generic().

◆ ixgbe_get_phy_firmware_version_tnx()

ixgbe_get_phy_firmware_version_tnx - Gets the PHY Firmware Version @hw: pointer to hardware structure @firmware_version: pointer to the PHY Firmware Version

Definition at line 1108 of file ixgbe_phy.c.

References DEBUGFUNC, IXGBE_MDIO_VENDOR_SPECIFIC_1_DEV_TYPE, ixgbe_phy_info::ops, ixgbe_hw::phy, ixgbe_phy_operations::read_reg, and TNX_FW_REV.

Referenced by ixgbe_init_phy_ops_82598(), and ixgbe_init_phy_ops_82599().

◆ ixgbe_get_phy_id()

ixgbe_get_phy_id - Get the phy type @hw: pointer to hardware structure

Definition at line 425 of file ixgbe_phy.c.

References DEBUGFUNC, DEBUGOUT2, ixgbe_phy_info::id, IXGBE_MDIO_PHY_ID_HIGH, IXGBE_MDIO_PHY_ID_LOW, IXGBE_MDIO_PMA_PMD_DEV_TYPE, IXGBE_PHY_REVISION_MASK, IXGBE_SUCCESS, ixgbe_phy_info::ops, ixgbe_hw::phy, ixgbe_phy_operations::read_reg, and ixgbe_phy_info::revision.

Referenced by ixgbe_probe_phy().

◆ ixgbe_get_phy_type_from_id()

| enum ixgbe_phy_type ixgbe_get_phy_type_from_id | ( | u32 | phy_id | ) |

ixgbe_get_phy_type_from_id - Get the phy type @phy_id: PHY ID information

Definition at line 456 of file ixgbe_phy.c.

References ATH_PHY_ID, DEBUGFUNC, IXGBE_M88E1500_E_PHY_ID, IXGBE_M88E1543_E_PHY_ID, ixgbe_phy_aq, ixgbe_phy_ext_1g_t, ixgbe_phy_nl, ixgbe_phy_qt, ixgbe_phy_tn, ixgbe_phy_unknown, ixgbe_phy_x550em_ext_t, QT2022_PHY_ID, TN1010_PHY_ID, X540_PHY_ID, X550_PHY_ID2, X550_PHY_ID3, X557_PHY_ID, and X557_PHY_ID2.

Referenced by ixgbe_probe_phy().

◆ ixgbe_get_sfp_init_sequence_offsets()

| s32 ixgbe_get_sfp_init_sequence_offsets | ( | struct ixgbe_hw * | hw, |

| u16 * | list_offset, | ||

| u16 * | data_offset | ||

| ) |

ixgbe_get_sfp_init_sequence_offsets - Provides offset of PHY init sequence @hw: pointer to hardware structure @list_offset: offset to the SFP ID list @data_offset: offset to the SFP data block

Checks the MAC's EEPROM to see if it supports a given SFP+ module type, if so it returns the offsets to the phy init sequence block.

Definition at line 1832 of file ixgbe_phy.c.

References DEBUGFUNC, DEBUGOUT, ixgbe_hw::device_id, ixgbe_hw::eeprom, ERROR_REPORT2, IXGBE_DEV_ID_82598_SR_DUAL_PORT_EM, IXGBE_ERR_PHY, IXGBE_ERR_SFP_NO_INIT_SEQ_PRESENT, IXGBE_ERR_SFP_NOT_PRESENT, IXGBE_ERR_SFP_NOT_SUPPORTED, IXGBE_ERROR_INVALID_STATE, IXGBE_PHY_INIT_END_NL, IXGBE_PHY_INIT_OFFSET_NL, ixgbe_sfp_type_1g_cu_core0, ixgbe_sfp_type_1g_cu_core1, ixgbe_sfp_type_1g_lx_core0, ixgbe_sfp_type_1g_lx_core1, ixgbe_sfp_type_1g_sx_core0, ixgbe_sfp_type_1g_sx_core1, ixgbe_sfp_type_da_act_lmt_core0, ixgbe_sfp_type_da_act_lmt_core1, ixgbe_sfp_type_da_cu, ixgbe_sfp_type_not_present, ixgbe_sfp_type_srlr_core0, ixgbe_sfp_type_srlr_core1, ixgbe_sfp_type_unknown, IXGBE_SUCCESS, ixgbe_eeprom_info::ops, ixgbe_hw::phy, ixgbe_eeprom_operations::read, and ixgbe_phy_info::sfp_type.

Referenced by ixgbe_init_phy_ops_82598(), ixgbe_reset_phy_nl(), and ixgbe_setup_sfp_modules_82599().

◆ ixgbe_get_supported_phy_sfp_layer_generic()

ixgbe_get_supported_phy_sfp_layer_generic - Returns physical layer type @hw: pointer to hardware structure

Determines physical layer capabilities of the current SFP.

Definition at line 1574 of file ixgbe_phy.c.

References DEBUGFUNC, ixgbe_phy_operations::identify_sfp, ixgbe_phy_qsfp_active_unknown, ixgbe_phy_qsfp_intel, ixgbe_phy_qsfp_passive_unknown, ixgbe_phy_qsfp_unknown, ixgbe_phy_sfp_active_unknown, ixgbe_phy_sfp_avago, ixgbe_phy_sfp_ftl, ixgbe_phy_sfp_ftl_active, ixgbe_phy_sfp_intel, ixgbe_phy_sfp_passive_tyco, ixgbe_phy_sfp_passive_unknown, ixgbe_phy_sfp_unknown, IXGBE_PHYSICAL_LAYER_1000BASE_SX, IXGBE_PHYSICAL_LAYER_1000BASE_T, IXGBE_PHYSICAL_LAYER_10GBASE_LR, IXGBE_PHYSICAL_LAYER_10GBASE_SR, IXGBE_PHYSICAL_LAYER_SFP_ACTIVE_DA, IXGBE_PHYSICAL_LAYER_SFP_PLUS_CU, IXGBE_PHYSICAL_LAYER_UNKNOWN, IXGBE_SFF_10GBASELR_CAPABLE, IXGBE_SFF_10GBASESR_CAPABLE, IXGBE_SFF_10GBE_COMP_CODES, IXGBE_SFF_1GBASESX_CAPABLE, IXGBE_SFF_1GBASET_CAPABLE, IXGBE_SFF_1GBE_COMP_CODES, IXGBE_SFF_QSFP_10GBE_COMP, ixgbe_sfp_type_not_present, ixgbe_phy_info::ops, ixgbe_hw::phy, ixgbe_phy_operations::read_i2c_eeprom, ixgbe_phy_info::sfp_type, and ixgbe_phy_info::type.

Referenced by ixgbe_get_supported_physical_layer_82599(), and ixgbe_get_supported_physical_layer_X550em().

◆ ixgbe_i2c_bus_clear()

| void ixgbe_i2c_bus_clear | ( | struct ixgbe_hw * | hw | ) |

ixgbe_i2c_bus_clear - Clears the I2C bus @hw: pointer to hardware structure

Clears the I2C bus by sending nine clock pulses. Used when data line is stuck low.

Definition at line 2605 of file ixgbe_phy.c.

References DEBUGFUNC, ixgbe_i2c_start(), ixgbe_i2c_stop(), IXGBE_I2C_T_HIGH, IXGBE_I2C_T_LOW, IXGBE_I2CCTL_BY_MAC, ixgbe_lower_i2c_clk(), ixgbe_raise_i2c_clk(), IXGBE_READ_REG, ixgbe_set_i2c_data(), and usec_delay.

Referenced by ixgbe_init_phy_ops_generic(), ixgbe_read_i2c_byte_generic_int(), ixgbe_read_i2c_combined_generic_int(), ixgbe_write_i2c_byte_generic_int(), and ixgbe_write_i2c_combined_generic_int().

◆ ixgbe_identify_module_generic()

ixgbe_identify_module_generic - Identifies module type @hw: pointer to hardware structure

Determines HW type and calls appropriate function.

Definition at line 1263 of file ixgbe_phy.c.

References DEBUGFUNC, ixgbe_mac_operations::get_media_type, IXGBE_ERR_SFP_NOT_PRESENT, ixgbe_identify_qsfp_module_generic(), ixgbe_identify_sfp_module_generic(), ixgbe_media_type_fiber, ixgbe_media_type_fiber_qsfp, ixgbe_sfp_type_not_present, ixgbe_hw::mac, ixgbe_mac_info::ops, ixgbe_hw::phy, and ixgbe_phy_info::sfp_type.

Referenced by ixgbe_identify_phy_82599(), ixgbe_identify_sfp_module_X550em(), and ixgbe_init_phy_ops_generic().

◆ ixgbe_identify_phy_generic()

ixgbe_identify_phy_generic - Get physical layer module @hw: pointer to hardware structure

Determines the physical layer module found on the current adapter.

Definition at line 322 of file ixgbe_phy.c.

References ixgbe_phy_info::addr, ixgbe_hw::bus, DEBUGFUNC, IXGBE_ERR_PHY_ADDR_INVALID, IXGBE_GSSR_PHY0_SM, IXGBE_GSSR_PHY1_SM, IXGBE_MAX_PHY_ADDR, IXGBE_NW_MNG_IF_SEL_MDIO_PHY_ADD, IXGBE_NW_MNG_IF_SEL_MDIO_PHY_ADD_SHIFT, ixgbe_phy_unknown, ixgbe_probe_phy(), IXGBE_SUCCESS, ixgbe_bus_info::lan_id, ixgbe_phy_info::nw_mng_if_sel, ixgbe_hw::phy, ixgbe_phy_info::phy_semaphore_mask, and ixgbe_phy_info::type.

Referenced by ixgbe_identify_phy_82599(), ixgbe_identify_phy_x550em(), ixgbe_init_phy_ops_generic(), and ixgbe_reset_phy_generic().

◆ ixgbe_identify_qsfp_module_generic()

ixgbe_identify_qsfp_module_generic - Identifies QSFP modules @hw: pointer to hardware structure

Searches for and identifies the QSFP module and assigns appropriate PHY type

Definition at line 1636 of file ixgbe_phy.c.

References ixgbe_hw::allow_unsupported_sfp, ixgbe_hw::bus, DEBUGFUNC, DEBUGOUT, EWARN, ixgbe_mac_operations::get_media_type, ixgbe_phy_info::id, IXGBE_DEVICE_CAPS_ALLOW_ANY_SFP, IXGBE_ERR_PHY_ADDR_INVALID, IXGBE_ERR_SFP_NOT_PRESENT, IXGBE_ERR_SFP_NOT_SUPPORTED, ixgbe_get_device_caps(), ixgbe_media_type_fiber_qsfp, ixgbe_phy_qsfp_active_unknown, ixgbe_phy_qsfp_intel, ixgbe_phy_qsfp_passive_unknown, ixgbe_phy_qsfp_unknown, ixgbe_phy_sfp_unsupported, ixgbe_phy_unknown, IXGBE_SFF_10GBASELR_CAPABLE, IXGBE_SFF_10GBASESR_CAPABLE, IXGBE_SFF_1GBASELX_CAPABLE, IXGBE_SFF_1GBASESX_CAPABLE, IXGBE_SFF_IDENTIFIER, IXGBE_SFF_IDENTIFIER_QSFP_PLUS, IXGBE_SFF_QSFP_10GBE_COMP, IXGBE_SFF_QSFP_1GBE_COMP, IXGBE_SFF_QSFP_CABLE_LENGTH, IXGBE_SFF_QSFP_CONNECTOR, IXGBE_SFF_QSFP_CONNECTOR_NOT_SEPARABLE, IXGBE_SFF_QSFP_DA_ACTIVE_CABLE, IXGBE_SFF_QSFP_DA_PASSIVE_CABLE, IXGBE_SFF_QSFP_DEVICE_TECH, IXGBE_SFF_QSFP_TRANSMITER_850NM_VCSEL, IXGBE_SFF_QSFP_VENDOR_OUI_BYTE0, IXGBE_SFF_QSFP_VENDOR_OUI_BYTE1, IXGBE_SFF_QSFP_VENDOR_OUI_BYTE2, IXGBE_SFF_VENDOR_OUI_BYTE0_SHIFT, IXGBE_SFF_VENDOR_OUI_BYTE1_SHIFT, IXGBE_SFF_VENDOR_OUI_BYTE2_SHIFT, IXGBE_SFF_VENDOR_OUI_INTEL, ixgbe_sfp_type_da_act_lmt_core0, ixgbe_sfp_type_da_act_lmt_core1, ixgbe_sfp_type_da_cu_core0, ixgbe_sfp_type_da_cu_core1, ixgbe_sfp_type_not_present, ixgbe_sfp_type_srlr_core0, ixgbe_sfp_type_srlr_core1, IXGBE_SUCCESS, ixgbe_bus_info::lan_id, ixgbe_hw::mac, ixgbe_phy_info::multispeed_fiber, ixgbe_mac_info::ops, ixgbe_phy_info::ops, ixgbe_hw::phy, ixgbe_phy_operations::read_i2c_eeprom, ixgbe_mac_operations::set_lan_id, ixgbe_phy_info::sfp_setup_needed, ixgbe_phy_info::sfp_type, and ixgbe_phy_info::type.

Referenced by ixgbe_identify_module_generic().

◆ ixgbe_identify_sfp_module_generic()

ixgbe_identify_sfp_module_generic - Identifies SFP modules @hw: pointer to hardware structure

Searches for and identifies the SFP module and assigns appropriate PHY type.

Definition at line 1293 of file ixgbe_phy.c.

References ixgbe_hw::allow_unsupported_sfp, ixgbe_hw::bus, DEBUGFUNC, DEBUGOUT, EWARN, ixgbe_mac_operations::get_media_type, ixgbe_phy_info::id, IXGBE_DEVICE_CAPS_ALLOW_ANY_SFP, IXGBE_ERR_PHY_ADDR_INVALID, IXGBE_ERR_SFP_NOT_PRESENT, IXGBE_ERR_SFP_NOT_SUPPORTED, ixgbe_get_device_caps(), ixgbe_mac_82598EB, ixgbe_media_type_fiber, ixgbe_phy_nl, ixgbe_phy_sfp_active_unknown, ixgbe_phy_sfp_avago, ixgbe_phy_sfp_ftl, ixgbe_phy_sfp_ftl_active, ixgbe_phy_sfp_intel, ixgbe_phy_sfp_passive_tyco, ixgbe_phy_sfp_passive_unknown, ixgbe_phy_sfp_unknown, ixgbe_phy_sfp_unsupported, ixgbe_phy_unknown, IXGBE_SFF_10GBASELR_CAPABLE, IXGBE_SFF_10GBASESR_CAPABLE, IXGBE_SFF_10GBE_COMP_CODES, IXGBE_SFF_1GBASELX_CAPABLE, IXGBE_SFF_1GBASESX_CAPABLE, IXGBE_SFF_1GBASET_CAPABLE, IXGBE_SFF_1GBE_COMP_CODES, IXGBE_SFF_CABLE_SPEC_COMP, IXGBE_SFF_CABLE_TECHNOLOGY, IXGBE_SFF_DA_ACTIVE_CABLE, IXGBE_SFF_DA_PASSIVE_CABLE, IXGBE_SFF_DA_SPEC_ACTIVE_LIMITING, IXGBE_SFF_IDENTIFIER, IXGBE_SFF_IDENTIFIER_SFP, IXGBE_SFF_VENDOR_OUI_AVAGO, IXGBE_SFF_VENDOR_OUI_BYTE0, IXGBE_SFF_VENDOR_OUI_BYTE0_SHIFT, IXGBE_SFF_VENDOR_OUI_BYTE1, IXGBE_SFF_VENDOR_OUI_BYTE1_SHIFT, IXGBE_SFF_VENDOR_OUI_BYTE2, IXGBE_SFF_VENDOR_OUI_BYTE2_SHIFT, IXGBE_SFF_VENDOR_OUI_FTL, IXGBE_SFF_VENDOR_OUI_INTEL, IXGBE_SFF_VENDOR_OUI_TYCO, ixgbe_sfp_type_1g_cu_core0, ixgbe_sfp_type_1g_cu_core1, ixgbe_sfp_type_1g_lx_core0, ixgbe_sfp_type_1g_lx_core1, ixgbe_sfp_type_1g_sx_core0, ixgbe_sfp_type_1g_sx_core1, ixgbe_sfp_type_da_act_lmt_core0, ixgbe_sfp_type_da_act_lmt_core1, ixgbe_sfp_type_da_cu, ixgbe_sfp_type_da_cu_core0, ixgbe_sfp_type_da_cu_core1, ixgbe_sfp_type_lr, ixgbe_sfp_type_not_present, ixgbe_sfp_type_sr, ixgbe_sfp_type_srlr_core0, ixgbe_sfp_type_srlr_core1, ixgbe_sfp_type_unknown, IXGBE_SUCCESS, ixgbe_bus_info::lan_id, ixgbe_hw::mac, ixgbe_phy_info::multispeed_fiber, ixgbe_mac_info::ops, ixgbe_phy_info::ops, ixgbe_hw::phy, ixgbe_phy_operations::read_i2c_eeprom, ixgbe_mac_operations::set_lan_id, ixgbe_phy_info::sfp_setup_needed, ixgbe_phy_info::sfp_type, ixgbe_mac_info::type, and ixgbe_phy_info::type.

Referenced by ixgbe_identify_module_generic().

◆ ixgbe_init_phy_ops_generic()

ixgbe_init_phy_ops_generic - Inits PHY function ptrs @hw: pointer to the hardware structure

Initialize the function pointers.

Definition at line 248 of file ixgbe_phy.c.

References ixgbe_phy_operations::check_link, ixgbe_phy_operations::check_overtemp, DEBUGFUNC, ixgbe_phy_operations::get_firmware_version, ixgbe_phy_operations::i2c_bus_clear, ixgbe_phy_operations::identify, ixgbe_phy_operations::identify_sfp, ixgbe_get_phy_firmware_version_generic(), ixgbe_i2c_bus_clear(), ixgbe_identify_module_generic(), ixgbe_identify_phy_generic(), ixgbe_read_i2c_byte_generic(), ixgbe_read_i2c_byte_generic_unlocked(), ixgbe_read_i2c_eeprom_generic(), ixgbe_read_i2c_sff8472_generic(), ixgbe_read_phy_reg_generic(), ixgbe_read_phy_reg_mdi(), ixgbe_reset_phy_generic(), ixgbe_setup_phy_link_generic(), ixgbe_setup_phy_link_speed_generic(), ixgbe_sfp_type_unknown, IXGBE_SUCCESS, ixgbe_tn_check_overtemp(), ixgbe_write_i2c_byte_generic(), ixgbe_write_i2c_byte_generic_unlocked(), ixgbe_write_i2c_eeprom_generic(), ixgbe_write_phy_reg_generic(), ixgbe_write_phy_reg_mdi(), ixgbe_phy_info::ops, ixgbe_hw::phy, ixgbe_phy_operations::read_i2c_byte, ixgbe_phy_operations::read_i2c_byte_unlocked, ixgbe_phy_operations::read_i2c_eeprom, ixgbe_phy_operations::read_i2c_sff8472, ixgbe_phy_operations::read_reg, ixgbe_phy_operations::read_reg_mdi, ixgbe_phy_operations::reset, ixgbe_phy_operations::setup_link, ixgbe_phy_operations::setup_link_speed, ixgbe_phy_info::sfp_type, ixgbe_phy_operations::write_i2c_byte, ixgbe_phy_operations::write_i2c_byte_unlocked, ixgbe_phy_operations::write_i2c_eeprom, ixgbe_phy_operations::write_reg, and ixgbe_phy_operations::write_reg_mdi.

Referenced by ixgbe_init_ops_82598(), ixgbe_init_ops_82599(), and ixgbe_init_ops_X540().

◆ ixgbe_read_i2c_byte_generic()

ixgbe_read_i2c_byte_generic - Reads 8 bit word over I2C @hw: pointer to hardware structure @byte_offset: byte offset to read @dev_addr: address to read from @data: value read

Performs byte read operation to SFP module's EEPROM over I2C interface at a specified device address.

Definition at line 2084 of file ixgbe_phy.c.

References ixgbe_read_i2c_byte_generic_int().

Referenced by ixgbe_init_phy_ops_generic(), and ixgbe_read_i2c_byte_82599().

◆ ixgbe_read_i2c_byte_generic_unlocked()

| s32 ixgbe_read_i2c_byte_generic_unlocked | ( | struct ixgbe_hw * | hw, |

| u8 | byte_offset, | ||

| u8 | dev_addr, | ||

| u8 * | data | ||

| ) |

ixgbe_read_i2c_byte_generic_unlocked - Reads 8 bit word over I2C @hw: pointer to hardware structure @byte_offset: byte offset to read @dev_addr: address to read from @data: value read

Performs byte read operation to SFP module's EEPROM over I2C interface at a specified device address.

Definition at line 2101 of file ixgbe_phy.c.

References ixgbe_read_i2c_byte_generic_int().

Referenced by ixgbe_init_phy_ops_generic().

◆ ixgbe_read_i2c_combined_generic_int()

| s32 ixgbe_read_i2c_combined_generic_int | ( | struct ixgbe_hw * | hw, |

| u8 | addr, | ||

| u16 | reg, | ||

| u16 * | val, | ||

| bool | lock | ||

| ) |

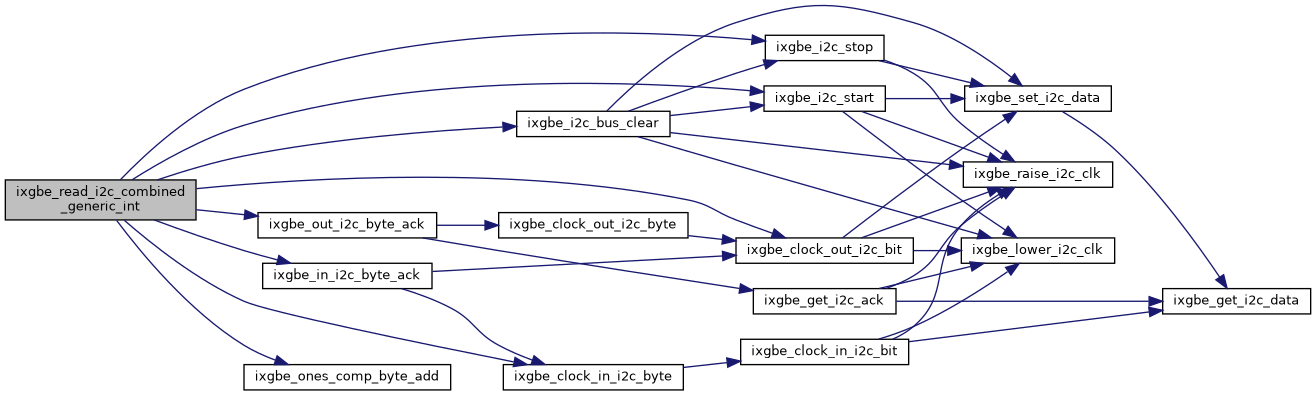

ixgbe_read_i2c_combined_generic_int - Perform I2C read combined operation @hw: pointer to the hardware structure @addr: I2C bus address to read from @reg: I2C device register to read from @val: pointer to location to receive read value @lock: true if to take and release semaphore

Returns an error code on error.

Definition at line 110 of file ixgbe_phy.c.

References ixgbe_mac_operations::acquire_swfw_sync, DEBUGOUT, ixgbe_clock_in_i2c_byte(), ixgbe_clock_out_i2c_bit(), IXGBE_ERR_I2C, IXGBE_ERR_SWFW_SYNC, ixgbe_i2c_bus_clear(), ixgbe_i2c_start(), ixgbe_i2c_stop(), ixgbe_in_i2c_byte_ack(), ixgbe_ones_comp_byte_add(), ixgbe_out_i2c_byte_ack(), ixgbe_hw::mac, ixgbe_mac_info::ops, ixgbe_hw::phy, ixgbe_phy_info::phy_semaphore_mask, and ixgbe_mac_operations::release_swfw_sync.

Referenced by ixgbe_read_i2c_combined_generic(), and ixgbe_read_i2c_combined_generic_unlocked().

◆ ixgbe_read_i2c_eeprom_generic()

ixgbe_read_i2c_eeprom_generic - Reads 8 bit EEPROM word over I2C interface @hw: pointer to hardware structure @byte_offset: EEPROM byte offset to read @eeprom_data: value read

Performs byte read operation to SFP module's EEPROM over I2C interface.

Definition at line 1926 of file ixgbe_phy.c.

References DEBUGFUNC, IXGBE_I2C_EEPROM_DEV_ADDR, ixgbe_phy_info::ops, ixgbe_hw::phy, and ixgbe_phy_operations::read_i2c_byte.

Referenced by ixgbe_init_phy_ops_generic().

◆ ixgbe_read_phy_reg_generic()

| s32 ixgbe_read_phy_reg_generic | ( | struct ixgbe_hw * | hw, |

| u32 | reg_addr, | ||

| u32 | device_type, | ||

| u16 * | phy_data | ||

| ) |

ixgbe_read_phy_reg_generic - Reads a value from a specified PHY register using the SWFW lock - this function is needed in most cases @hw: pointer to hardware structure @reg_addr: 32 bit address of PHY register to read @device_type: 5 bit device type @phy_data: Pointer to read data from PHY register

Definition at line 681 of file ixgbe_phy.c.

References ixgbe_mac_operations::acquire_swfw_sync, DEBUGFUNC, IXGBE_ERR_SWFW_SYNC, ixgbe_hw::mac, ixgbe_mac_info::ops, ixgbe_phy_info::ops, ixgbe_hw::phy, ixgbe_phy_info::phy_semaphore_mask, ixgbe_phy_operations::read_reg_mdi, and ixgbe_mac_operations::release_swfw_sync.

Referenced by ixgbe_init_phy_ops_generic().

◆ ixgbe_read_phy_reg_mdi()

ixgbe_read_phy_mdi - Reads a value from a specified PHY register without the SWFW lock @hw: pointer to hardware structure @reg_addr: 32 bit address of PHY register to read @device_type: 5 bit device type @phy_data: Pointer to read data from PHY register

Definition at line 599 of file ixgbe_phy.c.

References ixgbe_phy_info::addr, DEBUGOUT, ERROR_REPORT1, IXGBE_ERR_PHY, IXGBE_ERROR_POLLING, IXGBE_MDIO_COMMAND_TIMEOUT, IXGBE_MSCA, IXGBE_MSCA_ADDR_CYCLE, IXGBE_MSCA_DEV_TYPE_SHIFT, IXGBE_MSCA_MDI_COMMAND, IXGBE_MSCA_NP_ADDR_SHIFT, IXGBE_MSCA_PHY_ADDR_SHIFT, IXGBE_MSCA_READ, IXGBE_MSRWD, IXGBE_MSRWD_READ_DATA_SHIFT, IXGBE_READ_REG, IXGBE_SUCCESS, IXGBE_WRITE_REG, ixgbe_hw::phy, and usec_delay.

Referenced by ixgbe_init_phy_ops_generic().

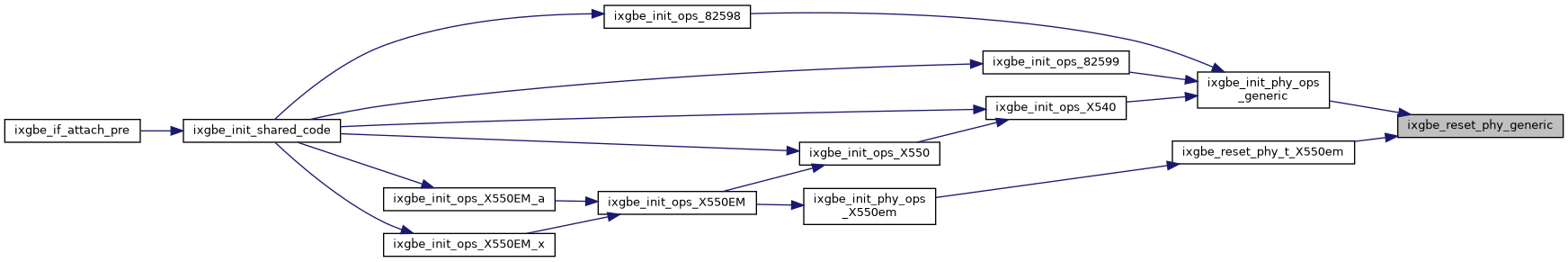

◆ ixgbe_reset_phy_generic()

ixgbe_reset_phy_generic - Performs a PHY reset @hw: pointer to hardware structure

Definition at line 496 of file ixgbe_phy.c.

References ixgbe_phy_operations::check_overtemp, DEBUGFUNC, ERROR_REPORT1, ixgbe_check_reset_blocked(), IXGBE_ERR_OVERTEMP, IXGBE_ERR_RESET_FAILED, IXGBE_ERROR_POLLING, ixgbe_identify_phy_generic(), IXGBE_MDIO_PHY_XS_CONTROL, IXGBE_MDIO_PHY_XS_DEV_TYPE, IXGBE_MDIO_PHY_XS_RESET, IXGBE_MDIO_PMA_PMD_DEV_TYPE, IXGBE_MDIO_TX_VENDOR_ALARMS_3, IXGBE_MDIO_TX_VENDOR_ALARMS_3_RST_MASK, ixgbe_phy_none, ixgbe_phy_unknown, ixgbe_phy_x550em_ext_t, IXGBE_SUCCESS, msec_delay, ixgbe_phy_info::ops, ixgbe_hw::phy, ixgbe_phy_operations::read_reg, ixgbe_phy_info::reset_if_overtemp, ixgbe_phy_info::type, usec_delay, and ixgbe_phy_operations::write_reg.

Referenced by ixgbe_init_phy_ops_generic(), and ixgbe_reset_phy_t_X550em().

◆ ixgbe_reset_phy_nl()

ixgbe_reset_phy_nl - Performs a PHY reset @hw: pointer to hardware structure

Definition at line 1145 of file ixgbe_phy.c.

References DEBUGFUNC, DEBUGOUT, DEBUGOUT1, DEBUGOUT2, ixgbe_hw::eeprom, ERROR_REPORT2, ixgbe_check_reset_blocked(), IXGBE_CONTROL_EOL_NL, IXGBE_CONTROL_MASK_NL, IXGBE_CONTROL_NL, IXGBE_CONTROL_SHIFT_NL, IXGBE_CONTROL_SOL_NL, IXGBE_DATA_MASK_NL, IXGBE_DATA_NL, IXGBE_DELAY_NL, IXGBE_ERR_PHY, IXGBE_ERROR_INVALID_STATE, ixgbe_get_sfp_init_sequence_offsets(), IXGBE_MDIO_PHY_XS_CONTROL, IXGBE_MDIO_PHY_XS_DEV_TYPE, IXGBE_MDIO_PHY_XS_RESET, IXGBE_SUCCESS, IXGBE_TWINAX_DEV, msec_delay, ixgbe_eeprom_info::ops, ixgbe_phy_info::ops, ixgbe_hw::phy, ixgbe_eeprom_operations::read, ixgbe_phy_operations::read_reg, and ixgbe_phy_operations::write_reg.

Referenced by ixgbe_init_phy_ops_82598().

◆ ixgbe_restart_auto_neg()

| void ixgbe_restart_auto_neg | ( | struct ixgbe_hw * | hw | ) |

ixgbe_restart_auto_neg - Restart auto negotiation on the PHY @hw: pointer to hardware structure

Definition at line 575 of file ixgbe_phy.c.

References ixgbe_check_reset_blocked(), IXGBE_MDIO_AUTO_NEG_CONTROL, IXGBE_MDIO_AUTO_NEG_DEV_TYPE, IXGBE_MII_RESTART, ixgbe_phy_info::ops, ixgbe_hw::phy, ixgbe_phy_operations::read_reg, and ixgbe_phy_operations::write_reg.

Referenced by ixgbe_setup_phy_link_generic(), and ixgbe_setup_phy_link_tnx().

◆ ixgbe_set_copper_phy_power()

ixgbe_set_copper_phy_power - Control power for copper phy @hw: pointer to hardware structure @on: true for on, false for off

Definition at line 2669 of file ixgbe_phy.c.

References ixgbe_check_reset_blocked(), IXGBE_MDIO_PHY_SET_LOW_POWER_MODE, IXGBE_MDIO_VENDOR_SPECIFIC_1_CONTROL, IXGBE_MDIO_VENDOR_SPECIFIC_1_DEV_TYPE, ixgbe_mng_present(), ixgbe_phy_info::ops, ixgbe_hw::phy, ixgbe_phy_operations::read_reg, and ixgbe_phy_operations::write_reg.

Referenced by ixgbe_enter_lplu_t_x550em(), ixgbe_get_lasi_ext_t_x550em(), and ixgbe_init_ops_X540().

◆ ixgbe_setup_phy_link_generic()

ixgbe_setup_phy_link_generic - Set and restart auto-neg @hw: pointer to hardware structure

Restart auto-negotiation and PHY and waits for completion.

Definition at line 806 of file ixgbe_phy.c.

References ixgbe_phy_info::autoneg_advertised, DEBUGFUNC, ixgbe_get_copper_link_capabilities_generic(), IXGBE_LINK_SPEED_100_FULL, IXGBE_LINK_SPEED_10GB_FULL, IXGBE_LINK_SPEED_1GB_FULL, IXGBE_LINK_SPEED_2_5GB_FULL, IXGBE_LINK_SPEED_5GB_FULL, ixgbe_mac_X550, IXGBE_MDIO_AUTO_NEG_DEV_TYPE, IXGBE_MII_100BASE_T_ADVERTISE, IXGBE_MII_100BASE_T_ADVERTISE_HALF, IXGBE_MII_10GBASE_T_ADVERTISE, IXGBE_MII_10GBASE_T_AUTONEG_CTRL_REG, IXGBE_MII_1GBASE_T_ADVERTISE, IXGBE_MII_2_5GBASE_T_ADVERTISE, IXGBE_MII_5GBASE_T_ADVERTISE, IXGBE_MII_AUTONEG_ADVERTISE_REG, IXGBE_MII_AUTONEG_REG, IXGBE_MII_AUTONEG_VENDOR_PROVISION_1_REG, ixgbe_restart_auto_neg(), IXGBE_SUCCESS, ixgbe_hw::mac, ixgbe_phy_info::ops, ixgbe_hw::phy, ixgbe_phy_operations::read_reg, ixgbe_mac_info::type, and ixgbe_phy_operations::write_reg.

Referenced by ixgbe_init_phy_ops_generic().

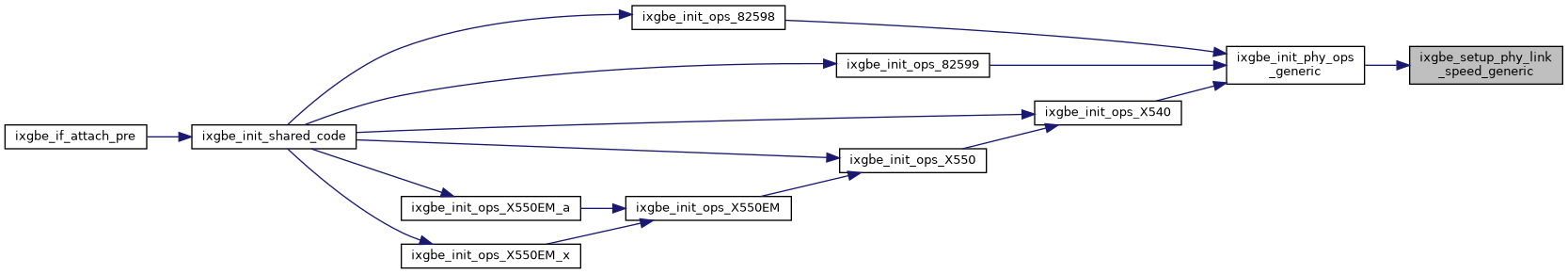

◆ ixgbe_setup_phy_link_speed_generic()

| s32 ixgbe_setup_phy_link_speed_generic | ( | struct ixgbe_hw * | hw, |

| ixgbe_link_speed | speed, | ||

| bool | autoneg_wait_to_complete | ||

| ) |

ixgbe_setup_phy_link_speed_generic - Sets the auto advertised capabilities @hw: pointer to hardware structure @speed: new link speed @autoneg_wait_to_complete: unused

Definition at line 885 of file ixgbe_phy.c.

References ixgbe_phy_info::autoneg_advertised, DEBUGFUNC, IXGBE_LINK_SPEED_100_FULL, IXGBE_LINK_SPEED_10_FULL, IXGBE_LINK_SPEED_10GB_FULL, IXGBE_LINK_SPEED_1GB_FULL, IXGBE_LINK_SPEED_2_5GB_FULL, IXGBE_LINK_SPEED_5GB_FULL, ixgbe_setup_phy_link(), IXGBE_SUCCESS, ixgbe_hw::phy, and UNREFERENCED_1PARAMETER.

Referenced by ixgbe_init_phy_ops_generic().

◆ ixgbe_setup_phy_link_tnx()

ixgbe_setup_phy_link_tnx - Set and restart auto-neg @hw: pointer to hardware structure

Restart auto-negotiation and PHY and waits for completion.

Definition at line 1043 of file ixgbe_phy.c.

References ixgbe_phy_info::autoneg_advertised, DEBUGFUNC, ixgbe_get_copper_link_capabilities_generic(), IXGBE_LINK_SPEED_100_FULL, IXGBE_LINK_SPEED_10GB_FULL, IXGBE_LINK_SPEED_1GB_FULL, IXGBE_MDIO_AUTO_NEG_DEV_TYPE, IXGBE_MII_100BASE_T_ADVERTISE, IXGBE_MII_10GBASE_T_ADVERTISE, IXGBE_MII_10GBASE_T_AUTONEG_CTRL_REG, IXGBE_MII_1GBASE_T_ADVERTISE_XNP_TX, IXGBE_MII_AUTONEG_ADVERTISE_REG, IXGBE_MII_AUTONEG_REG, IXGBE_MII_AUTONEG_XNP_TX_REG, ixgbe_restart_auto_neg(), IXGBE_SUCCESS, ixgbe_phy_info::ops, ixgbe_hw::phy, ixgbe_phy_operations::read_reg, and ixgbe_phy_operations::write_reg.

Referenced by ixgbe_init_phy_ops_82598(), and ixgbe_init_phy_ops_82599().

◆ ixgbe_tn_check_overtemp()

ixgbe_tn_check_overtemp - Checks if an overtemp occurred. @hw: pointer to hardware structure

Checks if the LASI temp alarm status was triggered due to overtemp

Definition at line 2641 of file ixgbe_phy.c.

References DEBUGFUNC, ixgbe_hw::device_id, ERROR_REPORT1, IXGBE_DEV_ID_82599_T3_LOM, IXGBE_ERR_OVERTEMP, IXGBE_ERROR_CAUTION, IXGBE_MDIO_PMA_PMD_DEV_TYPE, IXGBE_SUCCESS, IXGBE_TN_LASI_STATUS_REG, IXGBE_TN_LASI_STATUS_TEMP_ALARM, ixgbe_phy_info::ops, ixgbe_hw::phy, and ixgbe_phy_operations::read_reg.

Referenced by ixgbe_init_phy_ops_generic().

◆ ixgbe_validate_phy_addr()

ixgbe_validate_phy_addr - Determines phy address is valid @hw: pointer to hardware structure @phy_addr: PHY address

Definition at line 401 of file ixgbe_phy.c.

References ixgbe_phy_info::addr, DEBUGFUNC, DEBUGOUT1, IXGBE_MDIO_PHY_ID_HIGH, IXGBE_MDIO_PMA_PMD_DEV_TYPE, ixgbe_phy_info::ops, ixgbe_hw::phy, and ixgbe_phy_operations::read_reg.

Referenced by ixgbe_probe_phy().

◆ ixgbe_write_i2c_byte_generic()

ixgbe_write_i2c_byte_generic - Writes 8 bit word over I2C @hw: pointer to hardware structure @byte_offset: byte offset to write @dev_addr: address to write to @data: value to write

Performs byte write operation to SFP module's EEPROM over I2C interface at a specified device address.

Definition at line 2190 of file ixgbe_phy.c.

References ixgbe_write_i2c_byte_generic_int().

Referenced by ixgbe_init_phy_ops_generic(), and ixgbe_write_i2c_byte_82599().

◆ ixgbe_write_i2c_byte_generic_unlocked()

| s32 ixgbe_write_i2c_byte_generic_unlocked | ( | struct ixgbe_hw * | hw, |

| u8 | byte_offset, | ||

| u8 | dev_addr, | ||

| u8 | data | ||

| ) |

ixgbe_write_i2c_byte_generic_unlocked - Writes 8 bit word over I2C @hw: pointer to hardware structure @byte_offset: byte offset to write @dev_addr: address to write to @data: value to write

Performs byte write operation to SFP module's EEPROM over I2C interface at a specified device address.

Definition at line 2207 of file ixgbe_phy.c.

References ixgbe_write_i2c_byte_generic_int().

Referenced by ixgbe_init_phy_ops_generic().

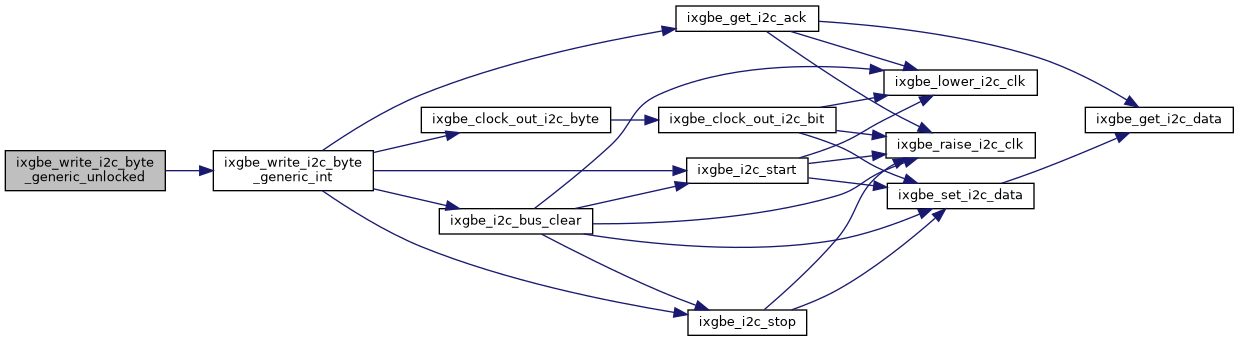

◆ ixgbe_write_i2c_combined_generic_int()

| s32 ixgbe_write_i2c_combined_generic_int | ( | struct ixgbe_hw * | hw, |

| u8 | addr, | ||

| u16 | reg, | ||

| u16 | val, | ||

| bool | lock | ||

| ) |

ixgbe_write_i2c_combined_generic_int - Perform I2C write combined operation @hw: pointer to the hardware structure @addr: I2C bus address to write to @reg: I2C device register to write to @val: value to write @lock: true if to take and release semaphore

Returns an error code on error.

Definition at line 187 of file ixgbe_phy.c.

References ixgbe_mac_operations::acquire_swfw_sync, DEBUGOUT, IXGBE_ERR_I2C, IXGBE_ERR_SWFW_SYNC, ixgbe_i2c_bus_clear(), ixgbe_i2c_start(), ixgbe_i2c_stop(), ixgbe_ones_comp_byte_add(), ixgbe_out_i2c_byte_ack(), ixgbe_hw::mac, ixgbe_mac_info::ops, ixgbe_hw::phy, ixgbe_phy_info::phy_semaphore_mask, and ixgbe_mac_operations::release_swfw_sync.

Referenced by ixgbe_write_i2c_combined_generic(), and ixgbe_write_i2c_combined_generic_unlocked().

◆ ixgbe_write_i2c_eeprom_generic()

ixgbe_write_i2c_eeprom_generic - Writes 8 bit EEPROM word over I2C interface @hw: pointer to hardware structure @byte_offset: EEPROM byte offset to write @eeprom_data: value to write

Performs byte write operation to SFP module's EEPROM over I2C interface.

Definition at line 1960 of file ixgbe_phy.c.

References DEBUGFUNC, IXGBE_I2C_EEPROM_DEV_ADDR, ixgbe_phy_info::ops, ixgbe_hw::phy, and ixgbe_phy_operations::write_i2c_byte.

Referenced by ixgbe_init_phy_ops_generic().

◆ ixgbe_write_phy_reg_generic()

| s32 ixgbe_write_phy_reg_generic | ( | struct ixgbe_hw * | hw, |

| u32 | reg_addr, | ||

| u32 | device_type, | ||

| u16 | phy_data | ||

| ) |

ixgbe_write_phy_reg_generic - Writes a value to specified PHY register using SWFW lock- this function is needed in most cases @hw: pointer to hardware structure @reg_addr: 32 bit PHY register to write @device_type: 5 bit device type @phy_data: Data to write to the PHY register

Definition at line 781 of file ixgbe_phy.c.

References ixgbe_mac_operations::acquire_swfw_sync, DEBUGFUNC, IXGBE_ERR_SWFW_SYNC, IXGBE_SUCCESS, ixgbe_hw::mac, ixgbe_mac_info::ops, ixgbe_phy_info::ops, ixgbe_hw::phy, ixgbe_phy_info::phy_semaphore_mask, ixgbe_mac_operations::release_swfw_sync, and ixgbe_phy_operations::write_reg_mdi.

Referenced by ixgbe_init_phy_ops_generic().

◆ ixgbe_write_phy_reg_mdi()

ixgbe_write_phy_reg_mdi - Writes a value to specified PHY register without SWFW lock @hw: pointer to hardware structure @reg_addr: 32 bit PHY register to write @device_type: 5 bit device type @phy_data: Data to write to the PHY register

Definition at line 707 of file ixgbe_phy.c.

References ixgbe_phy_info::addr, ERROR_REPORT1, IXGBE_ERR_PHY, IXGBE_ERROR_POLLING, IXGBE_MDIO_COMMAND_TIMEOUT, IXGBE_MSCA, IXGBE_MSCA_ADDR_CYCLE, IXGBE_MSCA_DEV_TYPE_SHIFT, IXGBE_MSCA_MDI_COMMAND, IXGBE_MSCA_NP_ADDR_SHIFT, IXGBE_MSCA_PHY_ADDR_SHIFT, IXGBE_MSCA_WRITE, IXGBE_MSRWD, IXGBE_READ_REG, IXGBE_SUCCESS, IXGBE_WRITE_REG, ixgbe_hw::phy, and usec_delay.

Referenced by ixgbe_init_phy_ops_generic().