Go to the source code of this file.

Macros | |

| #define | IXGBE_RTTDCS_TDPAC |

| #define | IXGBE_RTTDCS_VMPAC |

| #define | IXGBE_RTTDCS_TDRM 0x00000010 /* Transmit Recycle Mode */ |

| #define | IXGBE_RTTDCS_BDPM 0x00400000 /* Bypass Data Pipe - must clear! */ |

| #define | IXGBE_RTTDCS_BPBFSM |

| #define | IXGBE_RTTDCS_SPEED_CHG 0x80000000 /* Link speed change */ |

| #define | IXGBE_RTRUP2TC_UP_SHIFT 3 |

| #define | IXGBE_RTRUP2TC_UP_MASK 7 |

| #define | IXGBE_RTTUP2TC_UP_SHIFT 3 |

| #define | IXGBE_RTRPT4C_MCL_SHIFT 12 /* Offset to Max Credit Limit setting */ |

| #define | IXGBE_RTRPT4C_BWG_SHIFT 9 /* Offset to BWG index */ |

| #define | IXGBE_RTRPT4C_GSP 0x40000000 /* GSP enable bit */ |

| #define | IXGBE_RTRPT4C_LSP 0x80000000 /* LSP enable bit */ |

| #define | IXGBE_RDRXCTL_MPBEN |

| #define | IXGBE_RDRXCTL_MCEN |

| #define | IXGBE_RTRPCS_RRM 0x00000002 /* Receive Recycle Mode enable */ |

| #define | IXGBE_RTRPCS_RAC 0x00000004 |

| #define | IXGBE_RTRPCS_ARBDIS 0x00000040 /* Arbitration disable bit */ |

| #define | IXGBE_RTTDT2C_MCL_SHIFT 12 |

| #define | IXGBE_RTTDT2C_BWG_SHIFT 9 |

| #define | IXGBE_RTTDT2C_GSP 0x40000000 |

| #define | IXGBE_RTTDT2C_LSP 0x80000000 |

| #define | IXGBE_RTTPT2C_MCL_SHIFT 12 |

| #define | IXGBE_RTTPT2C_BWG_SHIFT 9 |

| #define | IXGBE_RTTPT2C_GSP 0x40000000 |

| #define | IXGBE_RTTPT2C_LSP 0x80000000 |

| #define | IXGBE_RTTPCS_TPPAC |

| #define | IXGBE_RTTPCS_ARBDIS 0x00000040 /* Arbiter disable */ |

| #define | IXGBE_RTTPCS_TPRM 0x00000100 /* Transmit Recycle Mode enable */ |

| #define | IXGBE_RTTPCS_ARBD_SHIFT 22 |

| #define | IXGBE_RTTPCS_ARBD_DCB 0x4 /* Arbitration delay in DCB mode */ |

| #define | IXGBE_TXPBTHRESH_DCB 0xA /* THRESH value for DCB mode */ |

| #define | IXGBE_SECTX_DCB 0x00001F00 /* DCB TX Buffer SEC IFG */ |

| #define | IXGBE_RTTBCNRC_RF_INT_SHIFT 14 |

| #define | IXGBE_RTTBCNRC_RS_ENA 0x80000000 |

| #define | IXGBE_RTTBCNCR_MNG_CMTGI 0x00000001 |

| #define | IXGBE_RTTBCNCR_MGN_BCNA_MODE 0x00000002 |

| #define | IXGBE_RTTBCNCR_RSV7_11_SHIFT 5 |

| #define | IXGBE_RTTBCNCR_G 0x00000400 |

| #define | IXGBE_RTTBCNCR_I 0x00000800 |

| #define | IXGBE_RTTBCNCR_H 0x00001000 |

| #define | IXGBE_RTTBCNCR_VER_SHIFT 14 |

| #define | IXGBE_RTTBCNCR_CMT_ETH_SHIFT 16 |

| #define | IXGBE_RTTBCNACL_SMAC_L_SHIFT 16 |

| #define | IXGBE_RTTBCNTG_BCNA_MODE 0x80000000 |

| #define | IXGBE_RTTBCNRTT_TS_SHIFT 3 |

| #define | IXGBE_RTTBCNRTT_TXQ_IDX_SHIFT 16 |

| #define | IXGBE_RTTBCNRD_BCN_CLEAR_ALL 0x00000002 |

| #define | IXGBE_RTTBCNRD_DRIFT_FAC_SHIFT 2 |

| #define | IXGBE_RTTBCNRD_DRIFT_INT_SHIFT 16 |

| #define | IXGBE_RTTBCNRD_DRIFT_ENA 0x80000000 |

Functions | |

| s32 | ixgbe_dcb_config_pfc_82599 (struct ixgbe_hw *, u8, u8 *) |

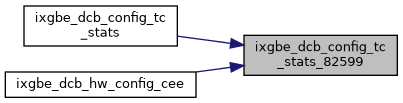

| s32 | ixgbe_dcb_config_tc_stats_82599 (struct ixgbe_hw *, struct ixgbe_dcb_config *) |

| s32 | ixgbe_dcb_get_tc_stats_82599 (struct ixgbe_hw *, struct ixgbe_hw_stats *, u8) |

| s32 | ixgbe_dcb_get_pfc_stats_82599 (struct ixgbe_hw *, struct ixgbe_hw_stats *, u8) |

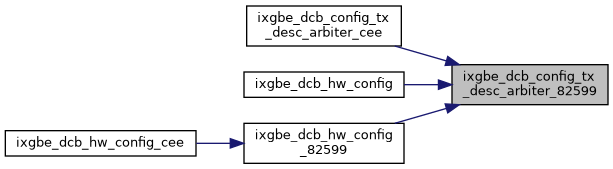

| s32 | ixgbe_dcb_config_tx_desc_arbiter_82599 (struct ixgbe_hw *, u16 *, u16 *, u8 *, u8 *) |

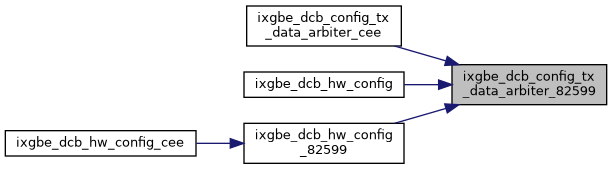

| s32 | ixgbe_dcb_config_tx_data_arbiter_82599 (struct ixgbe_hw *, u16 *, u16 *, u8 *, u8 *, u8 *) |

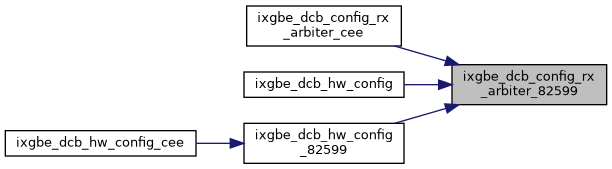

| s32 | ixgbe_dcb_config_rx_arbiter_82599 (struct ixgbe_hw *, u16 *, u16 *, u8 *, u8 *, u8 *) |

| s32 | ixgbe_dcb_config_82599 (struct ixgbe_hw *, struct ixgbe_dcb_config *) |

| s32 | ixgbe_dcb_hw_config_82599 (struct ixgbe_hw *, int, u16 *, u16 *, u8 *, u8 *, u8 *) |

Macro Definition Documentation

◆ IXGBE_RDRXCTL_MCEN

| #define IXGBE_RDRXCTL_MCEN |

Definition at line 59 of file ixgbe_dcb_82599.h.

◆ IXGBE_RDRXCTL_MPBEN

| #define IXGBE_RDRXCTL_MPBEN |

Definition at line 58 of file ixgbe_dcb_82599.h.

◆ IXGBE_RTRPCS_ARBDIS

| #define IXGBE_RTRPCS_ARBDIS 0x00000040 /* Arbitration disable bit */ |

Definition at line 65 of file ixgbe_dcb_82599.h.

◆ IXGBE_RTRPCS_RAC

| #define IXGBE_RTRPCS_RAC 0x00000004 |

Definition at line 64 of file ixgbe_dcb_82599.h.

◆ IXGBE_RTRPCS_RRM

| #define IXGBE_RTRPCS_RRM 0x00000002 /* Receive Recycle Mode enable */ |

Definition at line 62 of file ixgbe_dcb_82599.h.

◆ IXGBE_RTRPT4C_BWG_SHIFT

| #define IXGBE_RTRPT4C_BWG_SHIFT 9 /* Offset to BWG index */ |

Definition at line 54 of file ixgbe_dcb_82599.h.

◆ IXGBE_RTRPT4C_GSP

| #define IXGBE_RTRPT4C_GSP 0x40000000 /* GSP enable bit */ |

Definition at line 55 of file ixgbe_dcb_82599.h.

◆ IXGBE_RTRPT4C_LSP

| #define IXGBE_RTRPT4C_LSP 0x80000000 /* LSP enable bit */ |

Definition at line 56 of file ixgbe_dcb_82599.h.

◆ IXGBE_RTRPT4C_MCL_SHIFT

| #define IXGBE_RTRPT4C_MCL_SHIFT 12 /* Offset to Max Credit Limit setting */ |

Definition at line 53 of file ixgbe_dcb_82599.h.

◆ IXGBE_RTRUP2TC_UP_MASK

| #define IXGBE_RTRUP2TC_UP_MASK 7 |

Definition at line 49 of file ixgbe_dcb_82599.h.

◆ IXGBE_RTRUP2TC_UP_SHIFT

| #define IXGBE_RTRUP2TC_UP_SHIFT 3 |

Definition at line 48 of file ixgbe_dcb_82599.h.

◆ IXGBE_RTTBCNACL_SMAC_L_SHIFT

| #define IXGBE_RTTBCNACL_SMAC_L_SHIFT 16 |

Definition at line 103 of file ixgbe_dcb_82599.h.

◆ IXGBE_RTTBCNCR_CMT_ETH_SHIFT

| #define IXGBE_RTTBCNCR_CMT_ETH_SHIFT 16 |

Definition at line 101 of file ixgbe_dcb_82599.h.

◆ IXGBE_RTTBCNCR_G

| #define IXGBE_RTTBCNCR_G 0x00000400 |

Definition at line 97 of file ixgbe_dcb_82599.h.

◆ IXGBE_RTTBCNCR_H

| #define IXGBE_RTTBCNCR_H 0x00001000 |

Definition at line 99 of file ixgbe_dcb_82599.h.

◆ IXGBE_RTTBCNCR_I

| #define IXGBE_RTTBCNCR_I 0x00000800 |

Definition at line 98 of file ixgbe_dcb_82599.h.

◆ IXGBE_RTTBCNCR_MGN_BCNA_MODE

| #define IXGBE_RTTBCNCR_MGN_BCNA_MODE 0x00000002 |

Definition at line 95 of file ixgbe_dcb_82599.h.

◆ IXGBE_RTTBCNCR_MNG_CMTGI

| #define IXGBE_RTTBCNCR_MNG_CMTGI 0x00000001 |

Definition at line 94 of file ixgbe_dcb_82599.h.

◆ IXGBE_RTTBCNCR_RSV7_11_SHIFT

| #define IXGBE_RTTBCNCR_RSV7_11_SHIFT 5 |

Definition at line 96 of file ixgbe_dcb_82599.h.

◆ IXGBE_RTTBCNCR_VER_SHIFT

| #define IXGBE_RTTBCNCR_VER_SHIFT 14 |

Definition at line 100 of file ixgbe_dcb_82599.h.

◆ IXGBE_RTTBCNRC_RF_INT_SHIFT

| #define IXGBE_RTTBCNRC_RF_INT_SHIFT 14 |

Definition at line 91 of file ixgbe_dcb_82599.h.

◆ IXGBE_RTTBCNRC_RS_ENA

| #define IXGBE_RTTBCNRC_RS_ENA 0x80000000 |

Definition at line 92 of file ixgbe_dcb_82599.h.

◆ IXGBE_RTTBCNRD_BCN_CLEAR_ALL

| #define IXGBE_RTTBCNRD_BCN_CLEAR_ALL 0x00000002 |

Definition at line 110 of file ixgbe_dcb_82599.h.

◆ IXGBE_RTTBCNRD_DRIFT_ENA

| #define IXGBE_RTTBCNRD_DRIFT_ENA 0x80000000 |

Definition at line 113 of file ixgbe_dcb_82599.h.

◆ IXGBE_RTTBCNRD_DRIFT_FAC_SHIFT

| #define IXGBE_RTTBCNRD_DRIFT_FAC_SHIFT 2 |

Definition at line 111 of file ixgbe_dcb_82599.h.

◆ IXGBE_RTTBCNRD_DRIFT_INT_SHIFT

| #define IXGBE_RTTBCNRD_DRIFT_INT_SHIFT 16 |

Definition at line 112 of file ixgbe_dcb_82599.h.

◆ IXGBE_RTTBCNRTT_TS_SHIFT

| #define IXGBE_RTTBCNRTT_TS_SHIFT 3 |

Definition at line 107 of file ixgbe_dcb_82599.h.

◆ IXGBE_RTTBCNRTT_TXQ_IDX_SHIFT

| #define IXGBE_RTTBCNRTT_TXQ_IDX_SHIFT 16 |

Definition at line 108 of file ixgbe_dcb_82599.h.

◆ IXGBE_RTTBCNTG_BCNA_MODE

| #define IXGBE_RTTBCNTG_BCNA_MODE 0x80000000 |

Definition at line 105 of file ixgbe_dcb_82599.h.

◆ IXGBE_RTTDCS_BDPM

| #define IXGBE_RTTDCS_BDPM 0x00400000 /* Bypass Data Pipe - must clear! */ |

Definition at line 43 of file ixgbe_dcb_82599.h.

◆ IXGBE_RTTDCS_BPBFSM

| #define IXGBE_RTTDCS_BPBFSM |

Definition at line 44 of file ixgbe_dcb_82599.h.

◆ IXGBE_RTTDCS_SPEED_CHG

| #define IXGBE_RTTDCS_SPEED_CHG 0x80000000 /* Link speed change */ |

Definition at line 45 of file ixgbe_dcb_82599.h.

◆ IXGBE_RTTDCS_TDPAC

| #define IXGBE_RTTDCS_TDPAC |

Definition at line 40 of file ixgbe_dcb_82599.h.

◆ IXGBE_RTTDCS_TDRM

| #define IXGBE_RTTDCS_TDRM 0x00000010 /* Transmit Recycle Mode */ |

Definition at line 42 of file ixgbe_dcb_82599.h.

◆ IXGBE_RTTDCS_VMPAC

| #define IXGBE_RTTDCS_VMPAC |

Definition at line 41 of file ixgbe_dcb_82599.h.

◆ IXGBE_RTTDT2C_BWG_SHIFT

| #define IXGBE_RTTDT2C_BWG_SHIFT 9 |

Definition at line 69 of file ixgbe_dcb_82599.h.

◆ IXGBE_RTTDT2C_GSP

| #define IXGBE_RTTDT2C_GSP 0x40000000 |

Definition at line 70 of file ixgbe_dcb_82599.h.

◆ IXGBE_RTTDT2C_LSP

| #define IXGBE_RTTDT2C_LSP 0x80000000 |

Definition at line 71 of file ixgbe_dcb_82599.h.

◆ IXGBE_RTTDT2C_MCL_SHIFT

| #define IXGBE_RTTDT2C_MCL_SHIFT 12 |

Definition at line 68 of file ixgbe_dcb_82599.h.

◆ IXGBE_RTTPCS_ARBD_DCB

| #define IXGBE_RTTPCS_ARBD_DCB 0x4 /* Arbitration delay in DCB mode */ |

Definition at line 83 of file ixgbe_dcb_82599.h.

◆ IXGBE_RTTPCS_ARBD_SHIFT

| #define IXGBE_RTTPCS_ARBD_SHIFT 22 |

Definition at line 82 of file ixgbe_dcb_82599.h.

◆ IXGBE_RTTPCS_ARBDIS

| #define IXGBE_RTTPCS_ARBDIS 0x00000040 /* Arbiter disable */ |

Definition at line 80 of file ixgbe_dcb_82599.h.

◆ IXGBE_RTTPCS_TPPAC

| #define IXGBE_RTTPCS_TPPAC |

Definition at line 79 of file ixgbe_dcb_82599.h.

◆ IXGBE_RTTPCS_TPRM

| #define IXGBE_RTTPCS_TPRM 0x00000100 /* Transmit Recycle Mode enable */ |

Definition at line 81 of file ixgbe_dcb_82599.h.

◆ IXGBE_RTTPT2C_BWG_SHIFT

| #define IXGBE_RTTPT2C_BWG_SHIFT 9 |

Definition at line 74 of file ixgbe_dcb_82599.h.

◆ IXGBE_RTTPT2C_GSP

| #define IXGBE_RTTPT2C_GSP 0x40000000 |

Definition at line 75 of file ixgbe_dcb_82599.h.

◆ IXGBE_RTTPT2C_LSP

| #define IXGBE_RTTPT2C_LSP 0x80000000 |

Definition at line 76 of file ixgbe_dcb_82599.h.

◆ IXGBE_RTTPT2C_MCL_SHIFT

| #define IXGBE_RTTPT2C_MCL_SHIFT 12 |

Definition at line 73 of file ixgbe_dcb_82599.h.

◆ IXGBE_RTTUP2TC_UP_SHIFT

| #define IXGBE_RTTUP2TC_UP_SHIFT 3 |

Definition at line 51 of file ixgbe_dcb_82599.h.

◆ IXGBE_SECTX_DCB

| #define IXGBE_SECTX_DCB 0x00001F00 /* DCB TX Buffer SEC IFG */ |

Definition at line 88 of file ixgbe_dcb_82599.h.

◆ IXGBE_TXPBTHRESH_DCB

| #define IXGBE_TXPBTHRESH_DCB 0xA /* THRESH value for DCB mode */ |

Definition at line 85 of file ixgbe_dcb_82599.h.

Function Documentation

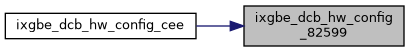

◆ ixgbe_dcb_config_82599()

| s32 ixgbe_dcb_config_82599 | ( | struct ixgbe_hw * | hw, |

| struct ixgbe_dcb_config * | dcb_config | ||

| ) |

ixgbe_dcb_config_82599 - Configure general DCB parameters @hw: pointer to hardware structure @dcb_config: pointer to ixgbe_dcb_config structure

Configure general DCB parameters.

Definition at line 508 of file ixgbe_dcb_82599.c.

References ASSERT, IXGBE_MRQC, IXGBE_MRQC_MRQE_MASK, IXGBE_MRQC_RSSEN, IXGBE_MRQC_RT4TCEN, IXGBE_MRQC_RT8TCEN, IXGBE_MRQC_RTRSS4TCEN, IXGBE_MRQC_RTRSS8TCEN, IXGBE_MRQC_VMDQRT4TCEN, IXGBE_MTQC, IXGBE_MTQC_4TC_4TQ, IXGBE_MTQC_8TC_8TQ, IXGBE_MTQC_RT_ENA, IXGBE_MTQC_VT_ENA, IXGBE_QDE, IXGBE_QDE_IDX_SHIFT, IXGBE_QDE_WRITE, IXGBE_READ_REG, IXGBE_RTTDCS, IXGBE_RTTDCS_ARBDIS, IXGBE_SECTX_DCB, IXGBE_SECTXMINIFG, IXGBE_SUCCESS, IXGBE_WRITE_REG, ixgbe_dcb_config::num_tcs, ixgbe_dcb_num_tcs::pg_tcs, and ixgbe_dcb_config::vt_mode.

Referenced by ixgbe_dcb_hw_config_cee().

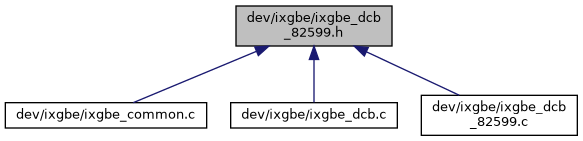

◆ ixgbe_dcb_config_pfc_82599()

ixgbe_dcb_config_pfc_82599 - Configure priority flow control @hw: pointer to hardware structure @pfc_en: enabled pfc bitmask @map: priority to tc assignments indexed by priority

Configure Priority Flow Control (PFC) for each traffic class.

Definition at line 295 of file ixgbe_dcb_82599.c.

References ixgbe_hw::fc, ixgbe_fc_info::high_water, IXGBE_DCB_MAX_TRAFFIC_CLASS, IXGBE_DCB_MAX_USER_PRIORITY, IXGBE_FCCFG, IXGBE_FCCFG_TFCE_PRIORITY, IXGBE_FCRTH_82599, IXGBE_FCRTH_FCEN, IXGBE_FCRTL_82599, IXGBE_FCRTL_XONE, IXGBE_FCRTV, IXGBE_FCTTV, ixgbe_mac_X540, IXGBE_MFLCN, IXGBE_MFLCN_DPF, IXGBE_MFLCN_RFCE, IXGBE_MFLCN_RPFCE, IXGBE_MFLCN_RPFCE_MASK, IXGBE_MFLCN_RPFCE_SHIFT, IXGBE_READ_REG, IXGBE_RXPBSIZE, IXGBE_SUCCESS, IXGBE_WRITE_REG, ixgbe_fc_info::low_water, ixgbe_hw::mac, ixgbe_fc_info::pause_time, and ixgbe_mac_info::type.

Referenced by ixgbe_dcb_config_pfc(), and ixgbe_dcb_config_pfc_cee().

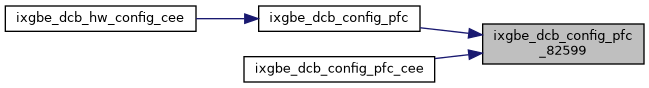

◆ ixgbe_dcb_config_rx_arbiter_82599()

| s32 ixgbe_dcb_config_rx_arbiter_82599 | ( | struct ixgbe_hw * | hw, |

| u16 * | refill, | ||

| u16 * | max, | ||

| u8 * | bwg_id, | ||

| u8 * | tsa, | ||

| u8 * | map | ||

| ) |

ixgbe_dcb_config_rx_arbiter_82599 - Config Rx Data arbiter @hw: pointer to hardware structure @refill: refill credits index by traffic class @max: max credits index by traffic class @bwg_id: bandwidth grouping indexed by traffic class @tsa: transmission selection algorithm indexed by traffic class @map: priority to tc assignments indexed by priority

Configure Rx Packet Arbiter and credits for each traffic class.

Definition at line 122 of file ixgbe_dcb_82599.c.

References IXGBE_DCB_MAX_TRAFFIC_CLASS, IXGBE_DCB_MAX_USER_PRIORITY, ixgbe_dcb_tsa_strict, IXGBE_RTRPCS, IXGBE_RTRPCS_ARBDIS, IXGBE_RTRPCS_RAC, IXGBE_RTRPCS_RRM, IXGBE_RTRPT4C, IXGBE_RTRPT4C_BWG_SHIFT, IXGBE_RTRPT4C_LSP, IXGBE_RTRPT4C_MCL_SHIFT, IXGBE_RTRUP2TC, IXGBE_RTRUP2TC_UP_SHIFT, IXGBE_SUCCESS, and IXGBE_WRITE_REG.

Referenced by ixgbe_dcb_config_rx_arbiter_cee(), ixgbe_dcb_hw_config(), and ixgbe_dcb_hw_config_82599().

◆ ixgbe_dcb_config_tc_stats_82599()

| s32 ixgbe_dcb_config_tc_stats_82599 | ( | struct ixgbe_hw * | hw, |

| struct ixgbe_dcb_config * | dcb_config | ||

| ) |

ixgbe_dcb_config_tc_stats_82599 - Config traffic class statistics @hw: pointer to hardware structure @dcb_config: pointer to ixgbe_dcb_config structure

Configure queue statistics registers, all queues belonging to same traffic class uses a single set of queue statistics counters.

Definition at line 382 of file ixgbe_dcb_82599.c.

References IXGBE_ERR_PARAM, IXGBE_RQSMR, IXGBE_SUCCESS, IXGBE_TQSM, IXGBE_WRITE_REG, ixgbe_dcb_config::num_tcs, ixgbe_dcb_num_tcs::pg_tcs, and ixgbe_dcb_config::vt_mode.

Referenced by ixgbe_dcb_config_tc_stats(), and ixgbe_dcb_hw_config_cee().

◆ ixgbe_dcb_config_tx_data_arbiter_82599()

| s32 ixgbe_dcb_config_tx_data_arbiter_82599 | ( | struct ixgbe_hw * | hw, |

| u16 * | refill, | ||

| u16 * | max, | ||

| u8 * | bwg_id, | ||

| u8 * | tsa, | ||

| u8 * | map | ||

| ) |

ixgbe_dcb_config_tx_data_arbiter_82599 - Config Tx Data arbiter @hw: pointer to hardware structure @refill: refill credits index by traffic class @max: max credits index by traffic class @bwg_id: bandwidth grouping indexed by traffic class @tsa: transmission selection algorithm indexed by traffic class @map: priority to tc assignments indexed by priority

Configure Tx Packet Arbiter and credits for each traffic class.

Definition at line 233 of file ixgbe_dcb_82599.c.

References IXGBE_DCB_MAX_TRAFFIC_CLASS, IXGBE_DCB_MAX_USER_PRIORITY, ixgbe_dcb_tsa_group_strict_cee, ixgbe_dcb_tsa_strict, IXGBE_RTTPCS, IXGBE_RTTPCS_ARBD_DCB, IXGBE_RTTPCS_ARBD_SHIFT, IXGBE_RTTPCS_ARBDIS, IXGBE_RTTPCS_TPPAC, IXGBE_RTTPCS_TPRM, IXGBE_RTTPT2C, IXGBE_RTTPT2C_BWG_SHIFT, IXGBE_RTTPT2C_GSP, IXGBE_RTTPT2C_LSP, IXGBE_RTTPT2C_MCL_SHIFT, IXGBE_RTTUP2TC, IXGBE_RTTUP2TC_UP_SHIFT, IXGBE_SUCCESS, and IXGBE_WRITE_REG.

Referenced by ixgbe_dcb_config_tx_data_arbiter_cee(), ixgbe_dcb_hw_config(), and ixgbe_dcb_hw_config_82599().

◆ ixgbe_dcb_config_tx_desc_arbiter_82599()

| s32 ixgbe_dcb_config_tx_desc_arbiter_82599 | ( | struct ixgbe_hw * | hw, |

| u16 * | refill, | ||

| u16 * | max, | ||

| u8 * | bwg_id, | ||

| u8 * | tsa | ||

| ) |

ixgbe_dcb_config_tx_desc_arbiter_82599 - Config Tx Desc. arbiter @hw: pointer to hardware structure @refill: refill credits index by traffic class @max: max credits index by traffic class @bwg_id: bandwidth grouping indexed by traffic class @tsa: transmission selection algorithm indexed by traffic class

Configure Tx Descriptor Arbiter and credits for each traffic class.

Definition at line 184 of file ixgbe_dcb_82599.c.

References IXGBE_DCB_MAX_TRAFFIC_CLASS, ixgbe_dcb_tsa_group_strict_cee, ixgbe_dcb_tsa_strict, IXGBE_RTTDCS, IXGBE_RTTDCS_TDPAC, IXGBE_RTTDCS_TDRM, IXGBE_RTTDQSEL, IXGBE_RTTDT1C, IXGBE_RTTDT2C, IXGBE_RTTDT2C_BWG_SHIFT, IXGBE_RTTDT2C_GSP, IXGBE_RTTDT2C_LSP, IXGBE_RTTDT2C_MCL_SHIFT, IXGBE_SUCCESS, and IXGBE_WRITE_REG.

Referenced by ixgbe_dcb_config_tx_desc_arbiter_cee(), ixgbe_dcb_hw_config(), and ixgbe_dcb_hw_config_82599().

◆ ixgbe_dcb_get_pfc_stats_82599()

| s32 ixgbe_dcb_get_pfc_stats_82599 | ( | struct ixgbe_hw * | hw, |

| struct ixgbe_hw_stats * | stats, | ||

| u8 | tc_count | ||

| ) |

ixgbe_dcb_get_pfc_stats_82599 - Return CBFC status data @hw: pointer to hardware structure @stats: pointer to statistics structure @tc_count: Number of elements in bwg_array.

This function returns the CBFC status data for each of the Traffic Classes.

Definition at line 90 of file ixgbe_dcb_82599.c.

References DEBUGFUNC, IXGBE_DCB_MAX_TRAFFIC_CLASS, IXGBE_ERR_PARAM, IXGBE_PXOFFRXCNT, IXGBE_PXOFFTXC, IXGBE_READ_REG, IXGBE_SUCCESS, ixgbe_hw_stats::pxoffrxc, and ixgbe_hw_stats::pxofftxc.

Referenced by ixgbe_dcb_get_pfc_stats().

◆ ixgbe_dcb_get_tc_stats_82599()

| s32 ixgbe_dcb_get_tc_stats_82599 | ( | struct ixgbe_hw * | hw, |

| struct ixgbe_hw_stats * | stats, | ||

| u8 | tc_count | ||

| ) |

ixgbe_dcb_get_tc_stats_82599 - Returns status for each traffic class @hw: pointer to hardware structure @stats: pointer to statistics structure @tc_count: Number of elements in bwg_array.

This function returns the status data for each of the Traffic Classes in use.

Definition at line 49 of file ixgbe_dcb_82599.c.

References DEBUGFUNC, IXGBE_DCB_MAX_TRAFFIC_CLASS, IXGBE_ERR_PARAM, IXGBE_QBRC_H, IXGBE_QBRC_L, IXGBE_QBTC_H, IXGBE_QBTC_L, IXGBE_QPRC, IXGBE_QPRDC, IXGBE_QPTC, IXGBE_READ_REG, IXGBE_SUCCESS, ixgbe_hw_stats::qbrc, ixgbe_hw_stats::qbtc, ixgbe_hw_stats::qprc, ixgbe_hw_stats::qprdc, and ixgbe_hw_stats::qptc.

Referenced by ixgbe_dcb_get_tc_stats().

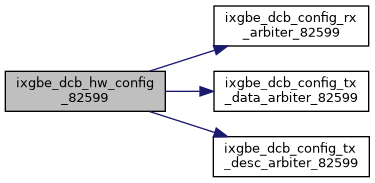

◆ ixgbe_dcb_hw_config_82599()

| s32 ixgbe_dcb_hw_config_82599 | ( | struct ixgbe_hw * | hw, |

| int | link_speed, | ||

| u16 * | refill, | ||

| u16 * | max, | ||

| u8 * | bwg_id, | ||

| u8 * | tsa, | ||

| u8 * | map | ||

| ) |

ixgbe_dcb_hw_config_82599 - Configure and enable DCB @hw: pointer to hardware structure @link_speed: unused @refill: refill credits index by traffic class @max: max credits index by traffic class @bwg_id: bandwidth grouping indexed by traffic class @tsa: transmission selection algorithm indexed by traffic class @map: priority to tc assignments indexed by priority

Configure dcb settings and enable dcb mode.

Definition at line 597 of file ixgbe_dcb_82599.c.

References ixgbe_dcb_config_rx_arbiter_82599(), ixgbe_dcb_config_tx_data_arbiter_82599(), ixgbe_dcb_config_tx_desc_arbiter_82599(), IXGBE_SUCCESS, and UNREFERENCED_1PARAMETER.

Referenced by ixgbe_dcb_hw_config_cee().