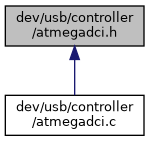

Go to the source code of this file.

Data Structures | |

| struct | atmegadci_td |

| struct | atmegadci_std_temp |

| struct | atmegadci_config_desc |

| union | atmegadci_hub_temp |

| struct | atmegadci_flags |

| struct | atmegadci_softc |

Macros | |

| #define | ATMEGA_MAX_DEVICES (USB_MIN_DEVICES + 1) |

| #define | ATMEGA_OTGTCON 0xF9 |

| #define | ATMEGA_OTGTCON_VALUE(x) ((x) << 0) |

| #define | ATMEGA_OTGTCON_PAGE(x) ((x) << 5) |

| #define | ATMEGA_UEINT 0xF4 |

| #define | ATMEGA_UEINT_MASK(n) (1 << (n)) /* endpoint interrupt mask */ |

| #define | ATMEGA_UEBCHX 0xF3 /* FIFO byte count high */ |

| #define | ATMEGA_UEBCLX 0xF2 /* FIFO byte count low */ |

| #define | ATMEGA_UEDATX 0xF1 /* FIFO data */ |

| #define | ATMEGA_UEIENX 0xF0 /* interrupt enable register */ |

| #define | ATMEGA_UEIENX_TXINE (1 << 0) |

| #define | ATMEGA_UEIENX_STALLEDE (1 << 1) |

| #define | ATMEGA_UEIENX_RXOUTE (1 << 2) |

| #define | ATMEGA_UEIENX_RXSTPE (1 << 3) /* received SETUP packet */ |

| #define | ATMEGA_UEIENX_NAKOUTE (1 << 4) |

| #define | ATMEGA_UEIENX_NAKINE (1 << 6) |

| #define | ATMEGA_UEIENX_FLERRE (1 << 7) |

| #define | ATMEGA_UESTA1X 0xEF |

| #define | ATMEGA_UESTA1X_CURRBK (3 << 0) /* current bank */ |

| #define | ATMEGA_UESTA1X_CTRLDIR (1 << 2) /* control endpoint direction */ |

| #define | ATMEGA_UESTA0X 0xEE |

| #define | ATMEGA_UESTA0X_NBUSYBK (3 << 0) |

| #define | ATMEGA_UESTA0X_DTSEQ (3 << 2) |

| #define | ATMEGA_UESTA0X_UNDERFI (1 << 5) /* underflow */ |

| #define | ATMEGA_UESTA0X_OVERFI (1 << 6) /* overflow */ |

| #define | ATMEGA_UESTA0X_CFGOK (1 << 7) |

| #define | ATMEGA_UECFG1X 0xED /* endpoint config register */ |

| #define | ATMEGA_UECFG1X_ALLOC (1 << 1) |

| #define | ATMEGA_UECFG1X_EPBK0 (0 << 2) |

| #define | ATMEGA_UECFG1X_EPBK1 (1 << 2) |

| #define | ATMEGA_UECFG1X_EPBK2 (2 << 2) |

| #define | ATMEGA_UECFG1X_EPBK3 (3 << 2) |

| #define | ATMEGA_UECFG1X_EPSIZE(n) ((n) << 4) |

| #define | ATMEGA_UECFG0X 0xEC |

| #define | ATMEGA_UECFG0X_EPDIR (1 << 0) /* endpoint direction */ |

| #define | ATMEGA_UECFG0X_EPTYPE0 (0 << 6) |

| #define | ATMEGA_UECFG0X_EPTYPE1 (1 << 6) |

| #define | ATMEGA_UECFG0X_EPTYPE2 (2 << 6) |

| #define | ATMEGA_UECFG0X_EPTYPE3 (3 << 6) |

| #define | ATMEGA_UECONX 0xEB |

| #define | ATMEGA_UECONX_EPEN (1 << 0) |

| #define | ATMEGA_UECONX_RSTDT (1 << 3) |

| #define | ATMEGA_UECONX_STALLRQC (1 << 4) /* stall request clear */ |

| #define | ATMEGA_UECONX_STALLRQ (1 << 5) /* stall request set */ |

| #define | ATMEGA_UERST 0xEA /* endpoint reset register */ |

| #define | ATMEGA_UERST_MASK(n) (1 << (n)) |

| #define | ATMEGA_UENUM 0xE9 /* endpoint number */ |

| #define | ATMEGA_UEINTX 0xE8 /* interrupt register */ |

| #define | ATMEGA_UEINTX_TXINI (1 << 0) |

| #define | ATMEGA_UEINTX_STALLEDI (1 << 1) |

| #define | ATMEGA_UEINTX_RXOUTI (1 << 2) |

| #define | ATMEGA_UEINTX_RXSTPI (1 << 3) /* received setup packet */ |

| #define | ATMEGA_UEINTX_NAKOUTI (1 << 4) |

| #define | ATMEGA_UEINTX_RWAL (1 << 5) |

| #define | ATMEGA_UEINTX_NAKINI (1 << 6) |

| #define | ATMEGA_UEINTX_FIFOCON (1 << 7) |

| #define | ATMEGA_UDMFN 0xE6 |

| #define | ATMEGA_UDMFN_FNCERR (1 << 4) |

| #define | ATMEGA_UDFNUMH 0xE5 /* frame number high */ |

| #define | ATMEGA_UDFNUMH_MASK 7 |

| #define | ATMEGA_UDFNUML 0xE4 /* frame number low */ |

| #define | ATMEGA_UDFNUML_MASK 0xFF |

| #define | ATMEGA_FRAME_MASK 0x7FF |

| #define | ATMEGA_UDADDR 0xE3 /* USB address */ |

| #define | ATMEGA_UDADDR_MASK 0x7F |

| #define | ATMEGA_UDADDR_ADDEN (1 << 7) |

| #define | ATMEGA_UDIEN 0xE2 /* USB device interrupt enable */ |

| #define | ATMEGA_UDINT_SUSPE (1 << 0) |

| #define | ATMEGA_UDINT_MSOFE (1 << 1) |

| #define | ATMEGA_UDINT_SOFE (1 << 2) |

| #define | ATMEGA_UDINT_EORSTE (1 << 3) |

| #define | ATMEGA_UDINT_WAKEUPE (1 << 4) |

| #define | ATMEGA_UDINT_EORSME (1 << 5) |

| #define | ATMEGA_UDINT_UPRSME (1 << 6) |

| #define | ATMEGA_UDINT 0xE1 /* USB device interrupt status */ |

| #define | ATMEGA_UDINT_SUSPI (1 << 0) |

| #define | ATMEGA_UDINT_MSOFI (1 << 1) |

| #define | ATMEGA_UDINT_SOFI (1 << 2) |

| #define | ATMEGA_UDINT_EORSTI (1 << 3) |

| #define | ATMEGA_UDINT_WAKEUPI (1 << 4) |

| #define | ATMEGA_UDINT_EORSMI (1 << 5) |

| #define | ATMEGA_UDINT_UPRSMI (1 << 6) |

| #define | ATMEGA_UDCON 0xE0 /* USB device connection register */ |

| #define | ATMEGA_UDCON_DETACH (1 << 0) |

| #define | ATMEGA_UDCON_RMWKUP (1 << 1) |

| #define | ATMEGA_UDCON_LSM (1 << 2) |

| #define | ATMEGA_UDCON_RSTCPU (1 << 3) |

| #define | ATMEGA_OTGINT 0xDF |

| #define | ATMEGA_OTGCON 0xDD |

| #define | ATMEGA_OTGCON_VBUSRQC (1 << 0) |

| #define | ATMEGA_OTGCON_VBUSREQ (1 << 1) |

| #define | ATMEGA_OTGCON_VBUSHWC (1 << 2) |

| #define | ATMEGA_OTGCON_SRPSEL (1 << 3) |

| #define | ATMEGA_OTGCON_SRPREQ (1 << 4) |

| #define | ATMEGA_OTGCON_HNPREQ (1 << 5) |

| #define | ATMEGA_USBINT 0xDA |

| #define | ATMEGA_USBINT_VBUSTI (1 << 0) /* USB VBUS interrupt */ |

| #define | ATMEGA_USBINT_IDI (1 << 1) /* USB ID interrupt */ |

| #define | ATMEGA_USBSTA 0xD9 |

| #define | ATMEGA_USBSTA_VBUS (1 << 0) |

| #define | ATMEGA_USBSTA_ID (1 << 1) |

| #define | ATMEGA_USBCON 0xD8 |

| #define | ATMEGA_USBCON_VBUSTE (1 << 0) |

| #define | ATMEGA_USBCON_IDE (1 << 1) |

| #define | ATMEGA_USBCON_OTGPADE (1 << 4) |

| #define | ATMEGA_USBCON_FRZCLK (1 << 5) |

| #define | ATMEGA_USBCON_USBE (1 << 7) |

| #define | ATMEGA_UHWCON 0xD7 |

| #define | ATMEGA_UHWCON_UVREGE (1 << 0) |

| #define | ATMEGA_UHWCON_UVCONE (1 << 4) |

| #define | ATMEGA_UHWCON_UIDE (1 << 6) |

| #define | ATMEGA_UHWCON_UIMOD (1 << 7) |

| #define | ATMEGA_READ_1(sc, reg) bus_space_read_1((sc)->sc_io_tag, (sc)->sc_io_hdl, reg) |

| #define | ATMEGA_WRITE_1(sc, reg, data) bus_space_write_1((sc)->sc_io_tag, (sc)->sc_io_hdl, reg, data) |

| #define | ATMEGA_WRITE_MULTI_1(sc, reg, ptr, len) bus_space_write_multi_1((sc)->sc_io_tag, (sc)->sc_io_hdl, reg, ptr, len) |

| #define | ATMEGA_READ_MULTI_1(sc, reg, ptr, len) bus_space_read_multi_1((sc)->sc_io_tag, (sc)->sc_io_hdl, reg, ptr, len) |

| #define | ATMEGA_EP_MAX 7 |

Typedefs | |

| typedef uint8_t() | atmegadci_cmd_t(struct atmegadci_td *td) |

| typedef void() | atmegadci_clocks_t(struct usb_bus *) |

Functions | |

| usb_error_t | atmegadci_init (struct atmegadci_softc *sc) |

| void | atmegadci_uninit (struct atmegadci_softc *sc) |

| void | atmegadci_interrupt (struct atmegadci_softc *sc) |

Variables | |

| struct atmegadci_config_desc | __packed |

Macro Definition Documentation

◆ ATMEGA_EP_MAX

| #define ATMEGA_EP_MAX 7 |

Definition at line 191 of file atmegadci.h.

◆ ATMEGA_FRAME_MASK

| #define ATMEGA_FRAME_MASK 0x7FF |

Definition at line 115 of file atmegadci.h.

◆ ATMEGA_MAX_DEVICES

| #define ATMEGA_MAX_DEVICES (USB_MIN_DEVICES + 1) |

Definition at line 37 of file atmegadci.h.

◆ ATMEGA_OTGCON

| #define ATMEGA_OTGCON 0xDD |

Definition at line 147 of file atmegadci.h.

◆ ATMEGA_OTGCON_HNPREQ

| #define ATMEGA_OTGCON_HNPREQ (1 << 5) |

Definition at line 153 of file atmegadci.h.

◆ ATMEGA_OTGCON_SRPREQ

| #define ATMEGA_OTGCON_SRPREQ (1 << 4) |

Definition at line 152 of file atmegadci.h.

◆ ATMEGA_OTGCON_SRPSEL

| #define ATMEGA_OTGCON_SRPSEL (1 << 3) |

Definition at line 151 of file atmegadci.h.

◆ ATMEGA_OTGCON_VBUSHWC

| #define ATMEGA_OTGCON_VBUSHWC (1 << 2) |

Definition at line 150 of file atmegadci.h.

◆ ATMEGA_OTGCON_VBUSREQ

| #define ATMEGA_OTGCON_VBUSREQ (1 << 1) |

Definition at line 149 of file atmegadci.h.

◆ ATMEGA_OTGCON_VBUSRQC

| #define ATMEGA_OTGCON_VBUSRQC (1 << 0) |

Definition at line 148 of file atmegadci.h.

◆ ATMEGA_OTGINT

| #define ATMEGA_OTGINT 0xDF |

Definition at line 145 of file atmegadci.h.

◆ ATMEGA_OTGTCON

| #define ATMEGA_OTGTCON 0xF9 |

Definition at line 39 of file atmegadci.h.

◆ ATMEGA_OTGTCON_PAGE

| #define ATMEGA_OTGTCON_PAGE | ( | x | ) | ((x) << 5) |

Definition at line 41 of file atmegadci.h.

◆ ATMEGA_OTGTCON_VALUE

| #define ATMEGA_OTGTCON_VALUE | ( | x | ) | ((x) << 0) |

Definition at line 40 of file atmegadci.h.

◆ ATMEGA_READ_1

Definition at line 176 of file atmegadci.h.

◆ ATMEGA_READ_MULTI_1

| #define ATMEGA_READ_MULTI_1 | ( | sc, | |

| reg, | |||

| ptr, | |||

| len | |||

| ) | bus_space_read_multi_1((sc)->sc_io_tag, (sc)->sc_io_hdl, reg, ptr, len) |

Definition at line 185 of file atmegadci.h.

◆ ATMEGA_UDADDR

| #define ATMEGA_UDADDR 0xE3 /* USB address */ |

Definition at line 117 of file atmegadci.h.

◆ ATMEGA_UDADDR_ADDEN

| #define ATMEGA_UDADDR_ADDEN (1 << 7) |

Definition at line 119 of file atmegadci.h.

◆ ATMEGA_UDADDR_MASK

| #define ATMEGA_UDADDR_MASK 0x7F |

Definition at line 118 of file atmegadci.h.

◆ ATMEGA_UDCON

| #define ATMEGA_UDCON 0xE0 /* USB device connection register */ |

Definition at line 139 of file atmegadci.h.

◆ ATMEGA_UDCON_DETACH

| #define ATMEGA_UDCON_DETACH (1 << 0) |

Definition at line 140 of file atmegadci.h.

◆ ATMEGA_UDCON_LSM

| #define ATMEGA_UDCON_LSM (1 << 2) |

Definition at line 142 of file atmegadci.h.

◆ ATMEGA_UDCON_RMWKUP

| #define ATMEGA_UDCON_RMWKUP (1 << 1) |

Definition at line 141 of file atmegadci.h.

◆ ATMEGA_UDCON_RSTCPU

| #define ATMEGA_UDCON_RSTCPU (1 << 3) |

Definition at line 143 of file atmegadci.h.

◆ ATMEGA_UDFNUMH

| #define ATMEGA_UDFNUMH 0xE5 /* frame number high */ |

Definition at line 109 of file atmegadci.h.

◆ ATMEGA_UDFNUMH_MASK

| #define ATMEGA_UDFNUMH_MASK 7 |

Definition at line 110 of file atmegadci.h.

◆ ATMEGA_UDFNUML

| #define ATMEGA_UDFNUML 0xE4 /* frame number low */ |

Definition at line 112 of file atmegadci.h.

◆ ATMEGA_UDFNUML_MASK

| #define ATMEGA_UDFNUML_MASK 0xFF |

Definition at line 113 of file atmegadci.h.

◆ ATMEGA_UDIEN

| #define ATMEGA_UDIEN 0xE2 /* USB device interrupt enable */ |

Definition at line 121 of file atmegadci.h.

◆ ATMEGA_UDINT

| #define ATMEGA_UDINT 0xE1 /* USB device interrupt status */ |

Definition at line 130 of file atmegadci.h.

◆ ATMEGA_UDINT_EORSME

| #define ATMEGA_UDINT_EORSME (1 << 5) |

Definition at line 127 of file atmegadci.h.

◆ ATMEGA_UDINT_EORSMI

| #define ATMEGA_UDINT_EORSMI (1 << 5) |

Definition at line 136 of file atmegadci.h.

◆ ATMEGA_UDINT_EORSTE

| #define ATMEGA_UDINT_EORSTE (1 << 3) |

Definition at line 125 of file atmegadci.h.

◆ ATMEGA_UDINT_EORSTI

| #define ATMEGA_UDINT_EORSTI (1 << 3) |

Definition at line 134 of file atmegadci.h.

◆ ATMEGA_UDINT_MSOFE

| #define ATMEGA_UDINT_MSOFE (1 << 1) |

Definition at line 123 of file atmegadci.h.

◆ ATMEGA_UDINT_MSOFI

| #define ATMEGA_UDINT_MSOFI (1 << 1) |

Definition at line 132 of file atmegadci.h.

◆ ATMEGA_UDINT_SOFE

| #define ATMEGA_UDINT_SOFE (1 << 2) |

Definition at line 124 of file atmegadci.h.

◆ ATMEGA_UDINT_SOFI

| #define ATMEGA_UDINT_SOFI (1 << 2) |

Definition at line 133 of file atmegadci.h.

◆ ATMEGA_UDINT_SUSPE

| #define ATMEGA_UDINT_SUSPE (1 << 0) |

Definition at line 122 of file atmegadci.h.

◆ ATMEGA_UDINT_SUSPI

| #define ATMEGA_UDINT_SUSPI (1 << 0) |

Definition at line 131 of file atmegadci.h.

◆ ATMEGA_UDINT_UPRSME

| #define ATMEGA_UDINT_UPRSME (1 << 6) |

Definition at line 128 of file atmegadci.h.

◆ ATMEGA_UDINT_UPRSMI

| #define ATMEGA_UDINT_UPRSMI (1 << 6) |

Definition at line 137 of file atmegadci.h.

◆ ATMEGA_UDINT_WAKEUPE

| #define ATMEGA_UDINT_WAKEUPE (1 << 4) |

Definition at line 126 of file atmegadci.h.

◆ ATMEGA_UDINT_WAKEUPI

| #define ATMEGA_UDINT_WAKEUPI (1 << 4) |

Definition at line 135 of file atmegadci.h.

◆ ATMEGA_UDMFN

| #define ATMEGA_UDMFN 0xE6 |

Definition at line 106 of file atmegadci.h.

◆ ATMEGA_UDMFN_FNCERR

| #define ATMEGA_UDMFN_FNCERR (1 << 4) |

Definition at line 107 of file atmegadci.h.

◆ ATMEGA_UEBCHX

| #define ATMEGA_UEBCHX 0xF3 /* FIFO byte count high */ |

Definition at line 46 of file atmegadci.h.

◆ ATMEGA_UEBCLX

| #define ATMEGA_UEBCLX 0xF2 /* FIFO byte count low */ |

Definition at line 47 of file atmegadci.h.

◆ ATMEGA_UECFG0X

| #define ATMEGA_UECFG0X 0xEC |

Definition at line 78 of file atmegadci.h.

◆ ATMEGA_UECFG0X_EPDIR

| #define ATMEGA_UECFG0X_EPDIR (1 << 0) /* endpoint direction */ |

Definition at line 79 of file atmegadci.h.

◆ ATMEGA_UECFG0X_EPTYPE0

| #define ATMEGA_UECFG0X_EPTYPE0 (0 << 6) |

Definition at line 80 of file atmegadci.h.

◆ ATMEGA_UECFG0X_EPTYPE1

| #define ATMEGA_UECFG0X_EPTYPE1 (1 << 6) |

Definition at line 81 of file atmegadci.h.

◆ ATMEGA_UECFG0X_EPTYPE2

| #define ATMEGA_UECFG0X_EPTYPE2 (2 << 6) |

Definition at line 82 of file atmegadci.h.

◆ ATMEGA_UECFG0X_EPTYPE3

| #define ATMEGA_UECFG0X_EPTYPE3 (3 << 6) |

Definition at line 83 of file atmegadci.h.

◆ ATMEGA_UECFG1X

Definition at line 70 of file atmegadci.h.

◆ ATMEGA_UECFG1X_ALLOC

| #define ATMEGA_UECFG1X_ALLOC (1 << 1) |

Definition at line 71 of file atmegadci.h.

◆ ATMEGA_UECFG1X_EPBK0

| #define ATMEGA_UECFG1X_EPBK0 (0 << 2) |

Definition at line 72 of file atmegadci.h.

◆ ATMEGA_UECFG1X_EPBK1

| #define ATMEGA_UECFG1X_EPBK1 (1 << 2) |

Definition at line 73 of file atmegadci.h.

◆ ATMEGA_UECFG1X_EPBK2

| #define ATMEGA_UECFG1X_EPBK2 (2 << 2) |

Definition at line 74 of file atmegadci.h.

◆ ATMEGA_UECFG1X_EPBK3

| #define ATMEGA_UECFG1X_EPBK3 (3 << 2) |

Definition at line 75 of file atmegadci.h.

◆ ATMEGA_UECFG1X_EPSIZE

Definition at line 76 of file atmegadci.h.

◆ ATMEGA_UECONX

| #define ATMEGA_UECONX 0xEB |

Definition at line 85 of file atmegadci.h.

◆ ATMEGA_UECONX_EPEN

| #define ATMEGA_UECONX_EPEN (1 << 0) |

Definition at line 86 of file atmegadci.h.

◆ ATMEGA_UECONX_RSTDT

| #define ATMEGA_UECONX_RSTDT (1 << 3) |

Definition at line 87 of file atmegadci.h.

◆ ATMEGA_UECONX_STALLRQ

| #define ATMEGA_UECONX_STALLRQ (1 << 5) /* stall request set */ |

Definition at line 89 of file atmegadci.h.

◆ ATMEGA_UECONX_STALLRQC

| #define ATMEGA_UECONX_STALLRQC (1 << 4) /* stall request clear */ |

Definition at line 88 of file atmegadci.h.

◆ ATMEGA_UEDATX

| #define ATMEGA_UEDATX 0xF1 /* FIFO data */ |

Definition at line 48 of file atmegadci.h.

◆ ATMEGA_UEIENX

| #define ATMEGA_UEIENX 0xF0 /* interrupt enable register */ |

Definition at line 50 of file atmegadci.h.

◆ ATMEGA_UEIENX_FLERRE

| #define ATMEGA_UEIENX_FLERRE (1 << 7) |

Definition at line 57 of file atmegadci.h.

◆ ATMEGA_UEIENX_NAKINE

| #define ATMEGA_UEIENX_NAKINE (1 << 6) |

Definition at line 56 of file atmegadci.h.

◆ ATMEGA_UEIENX_NAKOUTE

| #define ATMEGA_UEIENX_NAKOUTE (1 << 4) |

Definition at line 55 of file atmegadci.h.

◆ ATMEGA_UEIENX_RXOUTE

| #define ATMEGA_UEIENX_RXOUTE (1 << 2) |

Definition at line 53 of file atmegadci.h.

◆ ATMEGA_UEIENX_RXSTPE

| #define ATMEGA_UEIENX_RXSTPE (1 << 3) /* received SETUP packet */ |

Definition at line 54 of file atmegadci.h.

◆ ATMEGA_UEIENX_STALLEDE

| #define ATMEGA_UEIENX_STALLEDE (1 << 1) |

Definition at line 52 of file atmegadci.h.

◆ ATMEGA_UEIENX_TXINE

| #define ATMEGA_UEIENX_TXINE (1 << 0) |

Definition at line 51 of file atmegadci.h.

◆ ATMEGA_UEINT

| #define ATMEGA_UEINT 0xF4 |

Definition at line 43 of file atmegadci.h.

◆ ATMEGA_UEINT_MASK

Definition at line 44 of file atmegadci.h.

◆ ATMEGA_UEINTX

| #define ATMEGA_UEINTX 0xE8 /* interrupt register */ |

Definition at line 96 of file atmegadci.h.

◆ ATMEGA_UEINTX_FIFOCON

| #define ATMEGA_UEINTX_FIFOCON (1 << 7) |

Definition at line 104 of file atmegadci.h.

◆ ATMEGA_UEINTX_NAKINI

| #define ATMEGA_UEINTX_NAKINI (1 << 6) |

Definition at line 103 of file atmegadci.h.

◆ ATMEGA_UEINTX_NAKOUTI

| #define ATMEGA_UEINTX_NAKOUTI (1 << 4) |

Definition at line 101 of file atmegadci.h.

◆ ATMEGA_UEINTX_RWAL

| #define ATMEGA_UEINTX_RWAL (1 << 5) |

Definition at line 102 of file atmegadci.h.

◆ ATMEGA_UEINTX_RXOUTI

| #define ATMEGA_UEINTX_RXOUTI (1 << 2) |

Definition at line 99 of file atmegadci.h.

◆ ATMEGA_UEINTX_RXSTPI

| #define ATMEGA_UEINTX_RXSTPI (1 << 3) /* received setup packet */ |

Definition at line 100 of file atmegadci.h.

◆ ATMEGA_UEINTX_STALLEDI

| #define ATMEGA_UEINTX_STALLEDI (1 << 1) |

Definition at line 98 of file atmegadci.h.

◆ ATMEGA_UEINTX_TXINI

| #define ATMEGA_UEINTX_TXINI (1 << 0) |

Definition at line 97 of file atmegadci.h.

◆ ATMEGA_UENUM

| #define ATMEGA_UENUM 0xE9 /* endpoint number */ |

Definition at line 94 of file atmegadci.h.

◆ ATMEGA_UERST

| #define ATMEGA_UERST 0xEA /* endpoint reset register */ |

Definition at line 91 of file atmegadci.h.

◆ ATMEGA_UERST_MASK

Definition at line 92 of file atmegadci.h.

◆ ATMEGA_UESTA0X

| #define ATMEGA_UESTA0X 0xEE |

Definition at line 63 of file atmegadci.h.

◆ ATMEGA_UESTA0X_CFGOK

| #define ATMEGA_UESTA0X_CFGOK (1 << 7) |

Definition at line 68 of file atmegadci.h.

◆ ATMEGA_UESTA0X_DTSEQ

| #define ATMEGA_UESTA0X_DTSEQ (3 << 2) |

Definition at line 65 of file atmegadci.h.

◆ ATMEGA_UESTA0X_NBUSYBK

| #define ATMEGA_UESTA0X_NBUSYBK (3 << 0) |

Definition at line 64 of file atmegadci.h.

◆ ATMEGA_UESTA0X_OVERFI

| #define ATMEGA_UESTA0X_OVERFI (1 << 6) /* overflow */ |

Definition at line 67 of file atmegadci.h.

◆ ATMEGA_UESTA0X_UNDERFI

| #define ATMEGA_UESTA0X_UNDERFI (1 << 5) /* underflow */ |

Definition at line 66 of file atmegadci.h.

◆ ATMEGA_UESTA1X

| #define ATMEGA_UESTA1X 0xEF |

Definition at line 59 of file atmegadci.h.

◆ ATMEGA_UESTA1X_CTRLDIR

| #define ATMEGA_UESTA1X_CTRLDIR (1 << 2) /* control endpoint direction */ |

Definition at line 61 of file atmegadci.h.

◆ ATMEGA_UESTA1X_CURRBK

| #define ATMEGA_UESTA1X_CURRBK (3 << 0) /* current bank */ |

Definition at line 60 of file atmegadci.h.

◆ ATMEGA_UHWCON

| #define ATMEGA_UHWCON 0xD7 |

Definition at line 170 of file atmegadci.h.

◆ ATMEGA_UHWCON_UIDE

| #define ATMEGA_UHWCON_UIDE (1 << 6) |

Definition at line 173 of file atmegadci.h.

◆ ATMEGA_UHWCON_UIMOD

| #define ATMEGA_UHWCON_UIMOD (1 << 7) |

Definition at line 174 of file atmegadci.h.

◆ ATMEGA_UHWCON_UVCONE

| #define ATMEGA_UHWCON_UVCONE (1 << 4) |

Definition at line 172 of file atmegadci.h.

◆ ATMEGA_UHWCON_UVREGE

| #define ATMEGA_UHWCON_UVREGE (1 << 0) |

Definition at line 171 of file atmegadci.h.

◆ ATMEGA_USBCON

| #define ATMEGA_USBCON 0xD8 |

Definition at line 163 of file atmegadci.h.

◆ ATMEGA_USBCON_FRZCLK

| #define ATMEGA_USBCON_FRZCLK (1 << 5) |

Definition at line 167 of file atmegadci.h.

◆ ATMEGA_USBCON_IDE

| #define ATMEGA_USBCON_IDE (1 << 1) |

Definition at line 165 of file atmegadci.h.

◆ ATMEGA_USBCON_OTGPADE

| #define ATMEGA_USBCON_OTGPADE (1 << 4) |

Definition at line 166 of file atmegadci.h.

◆ ATMEGA_USBCON_USBE

| #define ATMEGA_USBCON_USBE (1 << 7) |

Definition at line 168 of file atmegadci.h.

◆ ATMEGA_USBCON_VBUSTE

| #define ATMEGA_USBCON_VBUSTE (1 << 0) |

Definition at line 164 of file atmegadci.h.

◆ ATMEGA_USBINT

| #define ATMEGA_USBINT 0xDA |

Definition at line 155 of file atmegadci.h.

◆ ATMEGA_USBINT_IDI

| #define ATMEGA_USBINT_IDI (1 << 1) /* USB ID interrupt */ |

Definition at line 157 of file atmegadci.h.

◆ ATMEGA_USBINT_VBUSTI

| #define ATMEGA_USBINT_VBUSTI (1 << 0) /* USB VBUS interrupt */ |

Definition at line 156 of file atmegadci.h.

◆ ATMEGA_USBSTA

| #define ATMEGA_USBSTA 0xD9 |

Definition at line 159 of file atmegadci.h.

◆ ATMEGA_USBSTA_ID

| #define ATMEGA_USBSTA_ID (1 << 1) |

Definition at line 161 of file atmegadci.h.

◆ ATMEGA_USBSTA_VBUS

| #define ATMEGA_USBSTA_VBUS (1 << 0) |

Definition at line 160 of file atmegadci.h.

◆ ATMEGA_WRITE_1

| #define ATMEGA_WRITE_1 | ( | sc, | |

| reg, | |||

| data | |||

| ) | bus_space_write_1((sc)->sc_io_tag, (sc)->sc_io_hdl, reg, data) |

Definition at line 179 of file atmegadci.h.

◆ ATMEGA_WRITE_MULTI_1

| #define ATMEGA_WRITE_MULTI_1 | ( | sc, | |

| reg, | |||

| ptr, | |||

| len | |||

| ) | bus_space_write_multi_1((sc)->sc_io_tag, (sc)->sc_io_hdl, reg, ptr, len) |

Definition at line 182 of file atmegadci.h.

Typedef Documentation

◆ atmegadci_clocks_t

| typedef void() atmegadci_clocks_t(struct usb_bus *) |

Definition at line 196 of file atmegadci.h.

◆ atmegadci_cmd_t

| typedef uint8_t() atmegadci_cmd_t(struct atmegadci_td *td) |

Definition at line 195 of file atmegadci.h.

Function Documentation

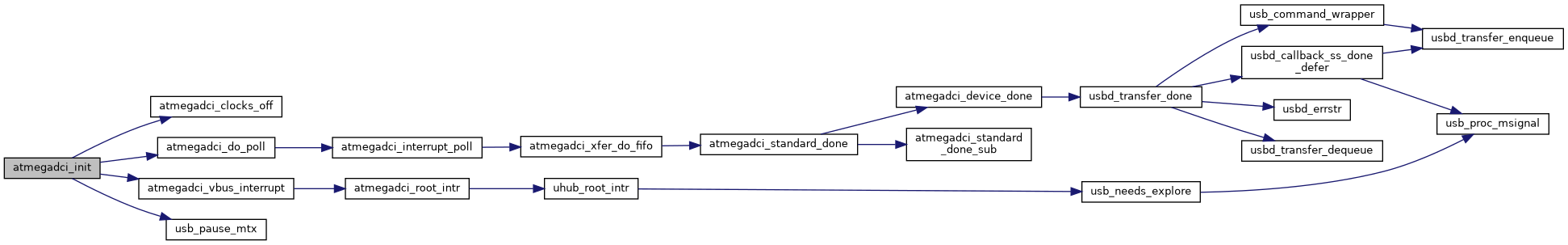

◆ atmegadci_init()

| usb_error_t atmegadci_init | ( | struct atmegadci_softc * | sc | ) |

Definition at line 1219 of file atmegadci.c.

References ATMEGA_EP_MAX, ATMEGA_READ_1, ATMEGA_UDCON, ATMEGA_UDCON_DETACH, ATMEGA_UDIEN, ATMEGA_UDINT_EORSTE, ATMEGA_UDINT_SUSPE, ATMEGA_UECONX, ATMEGA_UEIENX, ATMEGA_UENUM, ATMEGA_UERST, ATMEGA_UHWCON, ATMEGA_UHWCON_UIMOD, ATMEGA_UHWCON_UVREGE, ATMEGA_USBCON, ATMEGA_USBCON_FRZCLK, ATMEGA_USBCON_OTGPADE, ATMEGA_USBCON_USBE, ATMEGA_USBCON_VBUSTE, ATMEGA_USBSTA, ATMEGA_USBSTA_VBUS, ATMEGA_WRITE_1, atmegadci_bus_methods, atmegadci_clocks_off(), atmegadci_do_poll(), atmegadci_vbus_interrupt(), usb_bus::bus_mtx, DPRINTF, usb_bus::methods, n, atmegadci_softc::sc_bus, atmegadci_softc::sc_clocks_on, USB_BUS_LOCK, USB_BUS_UNLOCK, usb_pause_mtx(), USB_REV_1_1, and usb_bus::usbrev.

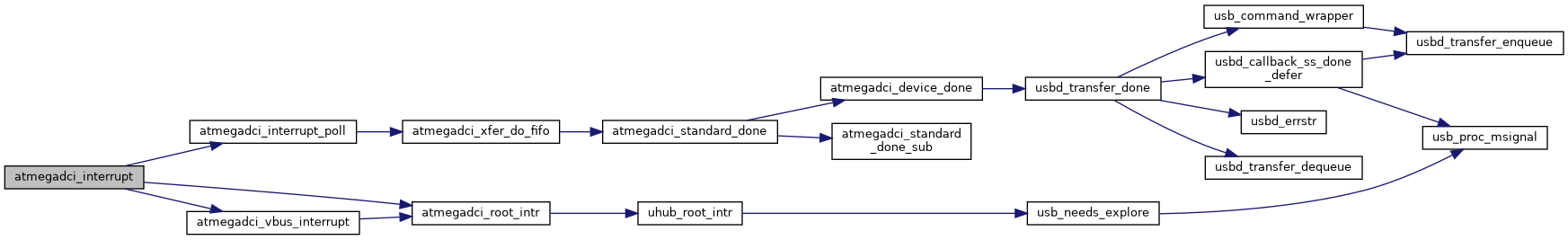

◆ atmegadci_interrupt()

| void atmegadci_interrupt | ( | struct atmegadci_softc * | sc | ) |

Definition at line 656 of file atmegadci.c.

References ATMEGA_READ_1, ATMEGA_UDIEN, ATMEGA_UDINT, ATMEGA_UDINT_EORSTE, ATMEGA_UDINT_EORSTI, ATMEGA_UDINT_SUSPE, ATMEGA_UDINT_SUSPI, ATMEGA_UDINT_WAKEUPE, ATMEGA_UDINT_WAKEUPI, ATMEGA_UEINT, ATMEGA_USBINT, ATMEGA_USBINT_VBUSTI, ATMEGA_USBSTA, ATMEGA_USBSTA_VBUS, ATMEGA_WRITE_1, atmegadci_interrupt_poll(), atmegadci_root_intr(), atmegadci_vbus_interrupt(), atmegadci_flags::change_connect, atmegadci_flags::change_suspend, atmegadci_softc::sc_bus, atmegadci_softc::sc_flags, status, atmegadci_flags::status_bus_reset, atmegadci_flags::status_suspend, USB_BUS_LOCK, and USB_BUS_UNLOCK.

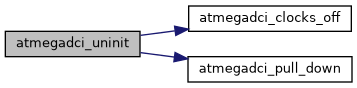

◆ atmegadci_uninit()

| void atmegadci_uninit | ( | struct atmegadci_softc * | sc | ) |

Definition at line 1310 of file atmegadci.c.

References ATMEGA_EP_MAX, ATMEGA_UDIEN, ATMEGA_UERST, ATMEGA_UHWCON, ATMEGA_WRITE_1, atmegadci_clocks_off(), atmegadci_pull_down(), atmegadci_flags::change_connect, atmegadci_flags::change_suspend, atmegadci_flags::port_powered, atmegadci_softc::sc_bus, atmegadci_softc::sc_clocks_on, atmegadci_softc::sc_flags, atmegadci_flags::status_bus_reset, atmegadci_flags::status_suspend, atmegadci_flags::status_vbus, USB_BUS_LOCK, and USB_BUS_UNLOCK.

Referenced by atmegadci_set_hw_power_sleep().

Variable Documentation

◆ __packed

| struct zyd_tx_radiotap_header __packed |