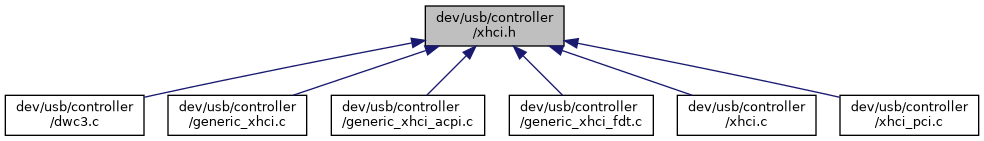

Go to the source code of this file.

Data Structures | |

| struct | xhci_dev_ctx_addr |

| struct | xhci_slot_ctx |

| struct | xhci_slot_ctx64 |

| struct | xhci_endp_ctx |

| struct | xhci_endp_ctx64 |

| struct | xhci_input_ctx |

| struct | xhci_input_ctx64 |

| struct | xhci_input_dev_ctx |

| struct | xhci_input_dev_ctx64 |

| struct | xhci_dev_ctx |

| struct | xhci_dev_ctx64 |

| struct | xhci_stream_ctx |

| struct | xhci_trb |

| struct | xhci_dev_endpoint_trbs |

| struct | xhci_td |

| struct | xhci_command |

| struct | xhci_event_ring_seg |

| struct | xhci_hw_root |

| struct | xhci_endpoint_ext |

| struct | xhci_hw_dev |

| struct | xhci_hw_softc |

| struct | xhci_config_desc |

| struct | xhci_bos_desc |

| union | xhci_hub_desc |

| struct | xhci_softc |

Typedefs | |

| typedef int() | xhci_port_route_t(device_t, uint32_t, uint32_t) |

Enumerations | |

| enum | { XHCI_ST_DISABLED , XHCI_ST_ENABLED , XHCI_ST_DEFAULT , XHCI_ST_ADDRESSED , XHCI_ST_CONFIGURED , XHCI_ST_MAX } |

Functions | |

| struct xhci_dev_ctx | __aligned (XHCI_DEV_CTX_ALIGN) |

| struct xhci_trb | __aligned (4) |

| struct xhci_td | __aligned (XHCI_TRB_ALIGN) |

| CTASSERT (sizeof(struct xhci_hw_root)==XHCI_PAGE_SIZE) | |

| uint8_t | xhci_use_polling (void) |

| usb_error_t | xhci_halt_controller (struct xhci_softc *) |

| usb_error_t | xhci_reset_controller (struct xhci_softc *) |

| usb_error_t | xhci_init (struct xhci_softc *, device_t, uint8_t) |

| usb_error_t | xhci_start_controller (struct xhci_softc *) |

| void | xhci_interrupt (struct xhci_softc *) |

| void | xhci_uninit (struct xhci_softc *) |

| int | xhci_pci_attach (device_t) |

| DECLARE_CLASS (xhci_pci_driver) | |

Variables | |

| volatile uint64_t | dummy |

| struct xhci_slot_ctx | ctx_slot |

| struct xhci_endp_ctx | ctx_ep [XHCI_MAX_ENDPOINTS - 1] |

| struct xhci_stream_ctx | __aligned |

| volatile uint64_t | qwTrb0 |

| volatile uint32_t | dwTrb2 |

| volatile uint32_t | dwTrb3 |

| struct xhci_trb | td_trb [XHCI_TD_PAGE_NBUF+1] |

| uint64_t | td_self |

| struct xhci_td * | next |

| struct xhci_td * | alt_next |

| struct xhci_td * | obj_next |

| struct usb_page_cache * | page_cache |

| uint32_t | len |

| uint32_t | remainder |

| uint8_t | ntrb |

| uint8_t | status |

| struct xhci_config_desc | __packed |

Macro Definition Documentation

◆ XHCI_CMD_ASSERT_LOCKED

| #define XHCI_CMD_ASSERT_LOCKED | ( | sc | ) | sx_assert(&(sc)->sc_cmd_sx, SA_LOCKED) |

◆ XHCI_CMD_LOCK

◆ XHCI_CMD_RING_SEG_ALIGN

◆ XHCI_CMD_UNLOCK

◆ XHCI_DEV_CTX_ADDR_ALIGN

◆ XHCI_DEV_CTX_ALIGN

◆ XHCI_ENDP_CTX_ALIGN

◆ XHCI_EPCTX_0_EPSTATE_DISABLED

◆ XHCI_EPCTX_0_EPSTATE_ERROR

◆ XHCI_EPCTX_0_EPSTATE_GET

◆ XHCI_EPCTX_0_EPSTATE_HALTED

◆ XHCI_EPCTX_0_EPSTATE_RESERVED_5

◆ XHCI_EPCTX_0_EPSTATE_RESERVED_6

◆ XHCI_EPCTX_0_EPSTATE_RESERVED_7

◆ XHCI_EPCTX_0_EPSTATE_RUNNING

◆ XHCI_EPCTX_0_EPSTATE_SET

◆ XHCI_EPCTX_0_EPSTATE_STOPPED

◆ XHCI_EPCTX_0_IVAL_GET

◆ XHCI_EPCTX_0_IVAL_SET

◆ XHCI_EPCTX_0_LSA_GET

◆ XHCI_EPCTX_0_LSA_SET

◆ XHCI_EPCTX_0_MAXP_STREAMS_GET

| #define XHCI_EPCTX_0_MAXP_STREAMS_GET | ( | x | ) | (((x) >> 10) & 0x1F) |

◆ XHCI_EPCTX_0_MAXP_STREAMS_SET

| #define XHCI_EPCTX_0_MAXP_STREAMS_SET | ( | x | ) | (((x) & 0x1F) << 10) |

◆ XHCI_EPCTX_0_MULT_GET

◆ XHCI_EPCTX_0_MULT_SET

◆ XHCI_EPCTX_1_CERR_GET

◆ XHCI_EPCTX_1_CERR_SET

◆ XHCI_EPCTX_1_EPTYPE_GET

◆ XHCI_EPCTX_1_EPTYPE_SET

◆ XHCI_EPCTX_1_HID_GET

◆ XHCI_EPCTX_1_HID_SET

◆ XHCI_EPCTX_1_MAXB_GET

◆ XHCI_EPCTX_1_MAXB_SET

◆ XHCI_EPCTX_1_MAXP_SIZE_GET

| #define XHCI_EPCTX_1_MAXP_SIZE_GET | ( | x | ) | (((x) >> 16) & 0xFFFF) |

◆ XHCI_EPCTX_1_MAXP_SIZE_SET

| #define XHCI_EPCTX_1_MAXP_SIZE_SET | ( | x | ) | (((x) & 0xFFFF) << 16) |

◆ XHCI_EPCTX_2_DCS_GET

◆ XHCI_EPCTX_2_DCS_SET

◆ XHCI_EPCTX_2_TR_DQ_PTR_MASK

◆ XHCI_EPCTX_4_AVG_TRB_LEN_GET

◆ XHCI_EPCTX_4_AVG_TRB_LEN_SET

◆ XHCI_EPCTX_4_MAX_ESIT_PAYLOAD_GET

| #define XHCI_EPCTX_4_MAX_ESIT_PAYLOAD_GET | ( | x | ) | (((x) >> 16) & 0xFFFF) |

◆ XHCI_EPCTX_4_MAX_ESIT_PAYLOAD_SET

| #define XHCI_EPCTX_4_MAX_ESIT_PAYLOAD_SET | ( | x | ) | (((x) & 0xFFFF) << 16) |

◆ XHCI_EPNO2EPID

◆ XHCI_EVENT_RING_SEG_ALIGN

◆ XHCI_INCTX_0_DROP_MASK

◆ XHCI_INCTX_1_ADD_MASK

◆ XHCI_INCTX_NON_CTRL_MASK

◆ XHCI_INPUT_CTX_ALIGN

◆ XHCI_MAX_COMMANDS

◆ XHCI_MAX_DEVICES

| #define XHCI_MAX_DEVICES MIN(USB_MAX_DEVICES, 128) |

◆ XHCI_MAX_ENDPOINTS

◆ XHCI_MAX_EVENTS

◆ XHCI_MAX_RSEG

◆ XHCI_MAX_SCRATCHPADS

| #define XHCI_MAX_SCRATCHPADS 256 /* theoretical max is 1023 */ |

◆ XHCI_MAX_TRANSFERS

◆ XHCI_PAGE_SIZE

◆ XHCI_SCRATCH_BUF_ARRAY_ALIGN

◆ XHCI_SCRATCH_BUFFER_ALIGN

| #define XHCI_SCRATCH_BUFFER_ALIGN USB_PAGE_SIZE |

◆ XHCI_SCTX_0_CTX_NUM_GET

◆ XHCI_SCTX_0_CTX_NUM_SET

◆ XHCI_SCTX_0_DCS_GET

◆ XHCI_SCTX_0_DCS_SET

◆ XHCI_SCTX_0_HUB_GET

◆ XHCI_SCTX_0_HUB_SET

◆ XHCI_SCTX_0_MTT_GET

◆ XHCI_SCTX_0_MTT_SET

◆ XHCI_SCTX_0_ROUTE_GET

◆ XHCI_SCTX_0_ROUTE_SET

◆ XHCI_SCTX_0_SCT_GET

◆ XHCI_SCTX_0_SCT_PRIM_SSA_128

◆ XHCI_SCTX_0_SCT_PRIM_SSA_16

◆ XHCI_SCTX_0_SCT_PRIM_SSA_256

◆ XHCI_SCTX_0_SCT_PRIM_SSA_32

◆ XHCI_SCTX_0_SCT_PRIM_SSA_64

◆ XHCI_SCTX_0_SCT_PRIM_SSA_8

◆ XHCI_SCTX_0_SCT_PRIM_TR_RING

◆ XHCI_SCTX_0_SCT_SEC_TR_RING

◆ XHCI_SCTX_0_SCT_SET

◆ XHCI_SCTX_0_SPEED_GET

◆ XHCI_SCTX_0_SPEED_SET

◆ XHCI_SCTX_0_TR_DQ_PTR_MASK

◆ XHCI_SCTX_1_MAX_EL_GET

◆ XHCI_SCTX_1_MAX_EL_SET

◆ XHCI_SCTX_1_NUM_PORTS_GET

◆ XHCI_SCTX_1_NUM_PORTS_SET

◆ XHCI_SCTX_1_RH_PORT_GET

◆ XHCI_SCTX_1_RH_PORT_SET

◆ XHCI_SCTX_2_IRQ_TARGET_GET

| #define XHCI_SCTX_2_IRQ_TARGET_GET | ( | x | ) | (((x) >> 22) & 0x3FF) |

◆ XHCI_SCTX_2_IRQ_TARGET_SET

| #define XHCI_SCTX_2_IRQ_TARGET_SET | ( | x | ) | (((x) & 0x3FF) << 22) |

◆ XHCI_SCTX_2_TT_HUB_SID_GET

◆ XHCI_SCTX_2_TT_HUB_SID_SET

◆ XHCI_SCTX_2_TT_PORT_NUM_GET

◆ XHCI_SCTX_2_TT_PORT_NUM_SET

◆ XHCI_SCTX_2_TT_THINK_TIME_GET

| #define XHCI_SCTX_2_TT_THINK_TIME_GET | ( | x | ) | (((x) >> 16) & 0x3) |

◆ XHCI_SCTX_2_TT_THINK_TIME_SET

| #define XHCI_SCTX_2_TT_THINK_TIME_SET | ( | x | ) | (((x) & 0x3) << 16) |

◆ XHCI_SCTX_3_DEV_ADDR_GET

◆ XHCI_SCTX_3_DEV_ADDR_SET

◆ XHCI_SCTX_3_SLOT_STATE_GET

◆ XHCI_SCTX_3_SLOT_STATE_SET

◆ XHCI_SLOT_CTX_ALIGN

◆ XHCI_STREAM_CTX_ALIGN

◆ XHCI_TD_ALIGN

◆ XHCI_TD_PAGE_NBUF

| #define XHCI_TD_PAGE_NBUF (((XHCI_TD_PAYLOAD_MAX + XHCI_TD_PAGE_SIZE - 1) / XHCI_TD_PAGE_SIZE) + 1) |

◆ XHCI_TD_PAGE_SIZE

| #define XHCI_TD_PAGE_SIZE ((USB_PAGE_SIZE < XHCI_TD_PAYLOAD_MAX) ? USB_PAGE_SIZE : XHCI_TD_PAYLOAD_MAX) |

◆ XHCI_TD_PAYLOAD_MAX

◆ XHCI_TRANS_RING_SEG_ALIGN

◆ XHCI_TRB_0_DIR_IN_MASK

◆ XHCI_TRB_0_WLENGTH_MASK

◆ XHCI_TRB_2_BYTES_GET

◆ XHCI_TRB_2_BYTES_SET

◆ XHCI_TRB_2_ERROR_GET

◆ XHCI_TRB_2_ERROR_SET

◆ XHCI_TRB_2_IRQ_GET

◆ XHCI_TRB_2_IRQ_SET

◆ XHCI_TRB_2_REM_GET

◆ XHCI_TRB_2_REM_SET

◆ XHCI_TRB_2_STREAM_GET

◆ XHCI_TRB_2_STREAM_SET

◆ XHCI_TRB_2_TDSZ_GET

◆ XHCI_TRB_2_TDSZ_SET

◆ XHCI_TRB_3_BEI_BIT

◆ XHCI_TRB_3_BSR_BIT

◆ XHCI_TRB_3_CHAIN_BIT

◆ XHCI_TRB_3_CYCLE_BIT

◆ XHCI_TRB_3_DCEP_BIT

◆ XHCI_TRB_3_DIR_IN

◆ XHCI_TRB_3_ENT_BIT

◆ XHCI_TRB_3_EP_GET

◆ XHCI_TRB_3_EP_SET

◆ XHCI_TRB_3_FRID_GET

◆ XHCI_TRB_3_FRID_SET

◆ XHCI_TRB_3_IDT_BIT

◆ XHCI_TRB_3_IOC_BIT

◆ XHCI_TRB_3_ISO_SIA_BIT

◆ XHCI_TRB_3_ISP_BIT

◆ XHCI_TRB_3_NSNOOP_BIT

◆ XHCI_TRB_3_PRSV_BIT

◆ XHCI_TRB_3_SLOT_GET

◆ XHCI_TRB_3_SLOT_SET

◆ XHCI_TRB_3_SUSP_EP_BIT

◆ XHCI_TRB_3_TBC_GET

◆ XHCI_TRB_3_TBC_SET

◆ XHCI_TRB_3_TC_BIT

◆ XHCI_TRB_3_TLBPC_GET

◆ XHCI_TRB_3_TLBPC_SET

◆ XHCI_TRB_3_TRT_IN

◆ XHCI_TRB_3_TRT_MASK

◆ XHCI_TRB_3_TRT_NONE

◆ XHCI_TRB_3_TRT_OUT

◆ XHCI_TRB_3_TYPE_GET

◆ XHCI_TRB_3_TYPE_SET

◆ XHCI_TRB_ALIGN

◆ XHCI_TRB_ERROR_BABBLE

◆ XHCI_TRB_ERROR_BAD_MELAT

◆ XHCI_TRB_ERROR_BANDWIDTH

◆ XHCI_TRB_ERROR_BW_OVERRUN

◆ XHCI_TRB_ERROR_CMD_ABORTED

◆ XHCI_TRB_ERROR_CMD_RING_STOP

◆ XHCI_TRB_ERROR_CONTEXT_STATE

◆ XHCI_TRB_ERROR_DATA_BUF

◆ XHCI_TRB_ERROR_ENDP_NOT_ON

◆ XHCI_TRB_ERROR_EV_RING_FULL

◆ XHCI_TRB_ERROR_EVENT_LOST

◆ XHCI_TRB_ERROR_INCOMPAT_DEV

◆ XHCI_TRB_ERROR_INVALID

◆ XHCI_TRB_ERROR_INVALID_SID

◆ XHCI_TRB_ERROR_ISOC_OVERRUN

◆ XHCI_TRB_ERROR_LENGTH

◆ XHCI_TRB_ERROR_MISSED_SERVICE

◆ XHCI_TRB_ERROR_NO_PING_RESP

◆ XHCI_TRB_ERROR_NO_SLOTS

◆ XHCI_TRB_ERROR_PARAMETER

◆ XHCI_TRB_ERROR_RESOURCE

◆ XHCI_TRB_ERROR_RING_OVERRUN

◆ XHCI_TRB_ERROR_RING_UNDERRUN

◆ XHCI_TRB_ERROR_SEC_BW

◆ XHCI_TRB_ERROR_SHORT_PKT

◆ XHCI_TRB_ERROR_SLOT_NOT_ON

◆ XHCI_TRB_ERROR_SPLIT_XACT

◆ XHCI_TRB_ERROR_STALL

◆ XHCI_TRB_ERROR_STOPPED

◆ XHCI_TRB_ERROR_STREAM_TYPE

◆ XHCI_TRB_ERROR_SUCCESS

◆ XHCI_TRB_ERROR_TRB

◆ XHCI_TRB_ERROR_UNDEFINED

◆ XHCI_TRB_ERROR_VF_RING_FULL

◆ XHCI_TRB_ERROR_XACT

◆ XHCI_TRB_EVENT_BW_REQUEST

◆ XHCI_TRB_EVENT_CMD_COMPLETE

◆ XHCI_TRB_EVENT_DEVICE_NOTIFY

◆ XHCI_TRB_EVENT_DOORBELL

◆ XHCI_TRB_EVENT_HOST_CTRL

◆ XHCI_TRB_EVENT_MFINDEX_WRAP

◆ XHCI_TRB_EVENT_PORT_STS_CHANGE

◆ XHCI_TRB_EVENT_TRANSFER

◆ XHCI_TRB_TYPE_ADDRESS_DEVICE

◆ XHCI_TRB_TYPE_CONFIGURE_EP

◆ XHCI_TRB_TYPE_DATA_STAGE

◆ XHCI_TRB_TYPE_DISABLE_SLOT

◆ XHCI_TRB_TYPE_ENABLE_SLOT

◆ XHCI_TRB_TYPE_EVALUATE_CTX

◆ XHCI_TRB_TYPE_EVENT_DATA

◆ XHCI_TRB_TYPE_FORCE_EVENT

◆ XHCI_TRB_TYPE_FORCE_HEADER

◆ XHCI_TRB_TYPE_GET_PORT_BW

◆ XHCI_TRB_TYPE_ISOCH

◆ XHCI_TRB_TYPE_LINK

◆ XHCI_TRB_TYPE_NEGOTIATE_BW

◆ XHCI_TRB_TYPE_NOOP

◆ XHCI_TRB_TYPE_NOOP_CMD

◆ XHCI_TRB_TYPE_NORMAL

◆ XHCI_TRB_TYPE_RESERVED

◆ XHCI_TRB_TYPE_RESET_DEVICE

◆ XHCI_TRB_TYPE_RESET_EP

◆ XHCI_TRB_TYPE_SET_LATENCY_TOL

◆ XHCI_TRB_TYPE_SET_TR_DEQUEUE

◆ XHCI_TRB_TYPE_SETUP_STAGE

◆ XHCI_TRB_TYPE_STATUS_STAGE

◆ XHCI_TRB_TYPE_STOP_EP

Typedef Documentation

◆ xhci_port_route_t

| typedef int() xhci_port_route_t(device_t, uint32_t, uint32_t) |

Enumeration Type Documentation

◆ anonymous enum

| anonymous enum |

Function Documentation

◆ __aligned() [1/3]

| struct xhci_trb __aligned | ( | 4 | ) |

◆ __aligned() [2/3]

| struct xhci_dev_ctx __aligned | ( | XHCI_DEV_CTX_ALIGN | ) |

◆ __aligned() [3/3]

| struct xhci_td __aligned | ( | XHCI_TRB_ALIGN | ) |

◆ CTASSERT()

| CTASSERT | ( | sizeof(struct xhci_hw_root) | = =XHCI_PAGE_SIZE | ) |

◆ DECLARE_CLASS()

| DECLARE_CLASS | ( | xhci_pci_driver | ) |

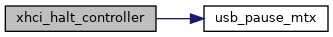

◆ xhci_halt_controller()

| usb_error_t xhci_halt_controller | ( | struct xhci_softc * | sc | ) |

Definition at line 454 of file xhci.c.

References DPRINTF, usb_bus::parent, xhci_softc::sc_bus, xhci_softc::sc_capa_off, xhci_softc::sc_door_off, xhci_softc::sc_oper_off, xhci_softc::sc_runt_off, USB_ERR_IOERROR, usb_pause_mtx(), XHCI_CAPLENGTH, XHCI_DBOFF, XHCI_RTSOFF, XHCI_STS_HCH, XHCI_USBCMD, XHCI_USBSTS, XREAD1, XREAD4, and XWRITE4.

Referenced by xhci_pci_attach(), xhci_pci_detach(), and xhci_set_hw_power_sleep().

◆ xhci_init()

| usb_error_t xhci_init | ( | struct xhci_softc * | sc, |

| device_t | self, | ||

| uint8_t | dma32 | ||

| ) |

Definition at line 511 of file xhci.c.

References usb_bus_msg::bus, usb_bus::control_ep_quirk, usb_bus::devices, usb_bus::devices_max, usb_bus::dma_bits, DPRINTF, usb_bus_msg::hdr, usb_bus::methods, usb_bus::parent, usb_proc_msg::pm_callback, xhci_softc::sc_bus, xhci_softc::sc_capa_off, xhci_softc::sc_cmd_cv, xhci_softc::sc_cmd_sx, xhci_softc::sc_command_ccs, xhci_softc::sc_config_msg, xhci_softc::sc_ctx_is_64_byte, xhci_softc::sc_devices, xhci_softc::sc_door_off, xhci_softc::sc_erst_max, xhci_softc::sc_event_ccs, xhci_softc::sc_exit_lat_max, xhci_softc::sc_imod_default, xhci_softc::sc_ist, xhci_softc::sc_noport, xhci_softc::sc_noscratch, xhci_softc::sc_noslot, xhci_softc::sc_oper_off, xhci_softc::sc_runt_off, usb_bus_mem_alloc_all(), USB_GET_DMA_TAG, USB_REV_3_0, usb_bus::usbrev, xhci_bus_methods, XHCI_CAPLENGTH, xhci_configure_msg, XHCI_DBOFF, XHCI_HCIVERSION, XHCI_HCS0_AC64, XHCI_HCS0_CSZ, XHCI_HCS1_DEVSLOT_MAX, XHCI_HCS1_N_PORTS, XHCI_HCS2_ERST_MAX, XHCI_HCS2_IST, XHCI_HCS2_SPB_MAX, XHCI_HCS3_U1_DEL, XHCI_HCS3_U2_DEL, XHCI_HCSPARAMS0, XHCI_HCSPARAMS1, XHCI_HCSPARAMS2, XHCI_HCSPARAMS3, XHCI_IMOD_DEFAULT, xhci_iterate_hw_softc(), XHCI_MAX_DEVICES, XHCI_MAX_RSEG, XHCI_MAX_SCRATCHPADS, XHCI_PAGESIZE, XHCI_PAGESIZE_4K, XHCI_RTSOFF, xhcictlquirk, xhcidma32, XREAD1, XREAD2, and XREAD4.

Referenced by generic_xhci_attach(), snps_dwc3_attach_xhci(), and xhci_pci_attach().

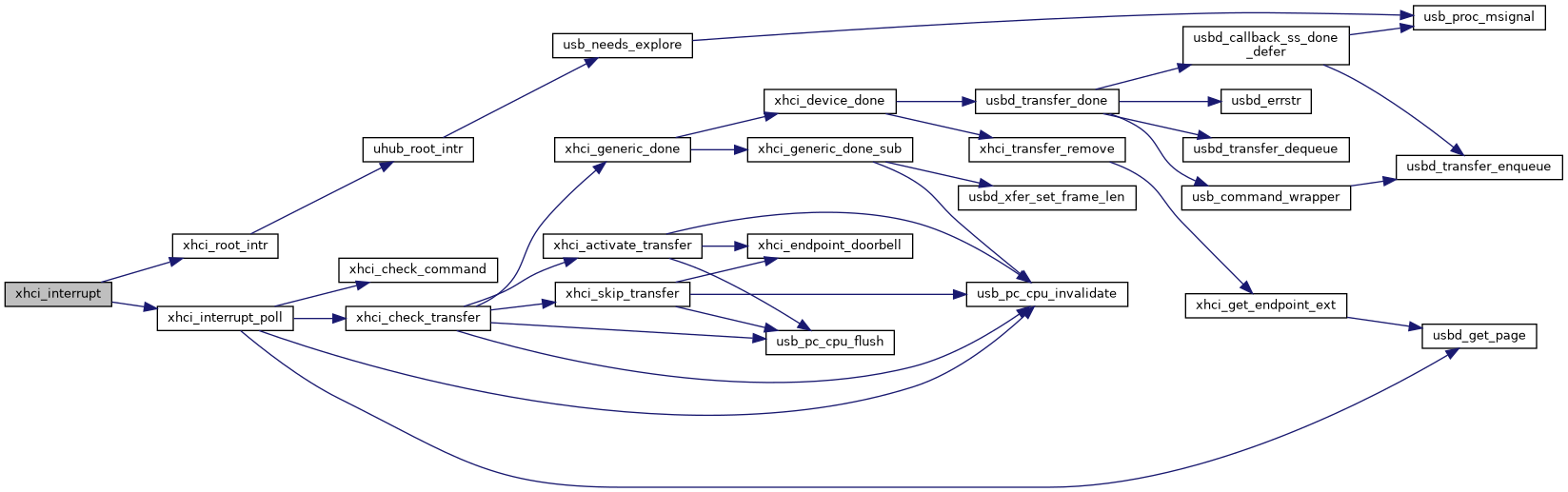

◆ xhci_interrupt()

| void xhci_interrupt | ( | struct xhci_softc * | sc | ) |

Definition at line 1603 of file xhci.c.

References xhci_softc::sc_bus, status, USB_BUS_LOCK, USB_BUS_UNLOCK, XHCI_IMAN, XHCI_IMAN_INTR_PEND, xhci_interrupt_poll(), xhci_root_intr(), XHCI_STS_HCE, XHCI_STS_HCH, XHCI_STS_HSE, XHCI_STS_PCD, XHCI_USBSTS, XREAD4, and XWRITE4.

Referenced by generic_xhci_attach(), snps_dwc3_attach_xhci(), xhci_interrupt_poll(), and xhci_pci_attach().

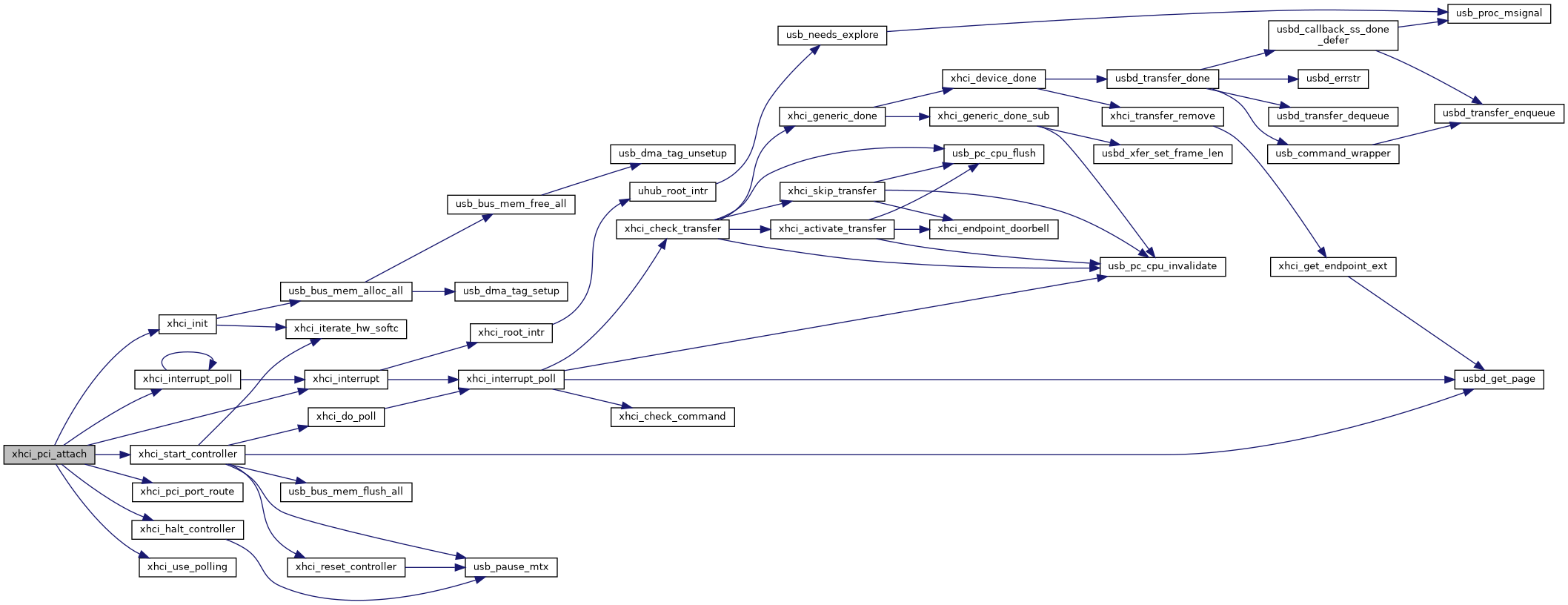

◆ xhci_pci_attach()

| int xhci_pci_attach | ( | device_t | self | ) |

Definition at line 271 of file xhci_pci.c.

References usb_bus::bdev, usb_bus::bus_mtx, count, error, PCI_XHCI_CBMEM, PCI_XHCI_VENDORID_AMD, PCI_XHCI_VENDORID_INTEL, rid, xhci_softc::sc_bus, xhci_softc::sc_callout, xhci_softc::sc_ctlstep, xhci_softc::sc_imod_default, xhci_softc::sc_intr_hdl, xhci_softc::sc_io_hdl, xhci_softc::sc_io_res, xhci_softc::sc_io_size, xhci_softc::sc_io_tag, xhci_softc::sc_irq_res, xhci_softc::sc_msix_res, xhci_softc::sc_no_deconfigure, xhci_softc::sc_port_route, xhci_softc::sc_vendor, USB_BUS_LOCK, USB_BUS_UNLOCK, usb_callout_init_mtx, xhci_halt_controller(), XHCI_IMOD_DEFAULT_LP, xhci_init(), xhci_interrupt(), xhci_interrupt_poll(), xhci_pci_detach, xhci_pci_port_route(), xhci_pci_take_controller, xhci_start_controller(), xhci_use_msi, xhci_use_msix, and xhci_use_polling().

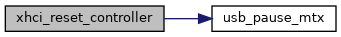

◆ xhci_reset_controller()

| usb_error_t xhci_reset_controller | ( | struct xhci_softc * | sc | ) |

Definition at line 484 of file xhci.c.

References DPRINTF, usb_bus::parent, xhci_softc::sc_bus, USB_ERR_IOERROR, usb_pause_mtx(), XHCI_CMD_HCRST, XHCI_STS_CNR, XHCI_USBCMD, XHCI_USBSTS, XREAD4, and XWRITE4.

Referenced by xhci_pci_detach(), xhci_set_hw_power_sleep(), and xhci_start_controller().

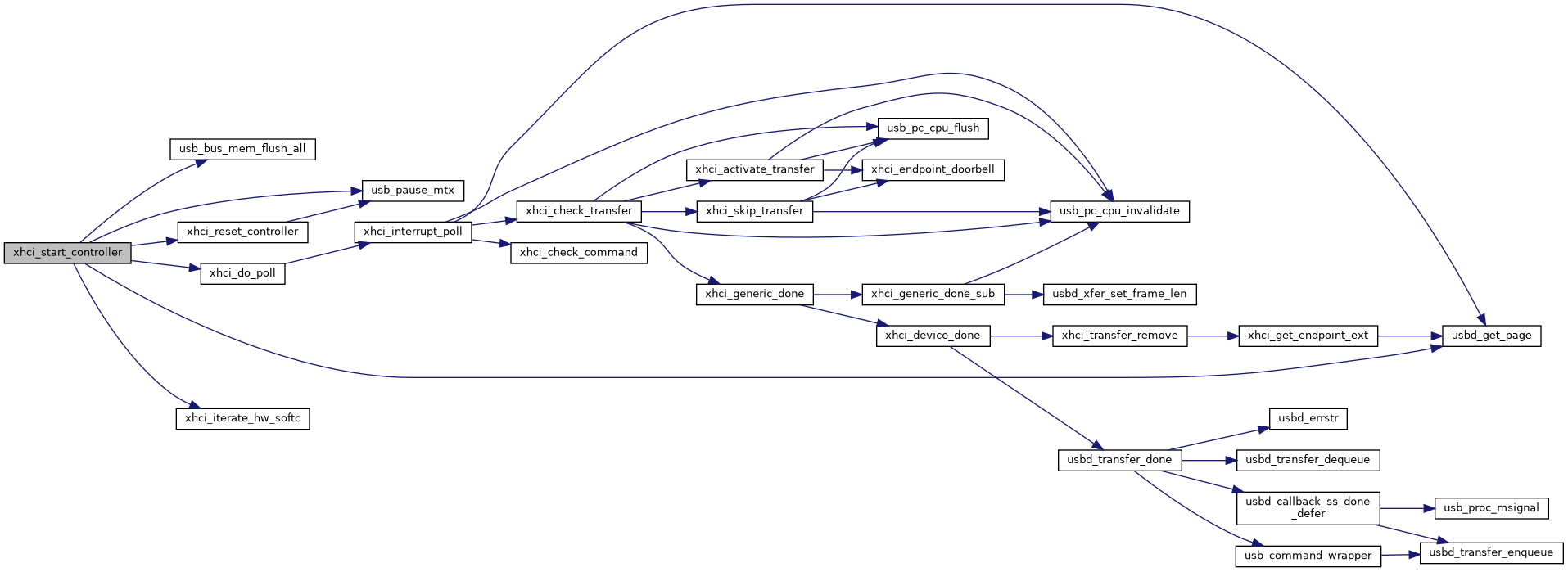

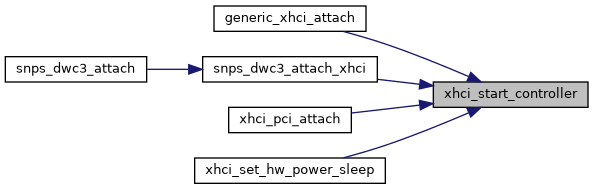

◆ xhci_start_controller()

| usb_error_t xhci_start_controller | ( | struct xhci_softc * | sc | ) |

Definition at line 304 of file xhci.c.

References addr, usb_page_search::buffer, xhci_hw_softc::ctx_pc, DPRINTF, xhci_event_ring_seg::dwEvrsTableSize, xhci_hw_root::hwr_commands, xhci_hw_root::hwr_ring_seg, usb_bus::parent, xhci_dev_ctx_addr::qwBaaDevCtxAddr, xhci_event_ring_seg::qwEvrsTablePtr, xhci_dev_ctx_addr::qwSpBufPtr, xhci_trb::qwTrb0, xhci_hw_softc::root_pc, xhci_softc::sc_bus, xhci_softc::sc_command_ccs, xhci_softc::sc_command_idx, xhci_softc::sc_erst_max, xhci_softc::sc_event_ccs, xhci_softc::sc_event_idx, xhci_softc::sc_hw, xhci_softc::sc_imod_default, xhci_softc::sc_noscratch, xhci_softc::sc_noslot, xhci_softc::sc_port_route, xhci_hw_softc::scratch_pc, usb_bus_mem_flush_all(), USB_ERR_IOERROR, usb_pause_mtx(), usbd_get_page(), XHCI_CMD_HSEE, XHCI_CMD_INTE, XHCI_CMD_RS, XHCI_CONFIG, XHCI_CRCR_HI, XHCI_CRCR_LO, XHCI_CRCR_LO_RCS, XHCI_DCBAAP_HI, XHCI_DCBAAP_LO, XHCI_DNCTRL, xhci_do_poll(), XHCI_ERDP_HI, XHCI_ERDP_LO, XHCI_ERSTBA_HI, XHCI_ERSTBA_LO, XHCI_ERSTS_SET, XHCI_ERSTSZ, XHCI_IMAN, XHCI_IMAN_INTR_ENA, XHCI_IMOD, xhci_iterate_hw_softc(), XHCI_MAX_COMMANDS, XHCI_MAX_EVENTS, xhci_reset_controller(), XHCI_STS_HCH, XHCI_USBCMD, XHCI_USBSTS, xhciroute, XREAD4, and XWRITE4.

Referenced by generic_xhci_attach(), snps_dwc3_attach_xhci(), xhci_pci_attach(), and xhci_set_hw_power_sleep().

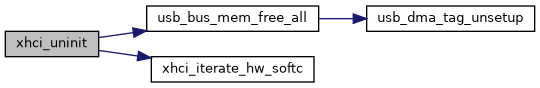

◆ xhci_uninit()

| void xhci_uninit | ( | struct xhci_softc * | sc | ) |

Definition at line 644 of file xhci.c.

References xhci_softc::sc_bus, xhci_softc::sc_cmd_cv, xhci_softc::sc_cmd_sx, usb_bus_mem_free_all(), and xhci_iterate_hw_softc().

Referenced by generic_xhci_detach(), and xhci_pci_detach().

◆ xhci_use_polling()

| uint8_t xhci_use_polling | ( | void | ) |

Definition at line 213 of file xhci.c.

Referenced by xhci_pci_attach().

Variable Documentation

◆ __aligned

| struct xhci_command __aligned |

◆ __packed

| struct xhci_bos_desc __packed |

◆ alt_next

◆ ctx_ep

| struct xhci_endp_ctx64 ctx_ep |

Definition at line 1 of file xhci.h.

Referenced by xhci_configure_endpoint(), and xhci_get_endpoint_state().

◆ ctx_slot

| struct xhci_slot_ctx64 ctx_slot |

Definition at line 0 of file xhci.h.

Referenced by xhci_configure_device(), xhci_configure_mask(), and xhci_set_address().

◆ dummy

◆ dwTrb2

| volatile uint32_t dwTrb2 |

Definition at line 3 of file xhci.h.

Referenced by xhci_configure_endpoint_by_xfer().

◆ dwTrb3

| volatile uint32_t dwTrb3 |

Definition at line 17 of file xhci.h.

Referenced by xhci_configure_endpoint_by_xfer().

◆ len

◆ next

◆ ntrb

◆ obj_next

◆ page_cache

| struct usb_page_cache* page_cache |

◆ qwTrb0

| volatile uint64_t qwTrb0 |

Definition at line 0 of file xhci.h.

Referenced by xhci_configure_endpoint_by_xfer().

◆ remainder

| uint32_t remainder |

Definition at line 12 of file xhci.h.

Referenced by rum_setup_tx_desc(), ural_setup_tx_desc(), and xhci_check_transfer().

◆ status

| uint8_t status |

Definition at line 14 of file xhci.h.

Referenced by acpi_uhub_attach_common(), acpi_uhub_find_rh_cb(), acpi_uhub_root_probe(), atmegadci_interrupt(), avr32dci_interrupt(), axge_rxeof(), dwc_otg_filter_interrupt(), dwc_otg_interrupt(), ehci_check_transfer(), ehci_device_isoc_hs_enter(), ehci_interrupt(), ehci_isoc_fs_done(), ehci_isoc_hs_done(), ehci_non_isoc_done_sub(), ohci_interrupt(), rue_bulk_read_callback(), uath_update_rxstat(), uhci_check_transfer(), uhci_interrupt(), uhci_isoc_done(), uhci_non_isoc_done_sub(), uhci_roothub_exec(), umass_cam_attach_sim(), umass_cam_cb(), umass_cam_quirk_cb(), umass_cam_sense_cb(), umass_init_shuttle(), umass_t_cbi_status_callback(), ums_fifo_ioctl(), ure_ifmedia_sts(), usbd_req_reset_port(), usbd_req_warm_reset_port(), wsp_ioctl(), xhci_check_transfer(), xhci_generic_done_sub(), and xhci_interrupt().

◆ td_self

◆ td_trb

| struct xhci_trb td_trb[XHCI_TD_PAGE_NBUF+1] |