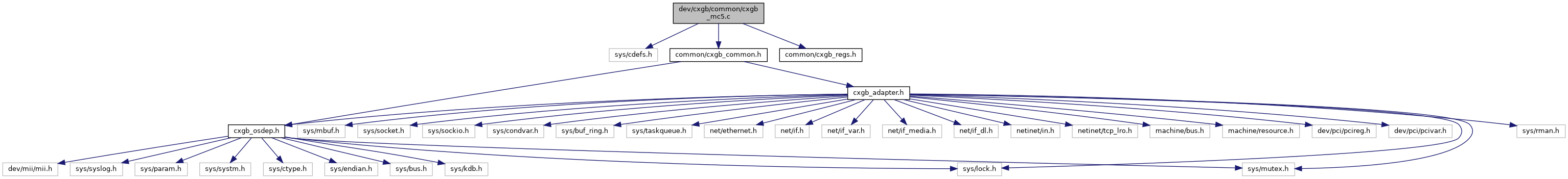

Go to the source code of this file.

Macros | |

| #define | IDT_CMD_READ 0 |

| #define | IDT_CMD_WRITE 1 |

| #define | IDT_CMD_SEARCH 2 |

| #define | IDT_CMD_LEARN 3 |

| #define | IDT_LAR_ADR0 0x180006 |

| #define | IDT_LAR_MODE144 0xffff0000 |

| #define | IDT_SCR_ADR0 0x180000 |

| #define | IDT_SSR0_ADR0 0x180002 |

| #define | IDT_SSR1_ADR0 0x180004 |

| #define | IDT_GMR_BASE_ADR0 0x180020 |

| #define | IDT_DATARY_BASE_ADR0 0 |

| #define | IDT_MSKARY_BASE_ADR0 0x80000 |

| #define | IDT4_CMD_SEARCH144 3 |

| #define | IDT4_CMD_WRITE 4 |

| #define | IDT4_CMD_READ 5 |

| #define | IDT4_SCR_ADR0 0x3 |

| #define | IDT4_GMR_BASE0 0x10 |

| #define | IDT4_GMR_BASE1 0x20 |

| #define | IDT4_GMR_BASE2 0x30 |

| #define | IDT4_DATARY_BASE_ADR0 0x1000000 |

| #define | IDT4_MSKARY_BASE_ADR0 0x2000000 |

| #define | MAX_WRITE_ATTEMPTS 5 |

| #define | MAX_ROUTES 2048 |

| #define | MC5_INT_FATAL (F_PARITYERR | F_REQQPARERR | F_DISPQPARERR) |

| #define | K * 1024 |

Enumerations | |

| enum | { IDT75P52100 = 4 , IDT75N43102 = 5 } |

| enum | { DBGI_MODE_MBUS = 0 , DBGI_MODE_IDT52100 = 5 } |

Functions | |

| __FBSDID ("$FreeBSD$") | |

| static int | mc5_cmd_write (adapter_t *adapter, u32 cmd) |

| static void | dbgi_wr_data3 (adapter_t *adapter, u32 v1, u32 v2, u32 v3) |

| static void | dbgi_rd_rsp3 (adapter_t *adapter, u32 *v1, u32 *v2, u32 *v3) |

| static int | mc5_write (adapter_t *adapter, u32 addr_lo, u32 cmd) |

| static int | init_mask_data_array (struct mc5 *mc5, u32 mask_array_base, u32 data_array_base, u32 write_cmd, int addr_shift) |

| static int | init_idt52100 (struct mc5 *mc5) |

| static int | init_idt43102 (struct mc5 *mc5) |

| static void | mc5_dbgi_mode_enable (const struct mc5 *mc5) |

| static void | mc5_dbgi_mode_disable (const struct mc5 *mc5) |

| int | t3_mc5_init (struct mc5 *mc5, unsigned int nservers, unsigned int nfilters, unsigned int nroutes) |

| int | t3_read_mc5_range (const struct mc5 *mc5, unsigned int start, unsigned int n, u32 *buf) |

| void | t3_mc5_intr_handler (struct mc5 *mc5) |

| void __devinit | t3_mc5_prep (adapter_t *adapter, struct mc5 *mc5, int mode) |

Macro Definition Documentation

◆ IDT4_CMD_READ

| #define IDT4_CMD_READ 5 |

Definition at line 73 of file cxgb_mc5.c.

◆ IDT4_CMD_SEARCH144

| #define IDT4_CMD_SEARCH144 3 |

Definition at line 71 of file cxgb_mc5.c.

◆ IDT4_CMD_WRITE

| #define IDT4_CMD_WRITE 4 |

Definition at line 72 of file cxgb_mc5.c.

◆ IDT4_DATARY_BASE_ADR0

| #define IDT4_DATARY_BASE_ADR0 0x1000000 |

Definition at line 84 of file cxgb_mc5.c.

◆ IDT4_GMR_BASE0

| #define IDT4_GMR_BASE0 0x10 |

Definition at line 79 of file cxgb_mc5.c.

◆ IDT4_GMR_BASE1

| #define IDT4_GMR_BASE1 0x20 |

Definition at line 80 of file cxgb_mc5.c.

◆ IDT4_GMR_BASE2

| #define IDT4_GMR_BASE2 0x30 |

Definition at line 81 of file cxgb_mc5.c.

◆ IDT4_MSKARY_BASE_ADR0

| #define IDT4_MSKARY_BASE_ADR0 0x2000000 |

Definition at line 85 of file cxgb_mc5.c.

◆ IDT4_SCR_ADR0

| #define IDT4_SCR_ADR0 0x3 |

Definition at line 76 of file cxgb_mc5.c.

◆ IDT_CMD_LEARN

| #define IDT_CMD_LEARN 3 |

Definition at line 52 of file cxgb_mc5.c.

◆ IDT_CMD_READ

| #define IDT_CMD_READ 0 |

Definition at line 49 of file cxgb_mc5.c.

◆ IDT_CMD_SEARCH

| #define IDT_CMD_SEARCH 2 |

Definition at line 51 of file cxgb_mc5.c.

◆ IDT_CMD_WRITE

| #define IDT_CMD_WRITE 1 |

Definition at line 50 of file cxgb_mc5.c.

◆ IDT_DATARY_BASE_ADR0

| #define IDT_DATARY_BASE_ADR0 0 |

Definition at line 67 of file cxgb_mc5.c.

◆ IDT_GMR_BASE_ADR0

| #define IDT_GMR_BASE_ADR0 0x180020 |

Definition at line 64 of file cxgb_mc5.c.

◆ IDT_LAR_ADR0

| #define IDT_LAR_ADR0 0x180006 |

Definition at line 55 of file cxgb_mc5.c.

◆ IDT_LAR_MODE144

| #define IDT_LAR_MODE144 0xffff0000 |

Definition at line 56 of file cxgb_mc5.c.

◆ IDT_MSKARY_BASE_ADR0

| #define IDT_MSKARY_BASE_ADR0 0x80000 |

Definition at line 68 of file cxgb_mc5.c.

◆ IDT_SCR_ADR0

| #define IDT_SCR_ADR0 0x180000 |

Definition at line 59 of file cxgb_mc5.c.

◆ IDT_SSR0_ADR0

| #define IDT_SSR0_ADR0 0x180002 |

Definition at line 60 of file cxgb_mc5.c.

◆ IDT_SSR1_ADR0

| #define IDT_SSR1_ADR0 0x180004 |

Definition at line 61 of file cxgb_mc5.c.

◆ K

| #define K * 1024 |

◆ MAX_ROUTES

| #define MAX_ROUTES 2048 |

Definition at line 89 of file cxgb_mc5.c.

◆ MAX_WRITE_ATTEMPTS

| #define MAX_WRITE_ATTEMPTS 5 |

Definition at line 87 of file cxgb_mc5.c.

◆ MC5_INT_FATAL

| #define MC5_INT_FATAL (F_PARITYERR | F_REQQPARERR | F_DISPQPARERR) |

Definition at line 422 of file cxgb_mc5.c.

Enumeration Type Documentation

◆ anonymous enum

| anonymous enum |

| Enumerator | |

|---|---|

| IDT75P52100 | |

| IDT75N43102 | |

Definition at line 37 of file cxgb_mc5.c.

◆ anonymous enum

| anonymous enum |

| Enumerator | |

|---|---|

| DBGI_MODE_MBUS | |

| DBGI_MODE_IDT52100 | |

Definition at line 43 of file cxgb_mc5.c.

Function Documentation

◆ __FBSDID()

| __FBSDID | ( | "$FreeBSD$" | ) |

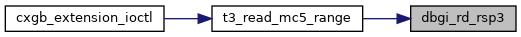

◆ dbgi_rd_rsp3()

Definition at line 109 of file cxgb_mc5.c.

References A_MC5_DB_DBGI_RSP_DATA0, A_MC5_DB_DBGI_RSP_DATA1, A_MC5_DB_DBGI_RSP_DATA2, and t3_read_reg().

Referenced by t3_read_mc5_range().

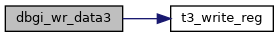

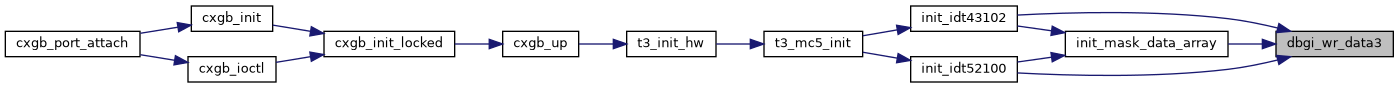

◆ dbgi_wr_data3()

Definition at line 102 of file cxgb_mc5.c.

References A_MC5_DB_DBGI_REQ_DATA0, A_MC5_DB_DBGI_REQ_DATA1, A_MC5_DB_DBGI_REQ_DATA2, and t3_write_reg().

Referenced by init_idt43102(), init_idt52100(), and init_mask_data_array().

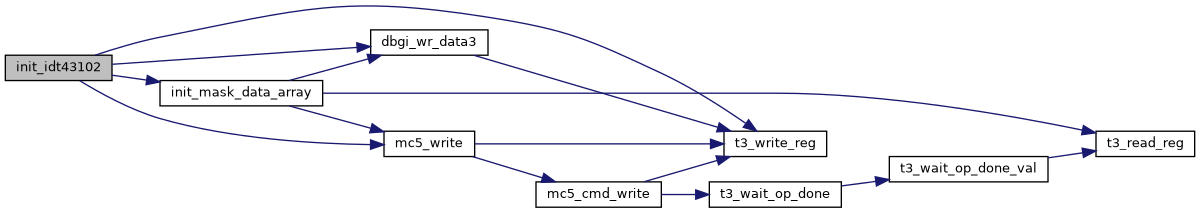

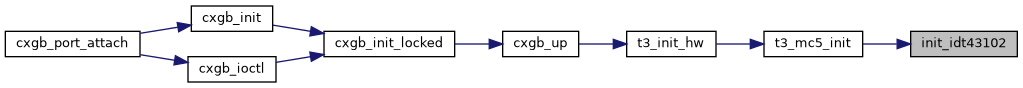

◆ init_idt43102()

|

static |

Definition at line 244 of file cxgb_mc5.c.

References A_MC5_DB_ACK_SRCH_CMD, A_MC5_DB_AOPEN_SRCH_CMD, A_MC5_DB_DATA_READ_CMD, A_MC5_DB_DATA_WRITE_CMD, A_MC5_DB_DBGI_CONFIG, A_MC5_DB_ELOOKUP_CMD, A_MC5_DB_ILOOKUP_CMD, A_MC5_DB_PART_ID_INDEX, A_MC5_DB_POPEN_DATA_WR_CMD, A_MC5_DB_POPEN_MASK_WR_CMD, A_MC5_DB_RSP_LATENCY, A_MC5_DB_SYN_SRCH_CMD, mc5::adapter, DBGI_MODE_IDT52100, dbgi_wr_data3(), IDT4_CMD_READ, IDT4_CMD_SEARCH144, IDT4_CMD_WRITE, IDT4_DATARY_BASE_ADR0, IDT4_GMR_BASE0, IDT4_GMR_BASE1, IDT4_GMR_BASE2, IDT4_MSKARY_BASE_ADR0, IDT4_SCR_ADR0, init_mask_data_array(), mc5_write(), adapter::params, adapter_params::rev, t3_write_reg(), V_RDLAT, and V_SRCHLAT.

Referenced by t3_mc5_init().

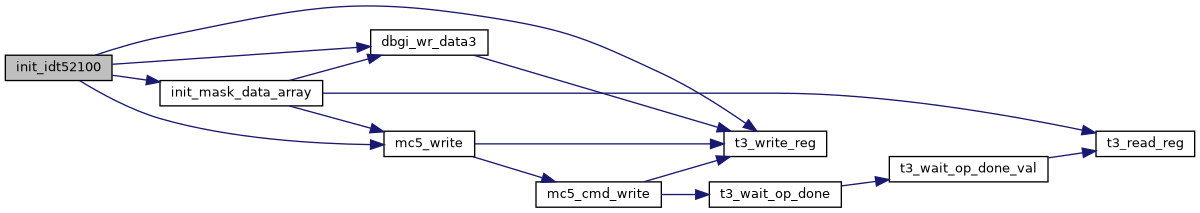

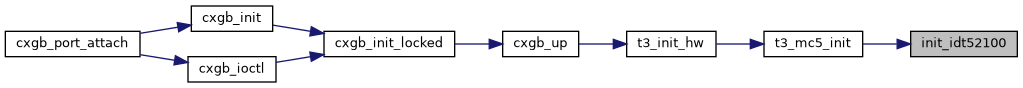

◆ init_idt52100()

|

static |

Definition at line 180 of file cxgb_mc5.c.

References A_MC5_DB_ACK_LRN_CMD, A_MC5_DB_ACK_SRCH_CMD, A_MC5_DB_AOPEN_LRN_CMD, A_MC5_DB_AOPEN_SRCH_CMD, A_MC5_DB_DATA_READ_CMD, A_MC5_DB_DATA_WRITE_CMD, A_MC5_DB_DBGI_CONFIG, A_MC5_DB_ELOOKUP_CMD, A_MC5_DB_ILOOKUP_CMD, A_MC5_DB_PART_ID_INDEX, A_MC5_DB_POPEN_DATA_WR_CMD, A_MC5_DB_POPEN_MASK_WR_CMD, A_MC5_DB_RSP_LATENCY, A_MC5_DB_SYN_LRN_CMD, A_MC5_DB_SYN_SRCH_CMD, mc5::adapter, DBGI_MODE_IDT52100, dbgi_wr_data3(), IDT_CMD_LEARN, IDT_CMD_READ, IDT_CMD_SEARCH, IDT_CMD_WRITE, IDT_DATARY_BASE_ADR0, IDT_GMR_BASE_ADR0, IDT_LAR_ADR0, IDT_LAR_MODE144, IDT_MSKARY_BASE_ADR0, IDT_SCR_ADR0, IDT_SSR0_ADR0, IDT_SSR1_ADR0, init_mask_data_array(), mc5_write(), t3_write_reg(), V_LRNLAT, V_RDLAT, and V_SRCHLAT.

Referenced by t3_mc5_init().

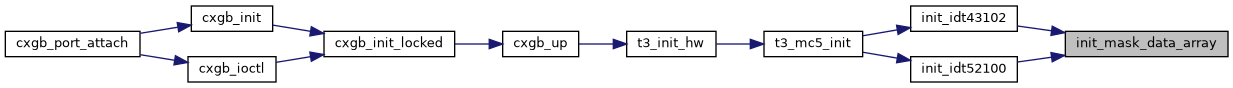

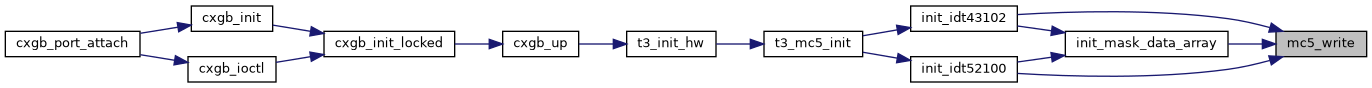

◆ init_mask_data_array()

|

static |

Definition at line 130 of file cxgb_mc5.c.

References A_MC5_DB_SERVER_INDEX, mc5::adapter, dbgi_wr_data3(), MC5_MODE_144_BIT, mc5_write(), mc5::mode, t3_read_reg(), and mc5::tcam_size.

Referenced by init_idt43102(), and init_idt52100().

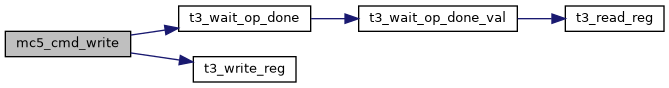

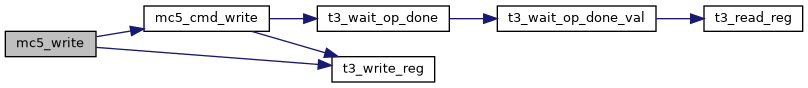

◆ mc5_cmd_write()

Definition at line 95 of file cxgb_mc5.c.

References A_MC5_DB_DBGI_REQ_CMD, A_MC5_DB_DBGI_RSP_STATUS, F_DBGIRSPVALID, MAX_WRITE_ATTEMPTS, t3_wait_op_done(), and t3_write_reg().

Referenced by mc5_write(), and t3_read_mc5_range().

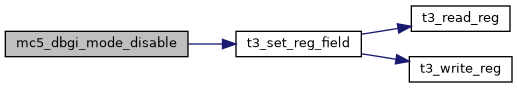

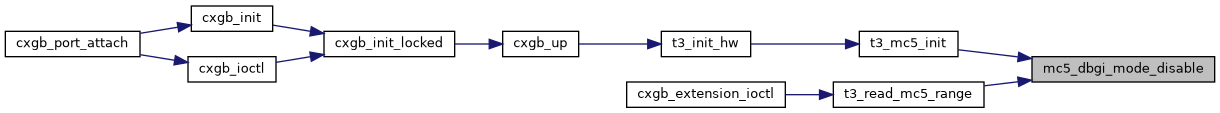

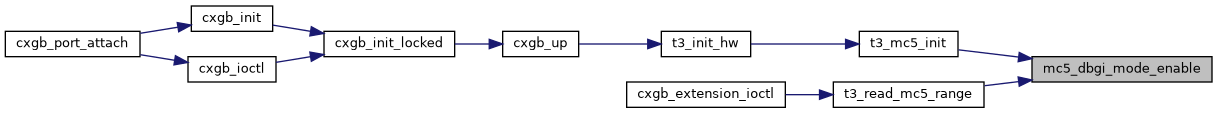

◆ mc5_dbgi_mode_disable()

|

static |

Definition at line 312 of file cxgb_mc5.c.

References A_MC5_DB_CONFIG, mc5::adapter, F_DBGIEN, F_MBUSEN, mc5::parity_enabled, t3_set_reg_field(), and V_PRTYEN.

Referenced by t3_mc5_init(), and t3_read_mc5_range().

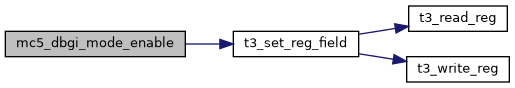

◆ mc5_dbgi_mode_enable()

|

inlinestatic |

Definition at line 305 of file cxgb_mc5.c.

References A_MC5_DB_CONFIG, mc5::adapter, F_DBGIEN, F_MBUSEN, F_PRTYEN, and t3_set_reg_field().

Referenced by t3_mc5_init(), and t3_read_mc5_range().

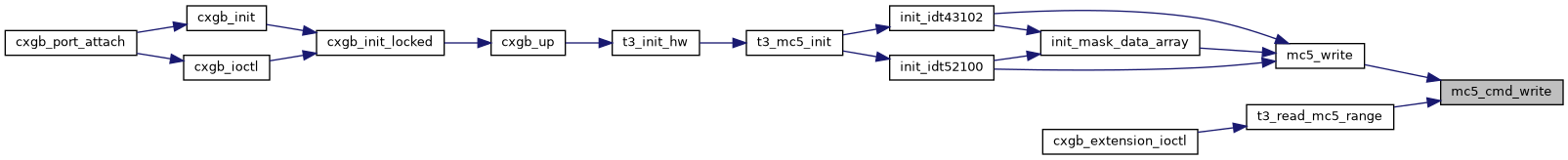

◆ mc5_write()

Definition at line 121 of file cxgb_mc5.c.

References A_MC5_DB_DBGI_REQ_ADDR0, CH_ERR, mc5_cmd_write(), and t3_write_reg().

Referenced by init_idt43102(), init_idt52100(), and init_mask_data_array().

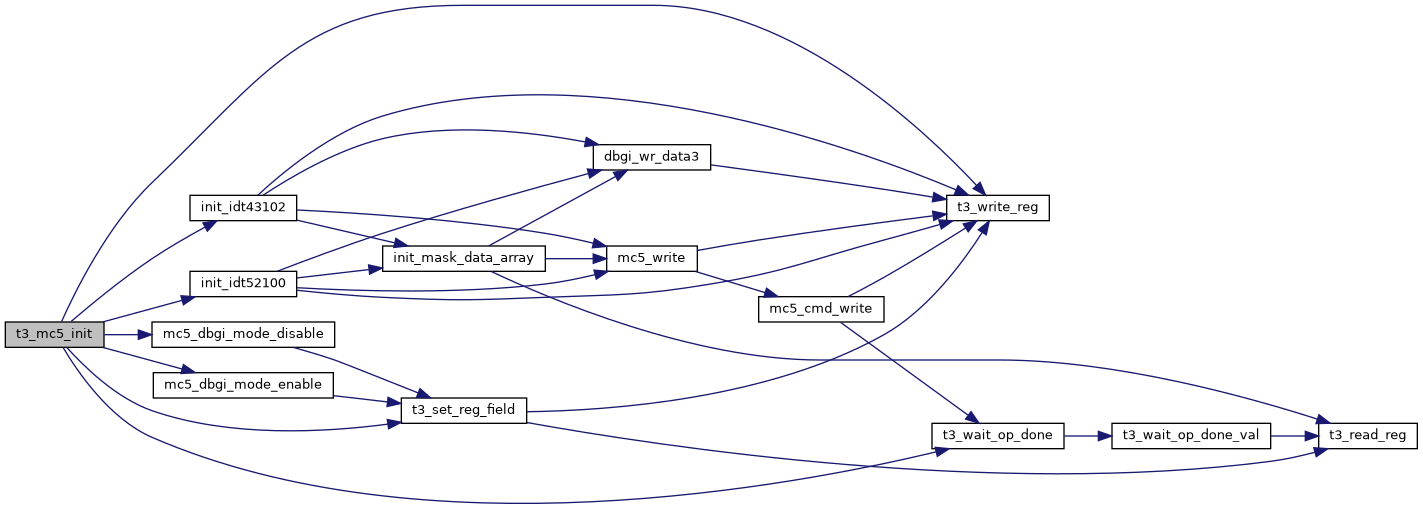

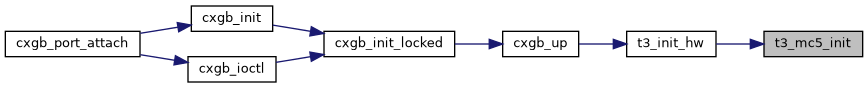

◆ t3_mc5_init()

| int t3_mc5_init | ( | struct mc5 * | mc5, |

| unsigned int | nservers, | ||

| unsigned int | nfilters, | ||

| unsigned int | nroutes | ||

| ) |

t3_mc5_init - initialize MC5 and the TCAM @mc5: the MC5 handle @nservers: desired number the TCP servers (listening ports) @nfilters: desired number of HW filters (classifiers) @nroutes: desired number of routes

Initialize MC5 and the TCAM and partition the TCAM for the requested number of servers, filters, and routes. The number of routes is typically 0 except for specialized uses of the T3 adapters.

Definition at line 329 of file cxgb_mc5.c.

References A_MC5_DB_CONFIG, A_MC5_DB_DBGI_REQ_ADDR1, A_MC5_DB_DBGI_REQ_ADDR2, A_MC5_DB_FILTER_TABLE, A_MC5_DB_ROUTING_TABLE_INDEX, A_MC5_DB_SERVER_INDEX, mc5::adapter, CH_ERR, F_COMPEN, F_TMMODE, F_TMRDY, F_TMRST, IDT75N43102, IDT75P52100, init_idt43102(), init_idt52100(), MAX_ROUTES, mc5_dbgi_mode_disable(), mc5_dbgi_mode_enable(), MC5_MODE_72_BIT, mc5::mode, mc5::parity_enabled, mc5::part_type, t3_set_reg_field(), t3_wait_op_done(), t3_write_reg(), mc5::tcam_size, V_COMPEN, and V_TMMODE.

Referenced by t3_init_hw().

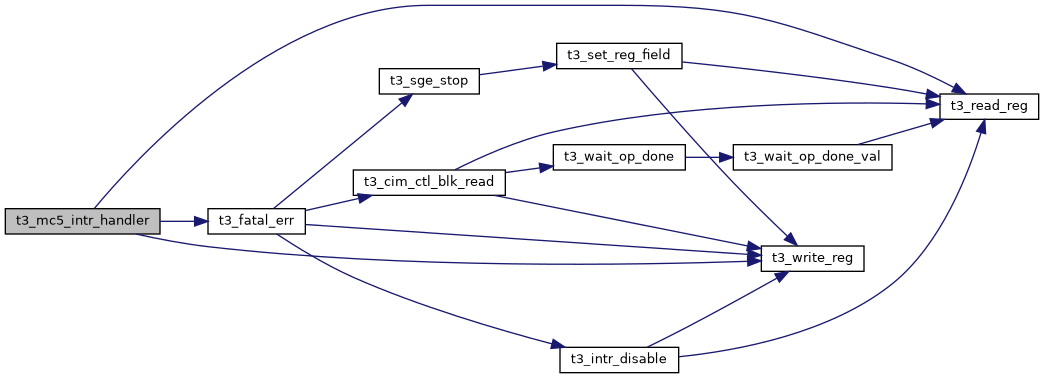

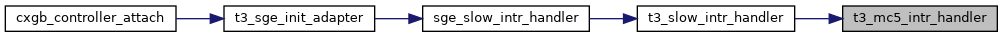

◆ t3_mc5_intr_handler()

| void t3_mc5_intr_handler | ( | struct mc5 * | mc5 | ) |

t3_mc5_intr_handler - MC5 interrupt handler @mc5: the MC5 handle

The MC5 interrupt handler.

Definition at line 430 of file cxgb_mc5.c.

References A_MC5_DB_INT_CAUSE, mc5_stats::active_rgn_full, mc5::adapter, CH_ALERT, mc5_stats::del_act_empty, mc5_stats::dispq_parity_err, F_ACTRGNFULL, F_DELACTEMPTY, F_DISPQPARERR, F_NFASRCHFAIL, F_PARITYERR, F_REQQPARERR, F_UNKNOWNCMD, MC5_INT_FATAL, mc5_stats::nfa_srch_err, mc5::parity_enabled, mc5_stats::parity_err, mc5_stats::reqq_parity_err, mc5::stats, t3_fatal_err(), t3_read_reg(), t3_write_reg(), and mc5_stats::unknown_cmd.

Referenced by t3_slow_intr_handler().

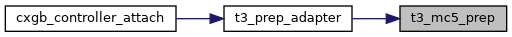

◆ t3_mc5_prep()

t3_mc5_prep - initialize the SW state for MC5 @adapter: the adapter @mc5: the MC5 handle @mode: whether the TCAM will be in 72- or 144-bit mode

Initialize the SW state associated with MC5. Among other things this determines the size of the attached TCAM.

Definition at line 473 of file cxgb_mc5.c.

References A_MC5_DB_CONFIG, mc5::adapter, adapter, F_TMTYPEHI, G_TMPARTSIZE, G_TMTYPE, K, MC5_MODE_144_BIT, mc5::mode, mc5::parity_enabled, mc5::part_type, t3_read_reg(), and mc5::tcam_size.

Referenced by t3_prep_adapter().

◆ t3_read_mc5_range()

read_mc5_range - dump a part of the memory managed by MC5 @mc5: the MC5 handle @start: the start address for the dump

: number of 72-bit words to read @buf: result buffer

Read n 72-bit words from MC5 memory from the given start location.

Definition at line 392 of file cxgb_mc5.c.

References A_MC5_DB_DBGI_REQ_ADDR0, mc5::adapter, dbgi_rd_rsp3(), IDT4_CMD_READ, IDT75N43102, IDT75P52100, IDT_CMD_READ, mc5_cmd_write(), mc5_dbgi_mode_disable(), mc5_dbgi_mode_enable(), mc5::part_type, and t3_write_reg().

Referenced by cxgb_extension_ioctl().