#include <sys/cdefs.h>#include <sys/param.h>#include <sys/systm.h>#include <sys/bus.h>#include <sys/lock.h>#include <sys/kernel.h>#include <sys/mutex.h>#include <sys/sysctl.h>#include <dev/pci/pcivar.h>#include <dev/pci/pcireg.h>#include <vm/vm.h>#include <vm/pmap.h>#include <machine/pci_cfgreg.h>

Go to the source code of this file.

Macros | |

| #define | PCIE_VADDR(base, reg, bus, slot, func) |

Functions | |

| __FBSDID ("$FreeBSD$") | |

| static uint32_t | pci_docfgregread (int bus, int slot, int func, int reg, int bytes) |

| static int | pciereg_cfgread (int bus, unsigned slot, unsigned func, unsigned reg, unsigned bytes) |

| static void | pciereg_cfgwrite (int bus, unsigned slot, unsigned func, unsigned reg, int data, unsigned bytes) |

| static int | pcireg_cfgread (int bus, int slot, int func, int reg, int bytes) |

| static void | pcireg_cfgwrite (int bus, int slot, int func, int reg, int data, int bytes) |

| SYSCTL_DECL (_hw_pci) | |

| MTX_SYSINIT (pcicfg_mtx, &pcicfg_mtx, "pcicfg_mtx", MTX_SPIN) | |

| SYSCTL_INT (_hw_pci, OID_AUTO, mcfg, CTLFLAG_RDTUN, &mcfg_enable, 0, "Enable support for PCI-e memory mapped config access") | |

| int | pci_cfgregopen (void) |

| u_int32_t | pci_cfgregread (int bus, int slot, int func, int reg, int bytes) |

| void | pci_cfgregwrite (int bus, int slot, int func, int reg, u_int32_t data, int bytes) |

| static int | pci_cfgenable (unsigned bus, unsigned slot, unsigned func, int reg, int bytes) |

| static void | pci_cfgdisable (void) |

| int | pcie_cfgregopen (uint64_t base, uint8_t minbus, uint8_t maxbus) |

Variables | |

| int | cfgmech = CFGMECH_1 |

| static vm_offset_t | pcie_base |

| static int | pcie_minbus |

| static int | pcie_maxbus |

| static uint32_t | pcie_badslots |

| static struct mtx | pcicfg_mtx |

| static int | mcfg_enable = 1 |

Macro Definition Documentation

◆ PCIE_VADDR

Function Documentation

◆ __FBSDID()

| __FBSDID | ( | "$FreeBSD$" | ) |

◆ MTX_SYSINIT()

| MTX_SYSINIT | ( | pcicfg_mtx | , |

| & | pcicfg_mtx, | ||

| "pcicfg_mtx" | , | ||

| MTX_SPIN | |||

| ) |

◆ pci_cfgdisable()

|

static |

Definition at line 155 of file pci_cfgreg.c.

Referenced by pcireg_cfgread(), and pcireg_cfgwrite().

◆ pci_cfgenable()

|

static |

Definition at line 139 of file pci_cfgreg.c.

References bus, func, PCI_BUSMAX, PCI_FUNCMAX, PCI_REGMAX, PCI_SLOTMAX, reg, and slot.

Referenced by pcireg_cfgread(), and pcireg_cfgwrite().

◆ pci_cfgregopen()

| int pci_cfgregopen | ( | void | ) |

Definition at line 75 of file pci_cfgreg.c.

Referenced by pcie_cfgregopen().

◆ pci_cfgregread()

| u_int32_t pci_cfgregread | ( | int | bus, |

| int | slot, | ||

| int | func, | ||

| int | reg, | ||

| int | bytes | ||

| ) |

Definition at line 97 of file pci_cfgreg.c.

References bus, func, pci_docfgregread(), PCIR_INTLINE, reg, and slot.

◆ pci_cfgregwrite()

| void pci_cfgregwrite | ( | int | bus, |

| int | slot, | ||

| int | func, | ||

| int | reg, | ||

| u_int32_t | data, | ||

| int | bytes | ||

| ) |

Definition at line 122 of file pci_cfgreg.c.

References bus, cfgmech, data, func, pcie_badslots, pcie_maxbus, pcie_minbus, pciereg_cfgwrite(), pcireg_cfgwrite(), reg, and slot.

◆ pci_docfgregread()

|

static |

Definition at line 82 of file pci_cfgreg.c.

References bus, cfgmech, func, pcie_badslots, pcie_maxbus, pcie_minbus, pciereg_cfgread(), pcireg_cfgread(), reg, and slot.

Referenced by pci_cfgregread().

◆ pcie_cfgregopen()

| int pcie_cfgregopen | ( | uint64_t | base, |

| uint8_t | minbus, | ||

| uint8_t | maxbus | ||

| ) |

Definition at line 215 of file pci_cfgreg.c.

References cfgmech, mcfg_enable, pci_cfgregopen(), PCI_SLOTMAX, pcie_badslots, pcie_base, pcie_maxbus, pcie_minbus, pciereg_cfgread(), pcireg_cfgread(), and slot.

◆ pciereg_cfgread()

|

static |

Definition at line 273 of file pci_cfgreg.c.

References bus, data, func, PCI_FUNCMAX, PCI_SLOTMAX, pcie_base, pcie_maxbus, PCIE_REGMAX, PCIE_VADDR, reg, and slot.

Referenced by pci_docfgregread(), and pcie_cfgregopen().

◆ pciereg_cfgwrite()

|

static |

Definition at line 304 of file pci_cfgreg.c.

References bus, data, func, PCI_FUNCMAX, PCI_SLOTMAX, pcie_base, pcie_maxbus, PCIE_REGMAX, PCIE_VADDR, reg, and slot.

Referenced by pci_cfgregwrite().

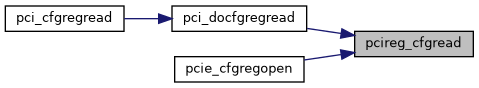

◆ pcireg_cfgread()

|

static |

Definition at line 165 of file pci_cfgreg.c.

References bus, data, func, pci_cfgdisable(), pci_cfgenable(), pcicfg_mtx, reg, and slot.

Referenced by pci_docfgregread(), and pcie_cfgregopen().

◆ pcireg_cfgwrite()

|

static |

Definition at line 191 of file pci_cfgreg.c.

References bus, data, func, pci_cfgdisable(), pci_cfgenable(), pcicfg_mtx, reg, and slot.

Referenced by pci_cfgregwrite().

◆ SYSCTL_DECL()

| SYSCTL_DECL | ( | _hw_pci | ) |

◆ SYSCTL_INT()

| SYSCTL_INT | ( | _hw_pci | , |

| OID_AUTO | , | ||

| mcfg | , | ||

| CTLFLAG_RDTUN | , | ||

| & | mcfg_enable, | ||

| 0 | , | ||

| "Enable support for PCI-e memory mapped config access" | |||

| ) |

Variable Documentation

◆ cfgmech

| int cfgmech = CFGMECH_1 |

Definition at line 63 of file pci_cfgreg.c.

Referenced by pci_cfgregwrite(), pci_docfgregread(), and pcie_cfgregopen().

◆ mcfg_enable

|

static |

Definition at line 70 of file pci_cfgreg.c.

Referenced by pcie_cfgregopen().

◆ pcicfg_mtx

|

static |

Definition at line 68 of file pci_cfgreg.c.

Referenced by pcireg_cfgread(), and pcireg_cfgwrite().

◆ pcie_badslots

|

static |

Definition at line 67 of file pci_cfgreg.c.

Referenced by pci_cfgregwrite(), pci_docfgregread(), and pcie_cfgregopen().

◆ pcie_base

|

static |

Definition at line 65 of file pci_cfgreg.c.

Referenced by pcie_cfgregopen(), pciereg_cfgread(), and pciereg_cfgwrite().

◆ pcie_maxbus

|

static |

Definition at line 66 of file pci_cfgreg.c.

Referenced by pci_cfgregwrite(), pci_docfgregread(), pcie_cfgregopen(), pciereg_cfgread(), and pciereg_cfgwrite().

◆ pcie_minbus

|

static |

Definition at line 66 of file pci_cfgreg.c.

Referenced by pci_cfgregwrite(), pci_docfgregread(), and pcie_cfgregopen().