spcdefs.h File Reference

The file defines the MPI Application Programming Interface (API) More...

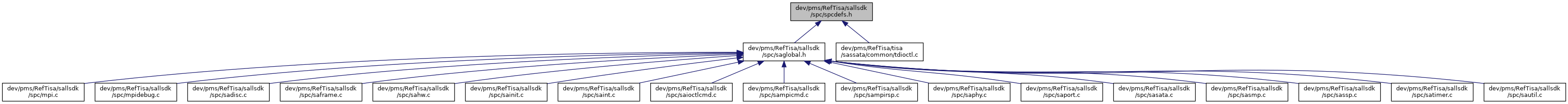

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Data Structures | |

| struct | mpiMsgHeader_s |

| MPI message header. More... | |

| struct | spc_configMainDescriptor_s |

| struct | spc_GSTableDescriptor_s |

| This structure is used for SPC MPI General Status Table. More... | |

| struct | spc_SPASTable_s |

| SAS Phy Analog Setup Table. More... | |

| struct | spc_inboundQueueDescriptor_s |

| This structure is used to configure inbound queues. More... | |

| struct | spc_outboundQueueDescriptor_s |

| This structure is used to configure outbound queues. More... | |

| struct | InterruptVT_s |

| struct | mpiInterruptVT_s |

| struct | phyAttrb_s |

| struct | sasPhyAttribute_s |

| struct | fwMSGUConfig_s |

Macros | |

| #define | SPC_MSGU_CFG_TABLE_UPDATE 0x001 /* Inbound doorbell bit0 */ |

| #define | SPC_MSGU_CFG_TABLE_RESET 0x002 /* Inbound doorbell bit1 */ |

| #define | SPC_MSGU_CFG_TABLE_FREEZE 0x004 /* Inbound doorbell bit2 */ |

| #define | SPC_MSGU_CFG_TABLE_UNFREEZE 0x008 /* Inbound doorbell bit4 */ |

| #define | SPCV_MSGU_CFG_TABLE_TRANSFER_DEBUG_INFO 0x080 /* Inbound doorbell bit7 SPCV */ |

| #define | SPCV_MSGU_HALT_CPUS 0x100 /* Inbound doorbell bit8 SPCV */ |

| #define | V_BIT 0x1 |

| #define | V_MASK 0x1 |

| #define | BC_MASK 0x1F |

| #define | OBID_MASK 0x3F |

| #define | CAT_MASK 0x0F |

| #define | OPCODE_MASK 0xFFF |

| #define | HEADER_V_MASK 0x80000000 |

| #define | HEADER_BC_MASK 0x1f000000 |

| #define | MAIN_SIGNATURE_OFFSET 0x00 /* DWORD 0x00 (R) */ |

| #define | MAIN_INTERFACE_REVISION 0x04 /* DWORD 0x01 (R) */ |

| #define | MAIN_FW_REVISION 0x08 /* DWORD 0x02 (R) */ |

| #define | MAIN_MAX_OUTSTANDING_IO_OFFSET 0x0C /* DWORD 0x03 (R) */ |

| #define | MAIN_MAX_SGL_OFFSET 0x10 /* DWORD 0x04 (R) */ |

| #define | MAIN_CNTRL_CAP_OFFSET 0x14 /* DWORD 0x05 (R) */ |

| #define | MAIN_GST_OFFSET 0x18 /* DWORD 0x06 (R) */ |

| #define | MAIN_IBQ_OFFSET 0x1C /* DWORD 0x07 (R) */ |

| #define | MAIN_OBQ_OFFSET 0x20 /* DWORD 0x08 (R) */ |

| #define | MAIN_IQNPPD_HPPD_OFFSET 0x24 /* DWORD 0x09 (W) */ |

| #define | MAIN_OB_HW_EVENT_PID03_OFFSET 0x28 /* DWORD 0x0A (W) */ /* reserved for SPCV */ |

| #define | MAIN_OB_HW_EVENT_PID47_OFFSET 0x2C /* DWORD 0x0B (W) */ /* reserved for SPCV */ |

| #define | MAIN_OB_NCQ_EVENT_PID03_OFFSET 0x30 /* DWORD 0x0C (W) */ /* reserved for SPCV */ |

| #define | MAIN_OB_NCQ_EVENT_PID47_OFFSET 0x34 /* DWORD 0x0D (W) */ /* reserved for SPCV */ |

| #define | MAIN_TITNX_EVENT_PID03_OFFSET 0x38 /* DWORD 0x0E (W) */ /* reserved for SPCV */ |

| #define | MAIN_TITNX_EVENT_PID47_OFFSET 0x3C /* DWORD 0x0F (W) */ /* reserved for SPCV */ |

| #define | MAIN_OB_SSP_EVENT_PID03_OFFSET 0x40 /* DWORD 0x10 (W) */ /* reserved for SPCV */ |

| #define | MAIN_OB_SSP_EVENT_PID47_OFFSET 0x44 /* DWORD 0x11 (W) */ /* reserved for SPCV */ |

| #define | MAIN_IO_ABORT_DELAY 0x48 /* DWORD 0x12 (W) */ /* reserved for SPCV */ |

| #define | MAIN_CUSTOMER_SETTING 0x4C /* DWORD 0x13 (W) */ /* reserved for SPCV */ |

| #define | MAIN_EVENT_LOG_ADDR_HI 0x50 /* DWORD 0x14 (W) */ |

| #define | MAIN_EVENT_LOG_ADDR_LO 0x54 /* DWORD 0x15 (W) */ |

| #define | MAIN_EVENT_LOG_BUFF_SIZE 0x58 /* DWORD 0x16 (W) */ |

| #define | MAIN_EVENT_LOG_OPTION 0x5C /* DWORD 0x17 (W) */ |

| #define | MAIN_IOP_EVENT_LOG_ADDR_HI 0x60 /* DWORD 0x18 (W) */ |

| #define | MAIN_IOP_EVENT_LOG_ADDR_LO 0x64 /* DWORD 0x19 (W) */ |

| #define | MAIN_IOP_EVENT_LOG_BUFF_SIZE 0x68 /* DWORD 0x1A (W) */ |

| #define | MAIN_IOP_EVENT_LOG_OPTION 0x6C /* DWORD 0x1B (W) */ |

| #define | MAIN_FATAL_ERROR_INTERRUPT 0x70 /* DWORD 0x1C (W) */ |

| #define | MAIN_FATAL_ERROR_RDUMP0_OFFSET 0x74 /* DWORD 0x1D (R) */ |

| #define | MAIN_FATAL_ERROR_RDUMP0_LENGTH 0x78 /* DWORD 0x1E (R) */ |

| #define | MAIN_FATAL_ERROR_RDUMP1_OFFSET 0x7C /* DWORD 0x1F (R) */ |

| #define | MAIN_FATAL_ERROR_RDUMP1_LENGTH 0x80 /* DWORD 0x20 (R) */ |

| #define | MAIN_HDA_FLAGS_OFFSET 0x84 /* DWORD 0x21 (R) */ /* reserved for SPCV */ |

| #define | MAIN_ANALOG_SETUP_OFFSET 0x88 /* DWORD 0x22 (R) */ |

| #define | MAIN_INT_VEC_TABLE_OFFSET 0x8C /* DWORD 0x23 (W) */ /* for SPCV */ |

| #define | MAIN_PHY_ATTRIBUTE_OFFSET 0x90 /* DWORD 0x24 (W) */ /* for SPCV */ |

| #define | MAIN_PRECTD_PRESETD 0x94 /* DWORD 0x25 (W) */ /* for SPCV */ |

| #define | MAIN_IRAD_RESERVED 0x98 /* DWORD 0x26 (W) */ /* for SPCV */ |

| #define | MAIN_MOQFOT_MOQFOES 0x9C /* DWORD 0x27 (W) */ /* for SPCV */ |

| #define | MAIN_MERRDCTO_MERRDCES 0xA0 /* DWORD 0x28 (W) */ /* for SPCV */ |

| #define | MAIN_ILAT_ILAV_ILASMRN_ILAMRN_ILAMJN 0xA4 /* DWORD 0x29 (W) */ /* for SPCV */ |

| #define | MAIN_INACTIVE_ILA_REVSION 0xA8 /* DWORD 0x2A (W) */ /* for SPCV V 3.02 */ |

| #define | MAIN_SEEPROM_REVSION 0xAC /* DWORD 0x2B (W) */ /* for SPCV V 3.02 */ |

| #define | MAIN_UNKNOWN1 0xB0 /* DWORD 0x2C (W) */ /* for SPCV V 3.03 */ |

| #define | MAIN_UNKNOWN2 0xB4 /* DWORD 0x2D (W) */ /* for SPCV V 3.03 */ |

| #define | MAIN_UNKNOWN3 0xB8 /* DWORD 0x2E (W) */ /* for SPCV V 3.03 */ |

| #define | MAIN_XCBI_REF_TAG_PAT 0xBC /* DWORD 0x2F (W) */ /* for SPCV V 3.03 */ |

| #define | MAIN_AWT_MIDRANGE 0xC0 /* DWORD 0x30 (W) */ /* for SPCV V 3.03 */ |

| #define | SPC_CONFIG |

| #define | MAIN_IO_ABORT_DELAY_END_TO_END_CRC_DISABLE 0x00010000 |

| #define | MAIN_MAX_IB_MASK 0x000000ff /* bit7-0 */ |

| #define | MAIN_MAX_OB_MASK 0x0000ff00 /* bit15-8 */ |

| #define | MAIN_PHY_COUNT_MASK 0x01f80000 /* bit24-19 */ |

| #define | MAIN_QSUPPORT_BITS 0x0007ffff |

| #define | MAIN_SAS_SUPPORT_BITS 0xfe000000 |

| #define | MAIN_MAX_SGL_BITS 0xFFFF |

| #define | MAIN_MAX_DEV_BITS 0xFFFF0000 |

| #define | MAIN_HDA_FLAG_BITS 0x000000FF |

| #define | FATAL_ERROR_INT_BITS 0xFF |

| #define | INT_REASRT_ENABLE 0x00020000 |

| #define | INT_REASRT_MS_ENABLE 0x00040000 |

| #define | INT_REASRT_DELAY_BITS 0xFFF80000 |

| #define | MAX_VALID_PHYS 8 |

| #define | IB_QUEUE_CFGSIZE 64 |

| #define | OB_QUEUE_CFGSIZE 64 |

| #define | IB_PROPERITY_OFFSET 0x00 |

| #define | IB_BASE_ADDR_HI_OFFSET 0x04 |

| #define | IB_BASE_ADDR_LO_OFFSET 0x08 |

| #define | IB_CI_BASE_ADDR_HI_OFFSET 0x0C |

| #define | IB_CI_BASE_ADDR_LO_OFFSET 0x10 |

| #define | IB_PIPCI_BAR 0x14 |

| #define | IB_PIPCI_BAR_OFFSET 0x18 |

| #define | IB_RESERVED_OFFSET 0x1C |

| #define | OB_PROPERITY_OFFSET 0x00 |

| #define | OB_BASE_ADDR_HI_OFFSET 0x04 |

| #define | OB_BASE_ADDR_LO_OFFSET 0x08 |

| #define | OB_PI_BASE_ADDR_HI_OFFSET 0x0C |

| #define | OB_PI_BASE_ADDR_LO_OFFSET 0x10 |

| #define | OB_CIPCI_BAR 0x14 |

| #define | OB_CIPCI_BAR_OFFSET 0x18 |

| #define | OB_INTERRUPT_COALES_OFFSET 0x1C |

| #define | OB_DYNAMIC_COALES_OFFSET 0x20 |

| #define | OB_PROPERTY_INT_ENABLE 0x40000000 |

| #define | GST_GSTLEN_MPIS_OFFSET 0x00 |

| #define | GST_IQ_FREEZE_STATE0_OFFSET 0x04 |

| #define | GST_IQ_FREEZE_STATE1_OFFSET 0x08 |

| #define | GST_MSGUTCNT_OFFSET 0x0C |

| #define | GST_IOPTCNT_OFFSET 0x10 |

| #define | GST_IOP1TCNT_OFFSET 0x14 |

| #define | GST_PHYSTATE_OFFSET 0x18 /* SPCV reserved */ |

| #define | GST_PHYSTATE0_OFFSET 0x18 /* SPCV reserved */ |

| #define | GST_PHYSTATE1_OFFSET 0x1C /* SPCV reserved */ |

| #define | GST_PHYSTATE2_OFFSET 0x20 /* SPCV reserved */ |

| #define | GST_PHYSTATE3_OFFSET 0x24 /* SPCV reserved */ |

| #define | GST_PHYSTATE4_OFFSET 0x28 /* SPCV reserved */ |

| #define | GST_PHYSTATE5_OFFSET 0x2C /* SPCV reserved */ |

| #define | GST_PHYSTATE6_OFFSET 0x30 /* SPCV reserved */ |

| #define | GST_PHYSTATE7_OFFSET 0x34 /* SPCV reserved */ |

| #define | GST_GPIO_PINS_OFFSET 0x38 |

| #define | GST_RERRINFO_OFFSET 0x44 |

| #define | GST_MPI_STATE_UNINIT 0x00 |

| #define | GST_MPI_STATE_INIT 0x01 |

| #define | GST_MPI_STATE_TERMINATION 0x02 |

| #define | GST_MPI_STATE_ERROR 0x03 |

| #define | GST_MPI_STATE_MASK 0x07 |

| #define | GST_INF_STATE_BITS 0xfffe0007 |

| #define | MPI_FATAL_ERROR_TABLE_OFFSET_MASK 0xFFFFFF |

| #define | MPI_FATAL_ERROR_TABLE_SIZE(value) ((0xFF000000 & value) >> SHIFT24) /* for SPCV */ |

| #define | MPI_FATAL_EDUMP_TABLE_LO_OFFSET 0x00 /* HNFBUFL */ |

| #define | MPI_FATAL_EDUMP_TABLE_HI_OFFSET 0x04 /* HNFBUFH */ |

| #define | MPI_FATAL_EDUMP_TABLE_LENGTH 0x08 /* HNFBLEN */ |

| #define | MPI_FATAL_EDUMP_TABLE_HANDSHAKE 0x0C /* FDDHSHK */ |

| #define | MPI_FATAL_EDUMP_TABLE_STATUS 0x10 /* FDDTSTAT */ |

| #define | MPI_FATAL_EDUMP_TABLE_ACCUM_LEN 0x14 /* ACCDDLEN */ |

| #define | MPI_FATAL_EDUMP_HANDSHAKE_RDY 0x1 |

| #define | MPI_FATAL_EDUMP_HANDSHAKE_BUSY 0x0 |

| #define | MPI_FATAL_EDUMP_TABLE_STAT_RSVD 0x0 |

| #define | MPI_FATAL_EDUMP_TABLE_STAT_DMA_FAILED 0x1 |

| #define | MPI_FATAL_EDUMP_TABLE_STAT_NF_SUCCESS_MORE_DATA 0x2 |

| #define | MPI_FATAL_EDUMP_TABLE_STAT_NF_SUCCESS_DONE 0x3 |

| #define | IOCTL_ERROR_NO_FATAL_ERROR 0x77 |

| #define | INT_VT_Coal_CNT_TO 0 |

| #define | INT_VT_Coal_ReAssert_Enab 4 |

| #define | PHY_STATE 0 |

| #define | PHY_EVENT_OQ 4 |

Typedefs | |

| typedef struct mpiMsgHeader_s | mpiMsgHeader_t |

| typedef struct spc_configMainDescriptor_s | spc_configMainDescriptor_t |

| typedef struct spc_GSTableDescriptor_s | spc_GSTableDescriptor_t |

| typedef struct spc_SPASTable_s | spc_SPASTable_t |

| typedef struct spc_inboundQueueDescriptor_s | spc_inboundQueueDescriptor_t |

| typedef struct spc_outboundQueueDescriptor_s | spc_outboundQueueDescriptor_t |

| typedef struct InterruptVT_s | InterruptVT_t |

| typedef struct mpiInterruptVT_s | mpiInterruptVT_t |

| typedef struct phyAttrb_s | phyAttrb_t |

| typedef struct sasPhyAttribute_s | sasPhyAttribute_t |

| typedef struct fwMSGUConfig_s | fwMSGUConfig_t |

| typedef void(* | EnadDisabHandler_t) (agsaRoot_t *agRoot, bit32 interruptVectorIndex) |

| typedef bit32(* | InterruptOurs_t) (agsaRoot_t *agRoot, bit32 interruptVectorIndex) |

Detailed Description

The file defines the MPI Application Programming Interface (API)

The file defines the MPI Application Programming Interfacde (API)

Definition in file spcdefs.h.

Macro Definition Documentation

◆ BC_MASK

◆ CAT_MASK

◆ FATAL_ERROR_INT_BITS

◆ GST_GPIO_PINS_OFFSET

◆ GST_GSTLEN_MPIS_OFFSET

◆ GST_INF_STATE_BITS

◆ GST_IOP1TCNT_OFFSET

◆ GST_IOPTCNT_OFFSET

◆ GST_IQ_FREEZE_STATE0_OFFSET

◆ GST_IQ_FREEZE_STATE1_OFFSET

◆ GST_MPI_STATE_ERROR

◆ GST_MPI_STATE_INIT

◆ GST_MPI_STATE_MASK

◆ GST_MPI_STATE_TERMINATION

◆ GST_MPI_STATE_UNINIT

◆ GST_MSGUTCNT_OFFSET

◆ GST_PHYSTATE0_OFFSET

◆ GST_PHYSTATE1_OFFSET

◆ GST_PHYSTATE2_OFFSET

◆ GST_PHYSTATE3_OFFSET

◆ GST_PHYSTATE4_OFFSET

◆ GST_PHYSTATE5_OFFSET

◆ GST_PHYSTATE6_OFFSET

◆ GST_PHYSTATE7_OFFSET

◆ GST_PHYSTATE_OFFSET

◆ GST_RERRINFO_OFFSET

◆ HEADER_BC_MASK

◆ HEADER_V_MASK

◆ IB_BASE_ADDR_HI_OFFSET

◆ IB_BASE_ADDR_LO_OFFSET

◆ IB_CI_BASE_ADDR_HI_OFFSET

◆ IB_CI_BASE_ADDR_LO_OFFSET

◆ IB_PIPCI_BAR

◆ IB_PIPCI_BAR_OFFSET

◆ IB_PROPERITY_OFFSET

◆ IB_QUEUE_CFGSIZE

◆ IB_RESERVED_OFFSET

◆ INT_REASRT_DELAY_BITS

◆ INT_REASRT_ENABLE

◆ INT_REASRT_MS_ENABLE

◆ INT_VT_Coal_CNT_TO

◆ INT_VT_Coal_ReAssert_Enab

◆ IOCTL_ERROR_NO_FATAL_ERROR

◆ MAIN_ANALOG_SETUP_OFFSET

| #define MAIN_ANALOG_SETUP_OFFSET 0x88 /* DWORD 0x22 (R) */ |

◆ MAIN_AWT_MIDRANGE

| #define MAIN_AWT_MIDRANGE 0xC0 /* DWORD 0x30 (W) */ /* for SPCV V 3.03 */ |

◆ MAIN_CNTRL_CAP_OFFSET

◆ MAIN_CUSTOMER_SETTING

| #define MAIN_CUSTOMER_SETTING 0x4C /* DWORD 0x13 (W) */ /* reserved for SPCV */ |

◆ MAIN_EVENT_LOG_ADDR_HI

◆ MAIN_EVENT_LOG_ADDR_LO

◆ MAIN_EVENT_LOG_BUFF_SIZE

| #define MAIN_EVENT_LOG_BUFF_SIZE 0x58 /* DWORD 0x16 (W) */ |

◆ MAIN_EVENT_LOG_OPTION

◆ MAIN_FATAL_ERROR_INTERRUPT

| #define MAIN_FATAL_ERROR_INTERRUPT 0x70 /* DWORD 0x1C (W) */ |

◆ MAIN_FATAL_ERROR_RDUMP0_LENGTH

| #define MAIN_FATAL_ERROR_RDUMP0_LENGTH 0x78 /* DWORD 0x1E (R) */ |

◆ MAIN_FATAL_ERROR_RDUMP0_OFFSET

| #define MAIN_FATAL_ERROR_RDUMP0_OFFSET 0x74 /* DWORD 0x1D (R) */ |

◆ MAIN_FATAL_ERROR_RDUMP1_LENGTH

| #define MAIN_FATAL_ERROR_RDUMP1_LENGTH 0x80 /* DWORD 0x20 (R) */ |

◆ MAIN_FATAL_ERROR_RDUMP1_OFFSET

| #define MAIN_FATAL_ERROR_RDUMP1_OFFSET 0x7C /* DWORD 0x1F (R) */ |

◆ MAIN_FW_REVISION

◆ MAIN_GST_OFFSET

◆ MAIN_HDA_FLAG_BITS

◆ MAIN_HDA_FLAGS_OFFSET

| #define MAIN_HDA_FLAGS_OFFSET 0x84 /* DWORD 0x21 (R) */ /* reserved for SPCV */ |

◆ MAIN_IBQ_OFFSET

◆ MAIN_ILAT_ILAV_ILASMRN_ILAMRN_ILAMJN

| #define MAIN_ILAT_ILAV_ILASMRN_ILAMRN_ILAMJN 0xA4 /* DWORD 0x29 (W) */ /* for SPCV */ |

◆ MAIN_INACTIVE_ILA_REVSION

| #define MAIN_INACTIVE_ILA_REVSION 0xA8 /* DWORD 0x2A (W) */ /* for SPCV V 3.02 */ |

◆ MAIN_INT_VEC_TABLE_OFFSET

| #define MAIN_INT_VEC_TABLE_OFFSET 0x8C /* DWORD 0x23 (W) */ /* for SPCV */ |

◆ MAIN_INTERFACE_REVISION

◆ MAIN_IO_ABORT_DELAY

| #define MAIN_IO_ABORT_DELAY 0x48 /* DWORD 0x12 (W) */ /* reserved for SPCV */ |

◆ MAIN_IO_ABORT_DELAY_END_TO_END_CRC_DISABLE

| #define MAIN_IO_ABORT_DELAY_END_TO_END_CRC_DISABLE 0x00010000 |

◆ MAIN_IOP_EVENT_LOG_ADDR_HI

| #define MAIN_IOP_EVENT_LOG_ADDR_HI 0x60 /* DWORD 0x18 (W) */ |

◆ MAIN_IOP_EVENT_LOG_ADDR_LO

| #define MAIN_IOP_EVENT_LOG_ADDR_LO 0x64 /* DWORD 0x19 (W) */ |

◆ MAIN_IOP_EVENT_LOG_BUFF_SIZE

| #define MAIN_IOP_EVENT_LOG_BUFF_SIZE 0x68 /* DWORD 0x1A (W) */ |

◆ MAIN_IOP_EVENT_LOG_OPTION

| #define MAIN_IOP_EVENT_LOG_OPTION 0x6C /* DWORD 0x1B (W) */ |

◆ MAIN_IQNPPD_HPPD_OFFSET

◆ MAIN_IRAD_RESERVED

| #define MAIN_IRAD_RESERVED 0x98 /* DWORD 0x26 (W) */ /* for SPCV */ |

◆ MAIN_MAX_DEV_BITS

◆ MAIN_MAX_IB_MASK

◆ MAIN_MAX_OB_MASK

◆ MAIN_MAX_OUTSTANDING_IO_OFFSET

| #define MAIN_MAX_OUTSTANDING_IO_OFFSET 0x0C /* DWORD 0x03 (R) */ |

◆ MAIN_MAX_SGL_BITS

◆ MAIN_MAX_SGL_OFFSET

◆ MAIN_MERRDCTO_MERRDCES

| #define MAIN_MERRDCTO_MERRDCES 0xA0 /* DWORD 0x28 (W) */ /* for SPCV */ |

◆ MAIN_MOQFOT_MOQFOES

| #define MAIN_MOQFOT_MOQFOES 0x9C /* DWORD 0x27 (W) */ /* for SPCV */ |

◆ MAIN_OB_HW_EVENT_PID03_OFFSET

| #define MAIN_OB_HW_EVENT_PID03_OFFSET 0x28 /* DWORD 0x0A (W) */ /* reserved for SPCV */ |

◆ MAIN_OB_HW_EVENT_PID47_OFFSET

| #define MAIN_OB_HW_EVENT_PID47_OFFSET 0x2C /* DWORD 0x0B (W) */ /* reserved for SPCV */ |

◆ MAIN_OB_NCQ_EVENT_PID03_OFFSET

| #define MAIN_OB_NCQ_EVENT_PID03_OFFSET 0x30 /* DWORD 0x0C (W) */ /* reserved for SPCV */ |

◆ MAIN_OB_NCQ_EVENT_PID47_OFFSET

| #define MAIN_OB_NCQ_EVENT_PID47_OFFSET 0x34 /* DWORD 0x0D (W) */ /* reserved for SPCV */ |

◆ MAIN_OB_SSP_EVENT_PID03_OFFSET

| #define MAIN_OB_SSP_EVENT_PID03_OFFSET 0x40 /* DWORD 0x10 (W) */ /* reserved for SPCV */ |

◆ MAIN_OB_SSP_EVENT_PID47_OFFSET

| #define MAIN_OB_SSP_EVENT_PID47_OFFSET 0x44 /* DWORD 0x11 (W) */ /* reserved for SPCV */ |

◆ MAIN_OBQ_OFFSET

◆ MAIN_PHY_ATTRIBUTE_OFFSET

| #define MAIN_PHY_ATTRIBUTE_OFFSET 0x90 /* DWORD 0x24 (W) */ /* for SPCV */ |

◆ MAIN_PHY_COUNT_MASK

◆ MAIN_PRECTD_PRESETD

| #define MAIN_PRECTD_PRESETD 0x94 /* DWORD 0x25 (W) */ /* for SPCV */ |

◆ MAIN_QSUPPORT_BITS

◆ MAIN_SAS_SUPPORT_BITS

◆ MAIN_SEEPROM_REVSION

| #define MAIN_SEEPROM_REVSION 0xAC /* DWORD 0x2B (W) */ /* for SPCV V 3.02 */ |

◆ MAIN_SIGNATURE_OFFSET

◆ MAIN_TITNX_EVENT_PID03_OFFSET

| #define MAIN_TITNX_EVENT_PID03_OFFSET 0x38 /* DWORD 0x0E (W) */ /* reserved for SPCV */ |

◆ MAIN_TITNX_EVENT_PID47_OFFSET

| #define MAIN_TITNX_EVENT_PID47_OFFSET 0x3C /* DWORD 0x0F (W) */ /* reserved for SPCV */ |

◆ MAIN_UNKNOWN1

| #define MAIN_UNKNOWN1 0xB0 /* DWORD 0x2C (W) */ /* for SPCV V 3.03 */ |

◆ MAIN_UNKNOWN2

| #define MAIN_UNKNOWN2 0xB4 /* DWORD 0x2D (W) */ /* for SPCV V 3.03 */ |

◆ MAIN_UNKNOWN3

| #define MAIN_UNKNOWN3 0xB8 /* DWORD 0x2E (W) */ /* for SPCV V 3.03 */ |

◆ MAIN_XCBI_REF_TAG_PAT

| #define MAIN_XCBI_REF_TAG_PAT 0xBC /* DWORD 0x2F (W) */ /* for SPCV V 3.03 */ |

◆ MAX_VALID_PHYS

◆ MPI_FATAL_EDUMP_HANDSHAKE_BUSY

◆ MPI_FATAL_EDUMP_HANDSHAKE_RDY

◆ MPI_FATAL_EDUMP_TABLE_ACCUM_LEN

| #define MPI_FATAL_EDUMP_TABLE_ACCUM_LEN 0x14 /* ACCDDLEN */ |

◆ MPI_FATAL_EDUMP_TABLE_HANDSHAKE

| #define MPI_FATAL_EDUMP_TABLE_HANDSHAKE 0x0C /* FDDHSHK */ |

◆ MPI_FATAL_EDUMP_TABLE_HI_OFFSET

| #define MPI_FATAL_EDUMP_TABLE_HI_OFFSET 0x04 /* HNFBUFH */ |

◆ MPI_FATAL_EDUMP_TABLE_LENGTH

◆ MPI_FATAL_EDUMP_TABLE_LO_OFFSET

| #define MPI_FATAL_EDUMP_TABLE_LO_OFFSET 0x00 /* HNFBUFL */ |

◆ MPI_FATAL_EDUMP_TABLE_STAT_DMA_FAILED

◆ MPI_FATAL_EDUMP_TABLE_STAT_NF_SUCCESS_DONE

◆ MPI_FATAL_EDUMP_TABLE_STAT_NF_SUCCESS_MORE_DATA

| #define MPI_FATAL_EDUMP_TABLE_STAT_NF_SUCCESS_MORE_DATA 0x2 |

◆ MPI_FATAL_EDUMP_TABLE_STAT_RSVD

◆ MPI_FATAL_EDUMP_TABLE_STATUS

◆ MPI_FATAL_ERROR_TABLE_OFFSET_MASK

◆ MPI_FATAL_ERROR_TABLE_SIZE

| #define MPI_FATAL_ERROR_TABLE_SIZE | ( | value | ) | ((0xFF000000 & value) >> SHIFT24) /* for SPCV */ |

◆ OB_BASE_ADDR_HI_OFFSET

◆ OB_BASE_ADDR_LO_OFFSET

◆ OB_CIPCI_BAR

◆ OB_CIPCI_BAR_OFFSET

◆ OB_DYNAMIC_COALES_OFFSET

◆ OB_INTERRUPT_COALES_OFFSET

◆ OB_PI_BASE_ADDR_HI_OFFSET

◆ OB_PI_BASE_ADDR_LO_OFFSET

◆ OB_PROPERITY_OFFSET

◆ OB_PROPERTY_INT_ENABLE

◆ OB_QUEUE_CFGSIZE

◆ OBID_MASK

◆ OPCODE_MASK

◆ PHY_EVENT_OQ

◆ PHY_STATE

◆ SPC_CONFIG

◆ SPC_MSGU_CFG_TABLE_FREEZE

| #define SPC_MSGU_CFG_TABLE_FREEZE 0x004 /* Inbound doorbell bit2 */ |

◆ SPC_MSGU_CFG_TABLE_RESET

| #define SPC_MSGU_CFG_TABLE_RESET 0x002 /* Inbound doorbell bit1 */ |

◆ SPC_MSGU_CFG_TABLE_UNFREEZE

| #define SPC_MSGU_CFG_TABLE_UNFREEZE 0x008 /* Inbound doorbell bit4 */ |

◆ SPC_MSGU_CFG_TABLE_UPDATE

| #define SPC_MSGU_CFG_TABLE_UPDATE 0x001 /* Inbound doorbell bit0 */ |

◆ SPCV_MSGU_CFG_TABLE_TRANSFER_DEBUG_INFO

| #define SPCV_MSGU_CFG_TABLE_TRANSFER_DEBUG_INFO 0x080 /* Inbound doorbell bit7 SPCV */ |

◆ SPCV_MSGU_HALT_CPUS

| #define SPCV_MSGU_HALT_CPUS 0x100 /* Inbound doorbell bit8 SPCV */ |

◆ V_BIT

◆ V_MASK

Typedef Documentation

◆ EnadDisabHandler_t

| typedef void(* EnadDisabHandler_t) (agsaRoot_t *agRoot, bit32 interruptVectorIndex) |

◆ fwMSGUConfig_t

| typedef struct fwMSGUConfig_s fwMSGUConfig_t |

◆ InterruptOurs_t

| typedef bit32(* InterruptOurs_t) (agsaRoot_t *agRoot, bit32 interruptVectorIndex) |

◆ InterruptVT_t

| typedef struct InterruptVT_s InterruptVT_t |

◆ mpiInterruptVT_t

| typedef struct mpiInterruptVT_s mpiInterruptVT_t |

◆ mpiMsgHeader_t

| typedef struct mpiMsgHeader_s mpiMsgHeader_t |

◆ phyAttrb_t

| typedef struct phyAttrb_s phyAttrb_t |

◆ sasPhyAttribute_t

| typedef struct sasPhyAttribute_s sasPhyAttribute_t |

◆ spc_configMainDescriptor_t

| typedef struct spc_configMainDescriptor_s spc_configMainDescriptor_t |

◆ spc_GSTableDescriptor_t

| typedef struct spc_GSTableDescriptor_s spc_GSTableDescriptor_t |

◆ spc_inboundQueueDescriptor_t

| typedef struct spc_inboundQueueDescriptor_s spc_inboundQueueDescriptor_t |

◆ spc_outboundQueueDescriptor_t

| typedef struct spc_outboundQueueDescriptor_s spc_outboundQueueDescriptor_t |

◆ spc_SPASTable_t

| typedef struct spc_SPASTable_s spc_SPASTable_t |